EENG4005

advertisement

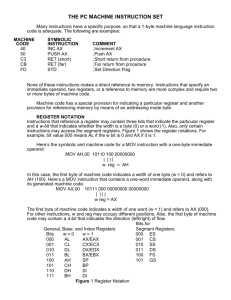

CE302 Microprocessors Lecture 2 Levent Eren Izmir University of Economics Outline • • • • Programming with registers Instruction components and format Addressing modes Sampling of addressing modes Levent Eren ce302 Programming Model Registers Note: 32 bit registers are not available on 8086, 8088, 80286 Levent Eren ce302 Programming with Registers General-Purpose Registers • AX(accumulator) often holds the temporary result after an arithmetic and logic operation (also addressed as EAX, AH, or AL) • BX (base) often holds the base (offset) address of data located in the memory (also addressed as EBX, BX, BL) • CX (count) contains the count for certain instructions such as shift count (CL) for shifts and a counter (CX or ECX) with the LOOP instruction (also addressed as ECX, CH, or CL) • DX (data) holds – the most significant part of the product after a 16- or 32-bit multiplication, – the most significant part of the dividend before a division, and – I/O port number for a variable I/O instruction (also addressed as EDX, DH, DL) Levent Eren ce302 Programming with Registers Pointer and Index Registers • SP (stack pointer) used to address data in a LIFO (last-in, firstout) stack memory, most often used when – the PUSH and POP instructions are executed – a subroutine is CALLed or RETurned within a program – Don’t ever mess with this directly • BP (base pointer) often used to address an array of data in the stack memory • SI (source index) used to address source data indirectly for use with the string instructions • DI (destination index) normally used to address destination data indirectly for use with the string instructions • IP (instruction pointer) always used to address the next instruction executed by the microprocessor Levent Eren ce302 Programming with Registers Flag Register • Flags indicate the condition of the microprocessor as well as its operation • The flag bits change after many arithmetic and logic instructions execute • Example flags, – C(carry) indicates carry after addition or a borrow after subtraction – O(overflow) is a condition that occurs when signed numbers are added or subtracted – Z(zero) indicates that the result of an arithmetic or logic operation is zero – T(trap) when the trap flag is set , it enables trapping through the onchip debugging feature Levent Eren ce302 Programming with Registers Segment Registers • CS(code) defines the starting address of the section of memoryholding code(programs and procedures used by programs) • DS(data) a section of memory that contains most data used by a program • ES(extra) an additional data segment • SS(stack) defines the area of memory used for the stack. – the location of the current entry point in the stack segment is determined by the stack pointer register. – the BP register addresses data within the stack segment • FS and GS available on 80386 and 80486 allow two additional memory segments for access by programs Levent Eren ce302 Machine Language • Machine language is the native binary code that the microprocessor understands and uses as the instructions that control its operation • Interpretation of machine’s language allows debugging or modification at the machine language level • Microprocessor requires an assembler program, which generates machine code – the machine language instructions are too complex to generate by hand • Machine language instructions for the 8086-80486, vary in length from 1 to as many as 13 bytes – there are over 20000 variations of machine language instructions Levent Eren ce302 Machine Language (cont.) • 16 -bit instruction mode – if the machine operates in the real mode the instructions for Intel family of microprocessors are 16 -bit instructions – this means that instructions use 16-bit offset address and 16-bit registers • In the protected mode the D bit in the descriptor (within a lookup table of descriptors) indicates how the 80386/80486 instructions access register and memory data in protected mode – D = 0, the 80386/80486 assumes 16 bit instructions – D = 1, the 80386/80486 assumes 32 bit instructions • the 32-bit instruction mode assumes all offset addresses are 32 bits as well as all registers Levent Eren ce302 Instruction Components and Format • s Opcode Mode Displacement Data Immediate value Instruction Components Levent Eren ce302 Addressing Modes • Register - transfers a byte or word from the source register or memory location to the destination register or memory location MOV BX, CX • Immediate - transfers an immediate byte or word of data into the destination register or memory location MOV AX, 3456h • Direct - moves a byte or word between a memory location and a register MOV AL, [1234h] (1234h is treated as a displacement within data segment) Levent Eren ce302 Addressing Modes(cont.) • Register Indirect (base relative or indexed) - transfers a byte or word of data between a register and the memory location addressed by an index (DI or SI) or base register (BP or BX) MOV AX, [BX] • Base Plus Index (base relative indexed) - transfers a byte or word of data between a register and the memory location addressed by a base register (BP or BX) plus index (DI or SI) register MOV DX, [BX + DI] Levent Eren ce302 Addressing Modes(cont.) • Register Relative - transfers a byte or word of data between a register and the memory location addressed by an index (DI or SI) or base register (BP or BX) plus displacement MOV AX, [BX + 1000h] • Base Relative Plus Index (base relative indexed) - transfers a byte or word of data between a register and the memory location addressed by a base register (BP or BX) plus an index register (DI or SI) MOV AX, [BX + SI + 100h] Levent Eren ce302 Instruction Components Instructions have four components that specify the operation to execute, and how to treat the associated data. D W MOD OPCODE Levent Eren ce302 REG R/M Instruction Components OPCODE • Opcode (one or two bytes) selects the operation (e.g., addition, subtraction, move) performed by the microprocessor D W D - direction of the data flow D = 0 data flow to R/M field from register field D = 1 data flow to the register field from R/M in the next byte of the instruction OPCODE W - data size W = 0 data size is a byte W = 1 data size is a word/double word Levent Eren ce302 Instruction Components MOD • MOD field specifies the addressing mode for the selected instruction and whether the displacement is present with the specified addressing mode MOD MOD REG R/M 00 01 10 11 FUNCTION no displacement 8-bit sign-extended displacement 16-bit displacement R/M is a register (register addressing mode) • If the MOD filed contains a 00, 01, or 10, the R/M field selects one of the data memory-addressing modes, e.g., – MOV – MOV Levent Eren AL, [DI] (no displacement) AL, [DI + 2] (8-bit displacement) ce302 Instruction Components REG & R/M in Register Assignment Register assignment for the REG and R/M fields Code W = 0 (Byte) W = 1(Word) W =1 (Double Word) 000 001 010 011 100 101 110 111 AL CL DL BL AH CH DH BH AX CX DX BX SP BP SI DI EAX ECX EDX EBX ESP EBP ESI EDI Levent Eren ce302 Register Assignment Example • Consider 2 byte instruction 8BECh in the machine language program (assuming 16-bit instruction mode) binary representation: 1000 1011 1110 1100, from this we have opcode: D=W 100010 1 => => MOD REG R/M 11 101 100 => => => MOV a word moves into the register specified in the REG field R/M field also indicates register indicates register BP indicates register SP consequently the instruction is: MOV BP, SP Levent Eren ce302 Use of R/M Filed in Determining Addressing Mode • If the MOD field contains a 00, 01, or 10, the R/M field takes on a new meaning Code Function • Examples: 1. if MOD = 00 and R/M = 101 the addressing mode is [DI] 2. if MOD = 01 or 10 and R/M = 101 the addressing mode is [DI + 33h] or LIST[DI + 22H], where 33h, LIST, 22h are arbitrary values for displacement Levent Eren ce302 000 001 010 011 100 101 110 111 DS:[BX+SI] DS:[BX+DI] SS:[BP+SI] SS:[BP+DI] DS:[SI] DS:[DI] SS:[BP] DS:[BX] Base plus Index Register indirect Example • Consider machine language instruction 8A15h binary representation is: 1000 1010 0001 0101 opcode: D 100010 1 => => W MOD REG R/M 0 00 010 101 => => => => the instruction is: MOV DL, [DI] Levent Eren ce302 MOV a word moves into the register specified in the REG field byte no displacement indicates register DL indicates addressing mode [DI] Direct Addressing Mode • Direct Addressing mode (for 16-bit instructions) occurs whenever memory data are referenced by only the displacement mode of addressing, e.g., MOV [1000h], DL moves the contents of DL into data segment memory location 1000h MOV NUMB, DL moves the contents of DL into symbolic data segment memory location NUMB OPCODE D W 1 0 0 0 1 0 0 0 Byte 1 Displacement-low 0 0 0 0 0 0 0 0 Byte 3 Levent Eren MOD REG R/M 0 0 0 1 0 1 1 0 Byte 2 MOV [1000h], DL Whenever the instruction has only a displacement: Displacement-high 0 0 0 1 0 0 0 0 Byte 4 ce302 MOD R/M is always 00 is always 110 Immediate Instruction • Consider an instruction: MOV word PTR[BX + 1000h], 1234h OPCODE W 1 1 0 0 0 1 1 1 Byte 1 Displacement-low 0 0 0 0 0 0 0 0 Byte 3 Data-low 0 0 1 1 0 1 0 0 Byte 5 Levent Eren MOD R/M Moves 1234h into the word-sized memory location addressed by the sum of 1000h, BX, and DS x 10h 1 0 0 0 0 1 1 1 Byte 2 Displacement-high 0 0 0 1 0 0 0 0 WORD PTR directive indicates to the assembler that the instruction uses a word-sized memory pointer (if the instruction moves a byte of immediate data, then BYTE PTR directive is used. Byte 4 Data-high 0 0 0 1 0 0 1 0 Byte 6 ce302 The above directive are only needed when it is not clear if the operation is a byte or a word, e.g., MOV [BX], AL clear a byte move MOV [BX], 1 not clear, can be byte-, word, or double word-sized move should be for instance MOV BYTE PTR [BX], 1 Segment MOV Instructions • The contents of a segment register are moved by MOV, PUSH, POP • Segment registers are selected by appropriate setting of register bits (REG field) Code 000 001 010 011 100 101 ES CS SS DS FS GS Note: MOV CS, ?? and POP CS are not allowed Levent Eren Example: MOV BX, CS Segment Register OPCODE 1 0 0 0 1 1 0 0 REG is 001 R/M is 011 MOD REG R/M 1 1 0 0 1 0 1 1 => selects CS => selects BX Note that the opcode for this instruction is different for the prior MOV instructions ce302 Sampling of Addressing Modes Levent Eren ce302 Sampling of Addressing Modes Levent Eren ce302 Sampling of Addressing Modes Levent Eren ce302