Xilinx Guidelines for Presentation Template

advertisement

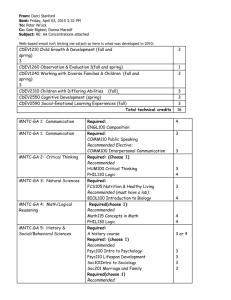

EDK Introduction This material exempt per Department of Commerce license exception TSU Objectives After completing this module, you will be able to: • • • • • Describe the embedded systems development flow Understand the components in the hardware design Specify ways to create a hardware design Identify the tools included in EDK Locate the EDK documentation EDK Intro 2 Outline • Introduction • EDK – Overview of EDK – Embedded Development Design Flow – XPS Platform Management • Supported Platforms • Appendix: Project Files and Structures EDK Intro 3 Embedded Systems • An embedded system is nearly any computing system (other than a general-purpose computer) with the following characteristics – Single-functioned • Typically, is designed to perform predefined function – Tightly constrained • • • • Tuned for low cost Single-to-fewer components based Performs functions fast enough Consumes minimum power – Reactive and real-time • Must continually monitor the desired environment and react to changes – Hardware and software co-existence EDK Intro 4 Embedded Systems • Examples: – Mobile phone systems • Customer handsets and base stations – Communication devices • Wired and wireless routers and switches – Automotive applications • Braking systems, traction control, airbag release systems, and cruisecontrol applications – Aerospace applications • Flight-control systems, engine controllers, auto-pilots and passenger inflight entertainment systems – Defense systems • Radar systems, fighter aircraft flight-control systems, radio systems, and missile guidance systems EDK Intro 5 Current Technologies • • • • Microcontroller-based systems DSP processor-based systems ASIC technology FPGA technology EDK Intro 6 Integration in System Design Integration of Functions Embedded Software Tools CPU CPU Embedded Software Tools Embedded Software Tools FPGA I/O FPGA + Memory + IP + High Speed IO (4K & Virtex) Logic Design Tools Memory Logic Design Tools Time EDK Intro 7 Logic + Memory + IP + Processors + RocketIO (Virtex-II Pro) Logic Design Tools Programmable Systems usher in a new era of system design integration possibilities Embedded Design in an FPGA • Embedded design in an FPGA consists of the following: – FPGA hardware design – C drivers for hardware – Software design • Software routines • Interrupt service routines (optional) • Real Time Operating System (RTOS) (optional) PowerPC-based Embedded Design RocketIO Dedicated Hard IP DSOCM BRAM PowerPC 405 Core Instruction Arbiter OPB Processor Local Bus e.g. Memory Controller ZBT SRAM EDK Intro 9 GB E-Net DDR SDRAM IBM CoreConnect™ on-chip bus standard PLB, OPB, and DCR Bus On-Chip Peripheral Bus Bridge UART SDRAM GPIO Arbiter Off-Chip Memory Flexible Soft IP DCR Bus Data PLB Hi-Speed Peripheral ISOCM BRAM On-Chip Peripheral Full system customization to meet performance, functionality, and cost goals MicroBlaze Processor-Based Embedded Design BRAM Local Memory MicroBlaze Bus 32-Bit RISC Core I-Cache BRAM D-Cache BRAM Flexible Soft IP Configurable Sizes Possible in Dedicated Hard IP PowerPC Virtex-II Pro 405 Core Custom Functions SRAM Bus Processor Local Bus Bridge Hi-Speed Peripheral UART 10/100 E-Net Data PLB On-Chip Peripheral Bus Custom Functions CacheLink EDK Intro 10 OPB e.g. Memory Controller Memory Controller Off-Chip FLASH/SRAM Memory GB E-Net Arbiter Arbiter Fast Simplex Link 0,1….7 Instruction Outline • Introduction • EDK – Overview of EDK – Embedded Development Design Flow – XPS Platform Management Hardware Design • Supported Platforms • Appendix: Project Files and Structures EDK Intro 11 Embedded Development Kit • What is Embedded Development Kit (EDK)? – The Embedded Development Kit is the Xilinx software suite for designing complete embedded programmable systems – The kit includes all the tools, documentation, and IP that you require for designing systems with embedded IBM PowerPC™ hard processor cores, and/or Xilinx MicroBlaze™ soft processor cores – It enables the integration of both hardware and software components of an embedded system EDK Intro 12 Embedded Development Tool Flow Overview VHDL or Verilog C Code Standard Embedded SW Development Flow Code Entry Include the BSP C/C++ Cross Compiler and Compile the Software LinkerImage ? 2 Load Software Into FLASH Embedded Development Kit HDL Entry Board Support Package System Netlist Data2MEM Compiled ELF 3 Compiled BIT Download Combined Image to FPGA Debugger Instantiate the Simulation/Synthesis ‘System Netlist’ and Implement Implementation the FPGA 1 ? Download Bitstream Into FPGA Chipscope RTOS, Board Support Package EDK Intro 13 Standard FPGA HW Development Flow Embedded System Tools • GNU software development tools – C/C++ compiler for the MicroBlaze™ and PowerPC™ processors (gcc) – Debugger for the MicroBlaze and PowerPC processors (gdb) • Hardware and software development tools – – – – – – – – – – – Base System Builder Wizard Hardware netlist generation tool: PlatGen Software Library generation tool: LibGen Simulation model generation tool: SimGen Create/Import Peripherals Wizard Xilinx Microprocessor Debug (XMD) Hardware debugging using ChipScope™ Pro Analyzer cores Eclipse IDE-based Software Development Kit (SDK) Application code profiling tools Virtual Platform generator: VPGen Flash Writer utility EDK Intro 14 Embedded System Tools • Board Support Packages (BSPs) – – – – • Standalone BSP Wind River VxWorks MontaVista Linux Xilinx MicroKernel (XMK) Xilinx Platform Studio – Xilinx Platform Studio (XPS) is a graphical Integrated Design Environment (IDE) that incorporates all the Embedded System Tools for seamless creation of hardware and software components and, optionally, a verification component EDK Intro 15 Xilinx Platform Studio (XPS) See notes section for detailed explanation EDK Intro 16 XPS Functions • Project management • Platform management – MHS or MSS file – XMP file – – – – • Software application management Tool flow settings Software platform settings Tool invocation Debug and simulation HW/SW Simulation Hardware Design XPS Software Design HW/SW Debug Outline • Introduction • EDK – Overview of EDK – Embedded Development Design Flow – XPS Platform Management • Supported Platforms • Appendix: Project Files and Structures EDK Intro 18 Project Management • Create a new project – Using File New Project or toolbar button • Select Base System Builder option – The Base System Builder (BSB) wizard is a software tool that helps you quickly build a working system targeted at a specific development board • Select Blank XPS Project option • Open an existing project – Using File Open Project or toolbar button • Browse to a pre-created project directory and selecting an xmp file – Using File New Project or toolbar button • Select Open a Recent Project option and selecting a project • Project information is saved in the Xilinx Microprocessor Project (XMP) file Project Creation Using Base System Builder (BSB) Option • • • • • • • Select a target board Select a processor Configure the processor Select and configure I/O interfaces Add internal peripherals Generate the system software and the linker script Generate the design – Generated files: • • • • system.mhs System.xmp etc/fast_runtime.opt pcore directory (empty) system.mss data/system.ucf etc/download.cmd system.bsb (optional, if selected) – TestApp_Memory/src directory containing (optional, if selected) • TestApp_Memory.c TestApp_Memory_LinkScr.ld – TestApp_Peripheral/src directory containing (optional, if selected) • TestApp_Peripheral EDK Intro 20 TestApp_Peripheral/src/TestApp_Periperal_LinkScr.ld EDK Tool Flow Library Generation MSS MHS Hardware Platform Generation CompEDKLib CompXLib IP Models ISE Models Testbench Stimulus IP Library or User Repository EDK SW Libraries LibGen .a Drivers, MDD SimGen MPD, PAO PCore HDL System and Wrapper VHD Synthesis (XST) Embedded Software Development Application Source .c, .h, .s PlatGen system.BMM Behavioral VHD Model ISE Tools NGC UCF NGDBuild SimGen NGD Compiler (GCC) MAP Structural VHD Model .o NCD, PCF Linker (GCC) PAR NCD ELF system.BIT BitGen BitInit system_BD.BMM SimGen Timing VHD Model download.BIT download.CMD EDK Intro 21 iMPACT Simulation Simulation Generator Hardware Implementation XPS/Xflow • Xflow – Implement hardware and generate the bitstream – Input files → .ngc netlists, .bmm file, system.vhd, .ucf – Output Files → system.bit, system_bd.bmm – Xflow calls the ISE™ Implementation tools using fast_runtime.opt file • NGDBuild, MAP, PAR, and TRACE are executed – Xflow then calls the BitGen program using bitgen.ut file • BitGen generates the bit file system.bit • BitGen also generates the back-annotated system_bd.bmm BMM file, which contains the physical location of the block RAMs EDK Intro 22 Hardware Implementation ISE/XPS Flow • The ISE/XPS flow provides integration of a processor system at two levels as a component in a FPGA design : – The processor system is the top-level design – The processor system is a submodule • Once the processor system is added in the ISE project, XPS can be invoked from ISE by selecting xmp file in Sources window and double-clicking Manage Processor System in the Processes window • Add user constraint file in ISE • Implement design in ISE by selecting top-level module in Sources window and double-clicking Implement Design in Processes window • Executable software can be merged by selecting top-level module in Sources window and double-clicking Update Bitstream with Processor Data in Processes window – This will call XPS in background to update the bitstream and generate system.bit and download.bit files in implementation directory as well as copy the file as system_stub.bit and system_stub_download.bit files in the ISE project directory EDK Intro 23 Software Flow Library Generation • Library Generator – LibGen – Input files → MSS – Output files → libc.a, libXil.a, libm.a – LibGen is generally the first tool run to configure libraries and device drivers • The MSS file defines the drivers associated with peripherals, standard input/output devices, interrupt handler routines, and other related software features – LibGen configures libraries and drivers with this information and produces an archive of object files: • libc.a - Standard C library • libXil.a - Xilinx library • libm.a - Math functions library EDK Intro 24 Software Flow Compilation • Compile program sources – Input files → *.c, *.c++, *.h, libc.a, libXil.a, libm.a – Output files → executable.elf – This invokes the compiler for each software application and builds the executable files for each processor – Four stages: • Pre-processor: Replaces all macros with definitions as defined in the .c or .h files • Machine-specific and language-specific compiler: Compiles C/C++ code • Assembler: Converts code to machine language and generates the object file • Linker: Links all the object files using user-defined or default linker script EDK Intro 25 Merging Hardware and Software Flows Hardware Flow Software Flow data2MEM download.bit GPIO MicroBlaze™/ PPC Arbiter UART EDK Intro 26 Merging Hardware and Software Flows • Data2MEM – Update the bitstream – Input files → system_bd.bmm, system.bit, executable.elf – Output file → download.bit – This invokes the BitInit tool, which initializes the instruction memory of the processor – The instruction memory may be initialized with a bootloop, bootloader, or an actual application – This is the stage where the hardware and the software flows come together. This stage also calls the hardware and software flow tools if required EDK Intro 27 Configuring the FPGA • Download the bitstream – Input file → download.bit – This downloads the download.bit file onto the target board using the Xilinx iMPACT tool in batch mode – XPS uses the etc/download.cmd file for downloading the bitstream • The download.cmd file contains information such as the type of cable is used and the position of the FPGA in a JTAG chain EDK Intro 28 Outline • Introduction • EDK – Overview of EDK – Embedded Development Design Flow – XPS Platform Management • Supported Platforms • Appendix: Project Files and Structures EDK Intro 29 Add/Edit Cores • Add cores, edit core parameters, and make bus and port connections through System Assembly view 1– Select IP Catalog tab to add peripherals 3 • Select a core and drop it in the system view or doubleclick on it to add 2– In the System View select an instance, right click, and then select Delete Instance 3– Change settings using appropriate filters and select an instance • Base and end addresses • Parameters • Ports 1 2 Project Options Device and Repository Tab • Set/Change Target Device – – – – Architecture Device Size Package Grade • Peripheral Repository Directory – Provide path to custom IP not present in the current project directory structure • Custom Makefile Directory Note: Detailed information on the other two tabs is provided in the “Adding Your Own IP to the OPB Bus” and the “System Simulation” modules in this course. Outline • Introduction • EDK – Project Management – Software Application Management – Platform Management • Supported Platforms • Appendix: Project Files and Structures EDK Intro 32 Supported Platforms • Operating systems – – – – Windows 2000 (Service Pack 2) Windows XP Solaris Operating System 2.8/2.9 Linux Red Hat Enterprise 3.0 • FPGA families – – – – – – Spartan™-II/IIE (MicroBlaze™ processor) Spartan-3/3E (MicroBlaze processor) Virtex™ and Virtex-E (MicroBlaze processor) Virtex-II (MicroBlaze processor) Virtex-II Pro (MicroBlaze and PowerPC™ processors) Virtex-4 FX (MicroBlaze and PowerPC processors) and LX/SX (MicroBlaze processor) EDK Intro 33 BSB-Supported Platforms • A list of supported Xilinx hardware boards: – – – – – – – – – – AFX board Spartan-3 Starter Board Virtex-4 ML401 Evaluation Platform Virtex-4 ML402 Evaluation Platform Virtex-4 ML403 Evaluation Platform Virtex-II Multimedia FF896 Development Board Virtex-II Pro ML300 Evaluation Platform Virtex-II Pro ML310 Evaluation Platform XUP Virtex-2 Pro Educational Platform (.xbd files downloadable from XUP web) Custom board • Board definition (.xbd) files for third party boards can be downloaded from the board vendor web site – Links from the BSB wizard and Xilinx embedded Web page EDK Intro 34 Knowledge Check • What is the MHS file? • What does the PlatGen tool do? • What tool is used to place executable code in an FPGA block RAM? EDK Intro 35 Answers • What is the MHS file? – The MHS file is the Microprocessor Hardware Specification; it specifies processors, hardware peripherals, bus connections, and address spaces for the hardware • What does the PlatGen tool do? – PlatGen takes the MHS file and creates the system and peripheral netlists, HDL wrapper files, BMM file, etc. • What tool is used to place executable code in an FPGA block RAM? – The Data2Mem tool will take the BMM file and create the proper initialization for the block RAM that is assigned to the executable memory space EDK Intro 36 Knowledge Check • How can you add or change configuration settings once the hardware system is build? • What does the LibGen tool do? • What is the difference between system.bit and download.bit files? EDK Intro 37 Answers • How can you add or change configuration settings once the hardware system is build? – Select IP Catalog tab, expand related IP peripheral folder, select a desired IP, and double-click on it to add it to the design – Select an IP instance in the System Assembly View panel, right click on it, and select desired configuration • What does the LibGen tool do? – Read MSS file and generate libraries • What is the difference between system.bit and download.bit files? – The system.bit file contains only hardware description whereas download.bit file contains both hardware description as well as executable software EDK Intro 38