EE 414 - nau.edu

advertisement

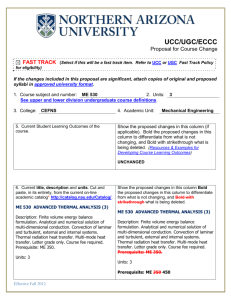

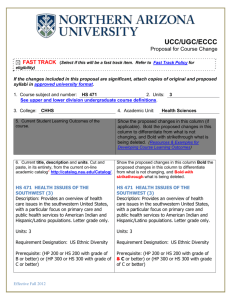

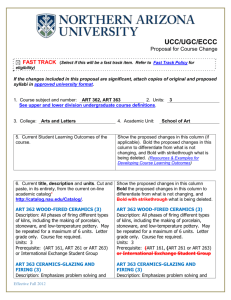

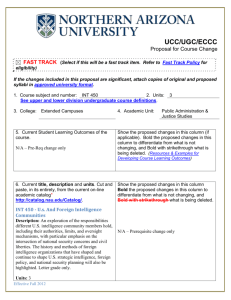

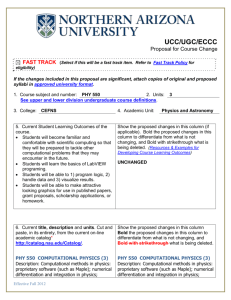

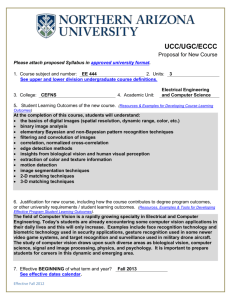

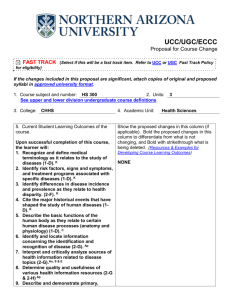

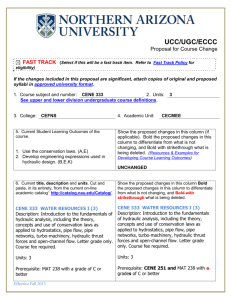

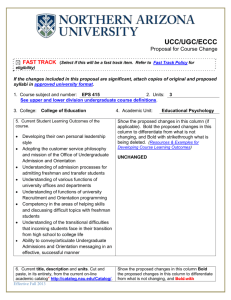

UCC/UGC/ECCC Proposal for Course Change FAST TRACK (Select if this will be a fast track item. Refer to UCC or UGC Fast Track Policy for eligibility) If the changes included in this proposal are significant, attach copies of original and proposed syllabi in approved university format. 1. Course subject and number: EE 414 2. Units: See upper and lower division undergraduate course definitions. 3. College: CEFNS 5. Current Student Learning Outcomes of the course. At the completion of this course, students will understand: 4. Academic Unit: 3 Electrical Engineering and Computer Science Show the proposed changes in this column (if applicable). Bold the proposed changes in this column to differentiate from what is not changing, and Bold with strikethrough what is being deleted. (Resources & Examples for Developing Course Learning Outcomes) the definition of computer architecture the major components of modern computer architecture the functionality and trade-offs of several cache memory designs the instruction pipeline a variety of memory technologies several key algorithms behind computer arithmetic the differences between RISC, CISC, and Superscalar architectures parallelism in terms of both single and multiple processors the issues and trade-offs involved in instruction set design UNCHANGED the unique architectures of graphics processors and digital signal processors 6. Current title, description and units. Cut and paste, in its entirety, from the current on-line Effective Fall 2012 Show the proposed changes in this column Bold the proposed changes in this column to academic catalog* http://catalog.nau.edu/Catalog/. differentiate from what is not changing, and Bold with strikethrough what is being deleted. EE 414 COMPUTER ARCHITECTURE (3) EE 414 COMPUTER ARCHITECTURE (3) Description: Architecture taxonomies and building blocks. Examples of system architectures, instruction sets, processors, I/O, memories, and computer busses. Introduces fault tolerance and parallel computing. Letter grade only. Course fee required. Description: Architecture taxonomies and building blocks. Examples of system architectures, instruction sets, processors, I/O, memories, and computer busses. Introduces fault tolerance and parallel computing. Letter grade only. Co convenes with EE 514. Course fee required. Units: 3 Prerequisite: EE 310 with grade of C or better Units: 3 Prerequisite: EE 310 215 with grade of C or better *if there has been a previously approved UCC/UGC/ECCC change since the last catalog year, please copy the approved text from the proposal form into this field. 7. Justification for course change. This proposal is to co-convene with the new EE 514, and change prerequisite. The former prerequisite of EE 310 is not necessary because the Computer Architecture material does not require a significant background in microelectronics nor in field-programmable gate array (FPGA) implementation as developed in EE 310. EE 414 and 514 do require a good background in the basics of microprocessors and their functioning, which are well covered by EE 215. 8. Effective BEGINNING of what term and year? Fall 2013 See effective dates calendar. IN THE FOLLOWING SECTION, COMPLETE ONLY WHAT IS CHANGING CURRENT Current course subject and number: PROPOSED Proposed course subject and number: Current number of units: Proposed number of units: Current short course title: Proposed short course title (max 30 characters): Current long course title: Proposed long course title (max 100 characters): Current grading option: letter grade pass/fail or both Proposed grading option: letter grade pass/fail or both Current repeat for additional units: Proposed repeat for additional units: Current max number of units: Proposed max number of units: Current prerequisite: Effective Fall 2012 Proposed prerequisite (include rationale in the EE 310 with grade of C or better justification): EE 215 with grade of C or better Current co-requisite: Proposed co-requisite (include rationale in the justification): Current co-convene with: Proposed co-convene with: NONE EE 514 Current cross list with: Proposed cross list with: 9. Is this course in any plan (major, minor, or certificate) or sub plan (emphasis)? Yes No If yes, describe the impact and include a letter of response from each impacted academic unit. 10. Is there a related plan or sub plan change proposal being submitted? If no, explain. Yes 11. Does this course include combined lecture and lab components? Yes If yes, include the units specific to each component in the course description above. No No Answer 12-15 for UCC/ECCC only: 12. Is this course an approved Liberal Studies or Diversity course? If yes, select all that apply. Liberal Studies Diversity Both Yes No 13. Do you want to remove the Liberal Studies or Diversity designation? If yes, select all that apply. Liberal Studies Diversity Both Yes No 14. Is this course listed in the Course Equivalency Guide? Yes No 15. Is this course a Shared Unique Numbering (SUN) course? Yes No FLAGSTAFF MOUNTAIN CAMPUS Scott Galland Reviewed by Curriculum Process Associate Effective Fall 2012 02/15/2013 Date Approvals: 2/14/2013 Department Chair/Unit Head (if appropriate) Date Chair of college curriculum committee Date Dean of college Date For Committee use only: UCC/UGC Approval Date Approved as submitted: Yes No Approved as modified: Yes No EXTENDED CAMPUSES Reviewed by Curriculum Process Associate Date Approvals: Academic Unit Head Date Division Curriculum Committee (Yuma, Yavapai, or Personal Learning) Date Division Administrator in Extended Campuses (Yuma, Yavapai, or Personal Learning) Date Faculty Chair of Extended Campuses Curriculum Committee (Yuma, Yavapai, or Personal Learning) Date Chief Academic Officer; Extended Offices (or Designee) Date Approved as submitted: Yes No Approved as modified: Yes No Effective Fall 2012 Department of Electrical Engineering & Computer Science COURSE SYLLABUS: EE 414 COMPUTER ARCHITECTURE General Information: Sequence number: Class times: 3.0 credit hours. There is no laboratory component to this course. Instructor: Dr. Phillip Mlsna, Associate Professor of Electrical Engineering Office: Engineering room 257, 523-2112, phillip.mlsna@nau.edu Office hours as posted (office door and BlackboardLearn) Official course webpages are on BlackboardLearn: http://bblearn.nau.edu Course Prerequisite: EE 215 with grade C or better Course Description (from catalog) : Architecture taxonomies and building blocks. Examples of system architectures, instruction sets, processors, I/O, memories, and computer busses. Introduces fault tolerance and parallel computing. Letter grade only. This course is available as a technical elective for undergraduate Electrical Engineering and Computer Science students. Student Learning Expectations/Outcomes for this Course : At the completion of this course, students will understand: the definition of computer architecture the major components of modern computer architecture the functionality and trade-offs of several cache memory designs the instruction pipeline a variety of memory technologies several key algorithms behind computer arithmetic the differences between RISC, CISC, and Superscalar architectures parallelism in terms of both single and multiple processors the issues and trade-offs involved in instruction set design the unique architectures of graphics processors and digital signal processors Course Structure/Approach: We will be following the textbook rather closely most of the time, with the topic order as shown in the “Course Outline” section below. The format will largely be lecture and discussion. The textbook readings are especially important. There will often be important material in the text that we will not have time to cover in class. Effective Fall 2012 Required Textbook: Hennessy and Patterson, “Computer Architecture: A Quantitative Approach”, 5th edition, 2012, Morgan Kaufmann, ISBN 978-0-12-383872-8. The publisher is providing several supplementary appendices in pdf form, which will be posted on BlackboardLearn. Earlier editions of the textbook are not adequate substitutes for this 5th edition. Recommended optional materials/references: Parhami, “Computer Arithmetic: Algorithms and Hardware Designs”, 2nd edition, 2010, Oxford University Press, ISBN 978-0-19-532848-6. Parhami, “Computer Architecture: From Microprocessors to Supercomputers”, 2005, Oxford University Press, ISBN-13: 978-0-19-515455-9. Course Outline: Weeks 1-2 Weeks 3-4 Weeks 5-6 Weeks 7-8 Weeks 9-10 Weeks 11-12 Week 13 Weeks 14-15 Fundamentals Memory Hierarchy Instruction Set Architecture Computer Arithmetic Instruction-Level Parallelism Data-Level Parallelism Thread-Level Parallelism Specialized Architectures Chapter 1 Chapter 2, Appendices B & D Appendices A & K Appendix J, supplemental source Chapter 3, Appendices C & H Chapters 4 & 6, Appendix G Chapter 5, Appendices F & I Appendix E Assessment of Student Learning Outcomes: Assessment will be based on two mid-term exams, homework, a term paper, participation, and a comprehensive final exam. Grading System and Assessment Timing: Exam 1 100 points Exam 2 100 points Final exam 150 points Homework 100 points Term Paper 50 points Participation 25 points Total 525 points approximately week 6 approximately week 11 Wed, Dec. 12, 10:00-noon approximately once per week attendance and active classroom participation Course Policies: Late Work Assignments are due when specified and can be submitted on BBLearn (preferred) or on paper at the beginning of the class period. Late work will be accepted electronically only (on BBLearn, not by e-mailing the professor!) up to 24 hours late for a 20% penalty, and not accepted after 24 hours late. Retests and Makeup Tests No makeup exams will be given except by prior arrangement in exceptional or emergency situations at the discretion of the instructor. Please contact me immediately if such a situation arises. (Procrastination is not an emergency.) Attendance Attendance is required and will be recorded on a random basis. Attendance data will be included in the participation portion of your grade. Academic Dishonesty Effective Fall 2012 Cheating and plagiarism are strictly prohibited. Incidents of cheating or plagiarism are treated quite seriously. The NAU policy on academic dishonesty in Appendix G of the current Student Handbook applies. All work you submit for grading must be your own. http://home.nau.edu/studentlife/handbook/appendix_g.asp You are encouraged to discuss the intellectual aspects of homework assignments with other class participants. However, each student is responsible for formulating solutions in his or her own words. I strongly discourage you from blindly copying from the webbased supposed “answers” for the Hennessy and Patterson text exercises. Most such “answers” are terse. Many of them are actually wrong. If you do not work hard to solve the homework, you will not learn the technology well enough to pass the exams, especially the final exam. University policies: Safe Working and Learning Environment Students with Disabilities Institutional Review Board Academic Integrity Academic Contact Hour Sensitive Course Material See the following document for these policy statements: http://www4.nau.edu/avpaa/UCCPolicy/plcystmt.html. Effective Fall 2012