COEN 4710

advertisement

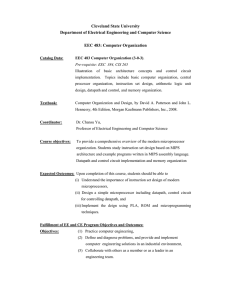

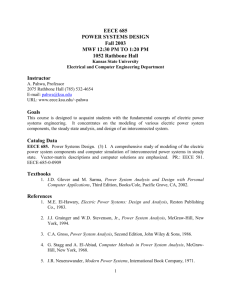

COEN 4710 (COEN 171): Computer Hardware Credits/contact hours: 3 Course Coordinator: Mike Johnson Text Book: Computer Organization and Design: The Hardware/Software Interface, 3rd Ed., David A. Patterson and John L. Hennessy, Morgan Kaufmann, 2005. Course Information: Overview of computer system design. Cost and performance specification. Design of arithmetic and logic units. Fundamentals of central processor architecture and a comparative study of computer instruction set architectures. Detailed study of microprocessors, including instruction execution timing and other timing considerations. Discussions of memory and I/O devices, including the interfaces to the CPU and I/O transfer techniques. Study of common bus standards. Design elective for Electrical and Electronics major. Prerequisites: EECE 2710 (COEN 030) with minimum grade of C and EECE 2030 (112) with minimum grade of C; or COSC 2200 (065) with minimum grade of C and EECE 2030 (112) with minimum grade of C . Required course in the Computer Engineering program as well as in the Electrical and Computer Engineering major within the Electrical Engineering program and for the Biocomputing major in the Biomedical Engineering program. Contribution to Professional Component: Engineering Science 33 % / Engineering Design 67 % Course Goals: To present students with a detailed understanding of the design problems and their solutions for modern computer hardware at and above the circuit block diagram level. Course Objectives: By the end of this course, you should.... 1. Be able to implement small to moderate-sized software applications using a modern assembly language (such as MIPS) 2. Be able to design combinatorial and sequential hardware to perform basic arithmetic calculations, and be able to critique various design alternatives. 3. Be able to use several different quantitative performance measures for comparing hardware designs, and be able to identify the advantages and disadvantages of each. 4. Be able to design and implement a single-cycle or multi-cycle datapath and its control signals, and be able to assess design methodologies and alternatives. 5. Be able to design a basic pipelined datapath and its control signals at the circuit block diagram level, and to address issues with structural, data, or branching hazards at either the hardware or software level. 6. Be able to design multiplication and division algorithms for integer or floating point numbers, using IEEE standard representation. Be able to interface memories at different levels of a memory hierarchy, and be able to do a performance analysis of a hierarchical memory system. 8. Be able to interface I/O devices using standard bus protocols, and be able to do a performance analysis of an I/O system based on the speed and bandwidths of the system components. 7. Contribution to Student Outcomes: I, J, K partial fulfillment of Criterion 3 objectives A, C, E, G, H, Course Topics: 1. 2. 3. 4. 5. 6. 7. 8. Introduction to Computer Architecture Instruction Sets Data and Arithmetic Performance Measures Processor Datapath and Control Pipelined Datapath and Control Memory Hierarchy Interfacing In the Patterson and Hennessy Text Chapter 1 Chapter 2 Chapter 3 Chapter 4 Chapter 5 Chapter 6 Chapter 7 Chapter 8