Technologies Pvt Ltd Foreview # 13, 2nd Floor, Rajagopal

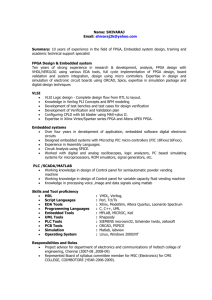

advertisement

Foreview Technologies Pvt Ltd VLSI # 13, 2nd Floor, Rajagopal Mudhaliyar Street, Opp national theatre, West Tambaram, Chennai-45 Mobile: 9043033334 & 8680002222 Office: 044-42602321 foreview.vlsi@gmail.com 1. 2. 3. 4. 5. 6. Design Of Milk Analysis Embedded System For Dairy Farmers using FPGA Mobile Avoidance For Safe Driving using Field Programmable Gate Array Advanced Rescue system for industrial monitoring using Zigbee, GSM and FPGA FPGA and RF based Real time implementation Of advanced Toll Gate system Advanced Terminal Founding And New Passport Security System Using Passive RF Control For Carbon Monoxide Leakage,Multi-sensor tracking and lane estimation in highly automated vehicles 7. Anti-Theft and smart Car control system Using Multi Media Service 8. Distance Analysis Of ATM And Cyber Security in Financial Sector Using FPGA Implementation 9. Solid Waste Management control system through zigbee And FPGA 10. Multi-Function System Through Hand Fly Signal And Control Of FPGA 11. Water Storage and Distribution System for Pharmaceuticals using FPGA and SCADA 12. Human Health Monitoring mobile Phone Application By Using The wireless nano sensor based System 13. Passenger Alert System And Advanced Control Over Existing System Using MMS 14. Wireless sensing and control for precision Green house management 15. Hardware‐efficient path planning for a mobile robot and FPGA realization 16. RFID based Navigation System for Unmanned Material Handling Vehicles using FPGA 17. Tracking System, Preventing Trees Extinction and Deforestation Using RF and FPGA 18. A Zigbee SMS Alert System With Trust Mechanism In Wireless Sensor Networks 19. Indoor Localization System based on Fingerprint Technique using RFID Passive Tag 20. A Directional-Edge-Based Real-Time Object Tracking System Employing Multiple Candidate-Location Generation 21. Building Control, Monitoring, Safety and Security using Collaborative Systems 22. Extended Wireless Monitoring through Intelligent Hybrid Energy Supply 23. Passenger BUS Alert System for Easy Navigation of Blind 24. Wireless Technologies for Distributed Sensor Networks Used in Measurement and Automation Systems 25. Migration From Legacy Wireless Technology to Zigbee For Home Automation 26. FPGA Based Tracking System For Railways Transportation 27. Tourist Management, Monitoring and Control System using Wireless Communication. 28. FPGA-based Modern Sailing Robot 29. RFID Library Management System and Control through Alert Signal. 30. Realization of Intelligent Traffic Light Monitor and Control System Based on Wireless Control 31. Authentication and Authorization Technique For Smart Card System EMBEDDED SYSTEMS I POWER ELECTRONICS I JAVA I DOTNET I MATLAB I VLSI I NS2 I PHP www.foreview.co.in /theforeviewtech@gmail.com 1|Page Foreview Technologies Pvt Ltd VLSI # 13, 2nd Floor, Rajagopal Mudhaliyar Street, Opp national theatre, West Tambaram, Chennai-45 Mobile: 9043033334 & 8680002222 Office: 044-42602321 foreview.vlsi@gmail.com 32. Speech Recognition Based Wireless Automation Of Home Loads With Fault Identification For Physically Challenged 33. The design and implementation of fire smoke detection system based on FPGA 34. Improve quality of care with remote activity and fall detection using ultrasonic sensors 35. Intelligent wireless communication devices for efficient data transfer and machine control 36. Web-based Student Attendance System using RFID Technology 37. Design and implementation of Direct Torque Control of Induction Machine on FPGA 38. Design and energetic analysis of an advanced control existing lighting systems 39. Analysis of an Indoor Biomedical Radar-Based System for Health Monitoring 40. A Wireless Irradiance-Temperature-Humidity Sensor for Photovoltaic Plant Monitoring Applications 41. Dual –Edge triggered Sense-Amplifier Flip Flop For Low Power systems 42. Folding ADC with Nano metric Compatible Architecture by Using a High Dynamic Input/output Folding Amplifier 43. A CMOS Magnitude/Phase Measurement Chip for Impedance Spectroscopy 44. A Low Power CMOS Voltage Mode SRAM Cell for High Speed VLSI Design 45. A Low Power Discreet Time Sigma Delta Modulator in 50nm CMOS 46. A Low-Power Dual-Mode Continuous-Time Delta-Sigma Modulator with a Folded Quantizer 47. A Low-Power, Area Efficient Design for Wide Fan-in Domino Logic based Comparators 48. An 18.7mW 10-GHz Phase-Locked Loop Circuit in 0.13-μm CMOS 49. A Sub-1V 32nA Process, Voltage and Temperature Invariant Voltage Reference Circuit 50. Average-8T Differential-Sensing Sub threshold SRAM With Bit Interleaving and 1k Bits Per Bit line 51. Comparative Study & Analysis 0132nm FD-SOI/SON and CNFET based 4x4 SRAM Cell Array 52. Defect-Oriented Non-Intrusive RF Test Using On-Chip Temperature Sensors 53. Design and Implementation of a High-Speed, Power-Efficient, Modified Hybrid-Mode Sense Amplifier for SRAM Applications 54. Divide-by-Three Injection-Locked Frequency Dividers Over 200 GHz in 40-nm CMOS 55. Efficiency of Oscillation-based BIST in 90nm CMOS Active Analogy Filters 56. Energy-Efficient Low-Latency 600 MHz FIR With High-Overdrive Charge-Recovery Logic 57. Reconfigurable low power noise Amplifier Using MEMS Varactor 58. Stochastic degradation modelling and simulation for analog integrated circuits in nano meter CMOS 59. Radiation Effects in Advanced Multiple Gate and Silicon-on-Insulator Transistors EMBEDDED SYSTEMS I POWER ELECTRONICS I JAVA I DOTNET I MATLAB I VLSI I NS2 I PHP www.foreview.co.in /theforeviewtech@gmail.com 2|Page Foreview Technologies Pvt Ltd VLSI # 13, 2nd Floor, Rajagopal Mudhaliyar Street, Opp national theatre, West Tambaram, Chennai-45 Mobile: 9043033334 & 8680002222 Office: 044-42602321 foreview.vlsi@gmail.com 60. Self controllable voltage level circuit for low level power, High speed 7T SRAM cell 61. Optical Receiver Using Noise Cancelling With an Integrated Photodiode in 40 nm CMOS Technology 62. Hardware Implementations of efficiency comparison of AES 63. A Secure Software Implementation of Nonlinear AES S-Box with the Enhancement of Biometrics. 64. An efficient FPGA implementation of the Advanced Encryption Standard algorithm. 65. Low Power FPGA Implementation of Digital FIR Filter Based on Low Power Multiplexer Base Shift/Add Multiplier. 66. Design and Implementation of Area-optimized AES Based on FPGA. 67. Construction of Optimum Composite Field Architecture for Compact High-Throughput AES S-Boxes. 68. Scalable 128-bit AES-CM Crypto-Core Reconfigurable Implementation for Secure Communications 69. Advanced FPGA Design of A Novel low power fir filter. 70. Area-Efficient Parallel FIR Digital Filter Structures for Symmetric Convolutions Based on Fast FIR Algorithm. 71. VLSI Design and Implementation of Low Power MAC for Digital FIR Filter. 72. Design of Digit-Serial FIR Filters: Algorithms, Architectures, and a CAD Tool. 73. Low-Cost FIR Filter Designs Based on Faithfully Rounded Truncated Multiple Constant Multiplication/Accumulation. 74. A Reconfigurable FIR Filter Architecture to Trade off Filter Performance for Dynamic Power Consumption 75. FPGA Design and Implementation of Vedic multiplier. 76. Design of Area and Speed wise superior Vedic multiplier for FPGA based arithmetic circuits. 77. FPGA Design of High Speed and Area Efficient Vedic Multiplier 78. New Reconfigurable Architectures for Implementing FIR Filters with Low Complexity. 79. Vedic Mathematics for Fast Multiplication in DSP applications. 80. Advanced FPGA Design for 32-bit MAC unit using Vedic multiplier. 81. Design and Analysis of Low Power Multipliers and 4:2 Compressor Using Adiabatic Logic. 82. VLSI Design of Testable Reversible Sequential Circuits. 83. Performance Analysis of Sequential Circuits using reversible logic. 84. An Optimized Design of Reversible Sequential Digital Circuits. 85. Design of Asynchronous Sequential Circuits using Reversible Logic Gates. 86. Using the Asynchronous Paradigm for Reversible Sequential Circuit Implementation. 87. High Performance DCT Implementation Using Reduced Complexity Wallace Multiplier. EMBEDDED SYSTEMS I POWER ELECTRONICS I JAVA I DOTNET I MATLAB I VLSI I NS2 I PHP www.foreview.co.in /theforeviewtech@gmail.com 3|Page Foreview Technologies Pvt Ltd VLSI # 13, 2nd Floor, Rajagopal Mudhaliyar Street, Opp national theatre, West Tambaram, Chennai-45 Mobile: 9043033334 & 8680002222 Office: 044-42602321 foreview.vlsi@gmail.com 88. High performance DADDA Multiplier implementation using high speed carry select adder. 89. VLSI Design of Wallace Tree Multiplier by Sklansky Adder. 90. Improvement of Wallace multipliers using Parallel prefix adders. 91. FPGA Design Of 128 Bit Low Power and Area Efficient Carry Select Adder. 92. Carry Bypass & Carry Select Adder Using Reversible Logic Gates. 93. A Scalable Memory-Based Reconfigurable Computing Framework for Nano scale Crossbar. 94. Hardware-Efficient Low-Power Image Processing System for Wireless Capsule Endoscopy. 95. VLSI Design of Approximate Message Passing for Signal Restoration and Compressive Sensing. 96. A High-Speed Low-Complexity Modified Radix-25 FFT Processor for High Rate WPAN Applications. 97. FFT Implementation with Fused Floating-Point Operations. Generic Mixed-Radix FFT Pruning. 98. Pipelined Architectures for Real-Valued FFT and Hermitian-Symmetric IFFT with Real Data paths. 99. FPGA based Pipelined Radix- 2K Feed forward FFT Architectures 100. VLSI Architecture for a Reconfigurable Spectrally Efficient FDM Baseband Transmitter. 101. A Pipeline VLSI Architecture for Fast Computation of the 2-D Discrete Wavelet Transform 102. An Efficient VLSI Architecture for Lifting-Based Discrete Wavelet Transform. 103. Memory-Efficient High-Speed Convolution-based Generic Structure for Multilevel 2-D DWT. 104. Techniques for Compensating Memory Errors in JPEG2000. 105. Low-Power Correlation for IEEE 802.16 OFDM Synchronization on FPGA. 106. Construction of Structured Regular LDPC Codes: A Design-Theoretic Approach. 107. Hybrid Path-Diversity-Aware Adaptive Routing with Latency Prediction Model in Networkon-Chip Systems. 108. FPGA based design for PNOC: Implementation on Verilog for FPGA. 109. AER and dynamic systems co-simulation over Simulink with Xilinx System Generator 110. Design and performance analysis of DWT/FFT based OFDM system 111. Design and VLSI Implementation of interpolators/decimators for DUC/DDC 112. FPGA chips and tools as the centre of an Design-Based Ana log Systems Education 113. Low Power VLSI Implementation of Adaptive Noise Canceller Based on Least Mean Square Algorithm 114. Multiphase technique to speed-up delay measurement via sub-sampling 115. Performance Evaluation and Receiver Front-End Design for On-Chip Millimetre-Wave Wireless Interconnect EMBEDDED SYSTEMS I POWER ELECTRONICS I JAVA I DOTNET I MATLAB I VLSI I NS2 I PHP www.foreview.co.in /theforeviewtech@gmail.com 4|Page Foreview Technologies Pvt Ltd VLSI # 13, 2nd Floor, Rajagopal Mudhaliyar Street, Opp national theatre, West Tambaram, Chennai-45 Mobile: 9043033334 & 8680002222 Office: 044-42602321 foreview.vlsi@gmail.com 116. A High-Level Simulink-Based Tool for FPAA Configuration 117. Real Time Hardware Co-simulation of Edge Detection for Video Processing System 118. VLSI Design and Implementation of Electronic Voting Machine 119. Simulation and Implementation of a BPSK Modulator on FPGA. 120. Implementation of QPSK Modulation and Demodulation on FPGA 121. BPSK System on Spartan 3E FPGA 122. Implementation of PSK and QAM demodulators on FPGA 123. Design and Simulation of 32-Point FFT Using Radix-2 Algorithm for FPGA Implementation 124. Platform-Independent Customizable UART Soft-Core 125. VLSI Architecture of Arithmetic Coder Used in SPIHT 126. 1024-Point Pipeline FFT Processor with Pointer FIFOs based on FPGA 127. Novel transistor level realization of ultra low power High Speed Vedic Multiplier 128. A Novel Adaptive Design Methodology for Minimum Leakage Power Considering PVT Variations on Nano scale VLSI Systems 129. Design and Sensitivity Analysis of a New Current-Mode Sense Amplifier for Low-Power SRAM 130. Ground Bounce Noise Reduction of Low leakage 1-bit Nano-CMOS based Full Adder Cells for Mobile Applications 131. CMOS Full-Adders for Energy-Efficient Arithmetic Applications 132. Variability Resilient Low-power 7T-SRAM Design for nano-Scaled Technologies 133. A Wide-Range All-Digital Delay-Locked Loop in 65nm CMOS Technology 134. Dual Stack Method: A Novel Approach to Low Leakage and Speed Power Product VLSI Design 135. Standby Leakage Power Reduction Technique for Nano scale CMOS VLSI Systems 136. Optimal Design For Ground Bounce Noise Reduction Using Sleep Transistor 137. A Novel Overlap-Based Logic Cell: An Efficient Implementation of Flip–Flops With Embedded Logic 138. Design of A Low Power Flip-Flop Using CMOS Deep Submicron Technology 139. A New Adaptive Weight Algorithm for Salt and Pepper Noise Removal 140. FPGA Implementation of Real-Time Object Tracking System on Spartan 3EDK 141. Memory-Efficient High-Speed Convolution-based Generic Structure for Multilevel 2-D DWT 142. A Pipeline VLSI Architecture for Fast Computation of the 2-D Discrete Wavelet Transform 143. An Efficient Denoising Architecture for Removal of Impulse Noise in Images 144. Dynamic Hand Gesture Recognition for Human- Computer Interactions 145. Dynamic Power Estimation for Motion Estimation Hardware 146. Blind Image Watermarking Using a Sample Projection Approach EMBEDDED SYSTEMS I POWER ELECTRONICS I JAVA I DOTNET I MATLAB I VLSI I NS2 I PHP www.foreview.co.in /theforeviewtech@gmail.com 5|Page Foreview Technologies Pvt Ltd VLSI # 13, 2nd Floor, Rajagopal Mudhaliyar Street, Opp national theatre, West Tambaram, Chennai-45 Mobile: 9043033334 & 8680002222 Office: 044-42602321 foreview.vlsi@gmail.com 147. An improved method of image edge detection based on wavelet transform 148. Mathematical Morphological Edge Detection For Remote Sensing Images 149. Flexible Hardware Architecture of Hierarchical K-Means Clustering for Large Cluster Number EMBEDDED SYSTEMS I POWER ELECTRONICS I JAVA I DOTNET I MATLAB I VLSI I NS2 I PHP www.foreview.co.in /theforeviewtech@gmail.com 6|Page