Introduction to VHDL

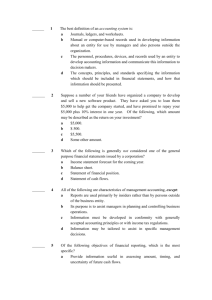

advertisement

Introduction to

VHDL

By

Mr. Fazrul Faiz Zakaria

School of Computer and Communication Engineering

UniMAP

VHDL ???

Very Hard Difficult Language

VHSIC Hardware Description Language

Very High Speed Integrated Circuits

VHDL is an IEEE standard

Why VHDL?

• HDL is a software solution due to limits in

hardware solutions and to:

– Increasing design complexity

– Increasing cost in time and investment

– Increasing knowledge requirement

– Inadequacy of other existing languages

3

VHDL main Features

• Supports the whole design process:

•

•

•

•

system level

RT level

logic level

circuit level (to some extent)

• Suitable for specification in

• behavioral domain

• structural domain

• Precise simulation semantics is associated with the language

constructs

Behavioral Modeling

• Only the functionality of the circuit, no structure

• Synthesis tool creates correct logic

• For the purpose of synthesis as well as simulation

Input

if (shift_left)

for (j=0; j<8; j=j+1)

#5 out[j]=out[j-1];

else

for (j=0; j<8; j=j+1)

#5 out[j] = out[j+1];

outputs

Structural Modeling

• Functionality and structure of the circuit

• Call out the specific hardware

• For the purpose of synthesis

Higher-level Component

input1

output1

Lower-level

Component1

Lower-level

Component1

inputn

outputn

VHDL Architectures

Abstraction Levels VHDL Architectures

Algorithmic

FSM

Behavioral

How it works

Structural

How it is connected

RTL

Gate

Layout

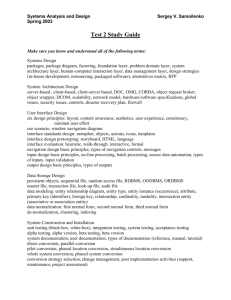

Basic VHDL Modeling

Structure

Library / Package Declaration

Entity Declaration

Architecture Flow

LIBRARY / PACKAGE DECLARATION

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_signed.all;

use ieee.std_logic_unsigned.all;

use ieee.std_logic_arith.all;

library work;

use work.my_package.entity_name;

use work.my_package.function_name;

Entity Declaration

• Specifies the input and output signals of the entity

• modes : in, out, inout, buffer

• Format :

Entity name is

port (port_name : mode data_type);

End name;

Entity Declaration (2)

entity name

port names

port mode (direction)

entity reg4 is

port ( d0, d1, d2, d3, en, clk : in bit;

q0, q1, q2, q3 : out bit );

end entity reg4;

punctuation

reserved words

port type

Rules for Entity Name

• Any alphanumeric character may be used in the name, as well as

the ‘_’ underscore character.

• It is not case sensitive

• Cannot be a VHDL keyword

• Cannot begin with a number, must begin with a letter

• Cannot have 2 straight ‘_ _’ underscores

• Cannot end with an ‘_’ underscore

• Cannot have a blank space

ARCHITECTURE

•

•

•

•

The Internal Aspect of a Design Unit

Can be behavioral (RTL) or structural

Always associated with single entity

Single entity can have multiple architectures

architecture architecture_name of entity_name is

{architecture_declarative_part}

begin

{architecture_descriptive_part}

end [architecture_name];

Operators

Architecture : Behavioral Modeling

• Architecture body

– describes an implementation of an entity

– may be several per entity

• Behavioral architecture

– describes the algorithm performed by the

module

– contains

• process statements, each containing

– sequential statements, including

» signal assignment statements and

» wait statements

Architecture : Behavioral Modeling

architecture behav of reg4 is

begin

sensitivity list

process (d0, d1, d2, d3, en, clk)

variable stored_d0, stored_d1, stored_d2, stored_d3 : bit;

begin

if en = '1' and clk = '1' then

stored_d0 := d0;

notice := syntax

stored_d1 := d1;

used for equating values

stored_d2 := d2;

from signals...

stored_d3 := d3;

end if;

simulates real-world

q0 <= stored_d0 after 5 ns;

q1 <= stored_d1 after 5 ns;

propagation delays.

q2 <= stored_d2 after 5 ns;

q3 <= stored_d3 after 5 ns;

end process;

end behav;

Behavioral Way’s Example

Behavioral Way’s Example (2)

Architecture : Structural Modeling

• Structural architecture

– implements the module as a composition of

subsystems

– contains

• signal declarations, for internal interconnections

– the entity ports are also treated as signals

• component instances

– instances of previously declared entity/architecture pairs

• port maps in component instances

– connect signals to component ports

Structural way’s example

bit0

d_latch

d

q

d0

q0

clk

bit1

d_latch

d

q

d1

q1

clk

bit2

d_latch

d

q

d2

q2

clk

bit3

d_latch

d

q

d3

en

clk

gate

and2

a

y

b

clk

int_clk

q3

Structural way cont..

• First declare D-latch and and-gate entities and architectures

entity d_latch is

port ( d, clk : in bit;

out bit );

end entity d_latch;

q :

architecture basic of d_latch is

begin

process (clk, d)

begin

if clk = ‘1’ then

q <= d after 2 ns;

end if;

end process;

end basic;

entity and2 is

port ( a, b : in bit;

y : out bit );

end entity and2;

architecture basic of and2

is

begin

process (a, b)

begin

y <= a and b after 2

ns;

end process ;

end basic;

Structural way...

• Declare corresponding components in register architecture body

architecture struct of reg4 is

component d_latch

port ( d, clk : in bit; q : out bit );

end component;

component and2

port ( a, b : in bit; y : out bit );

end component;

signal int_clk : bit;

...

Structural way..

• Now use them to implement the register

...

begin

bit0 : d_latch

port map ( d0,

bit1 : d_latch

port map ( d1,

bit2 : d_latch

port map ( d2,

bit3 : d_latch

port map ( d3,

gate : and2

port map ( en,

end struct;

int_clk, q0 );

int_clk, q1 );

int_clk, q2 );

int_clk, q3 );

clk, int_clk );

Mixed Behavior and Structure

• An architecture can contain both behavioral and structural

parts

• process statements and component instances

• collectively called concurrent statements

• processes can read and assign to signals

• Example: register-transfer-level (RTL) Model

• data path described structurally

• control section described behaviorally

Mixed Example

multiplier

multiplicand

shift_reg

control_

section

shift_

adder

reg

product

Mixed Example

entity multiplier is

port ( clk, reset : in bit;

multiplicand, multiplier : in integer;

product : out integer );

end multiplier;

architecture mixed of mulitplier is

signal partial_product, full_product : integer;

signal arith_control, result_en, mult_bit, mult_load : bit;

begin

arith_unit : entity work.shift_adder(behavior)

port map ( addend => multiplicand, augend => full_product,

sum => partial_product,

add_control => arith_control );

result : entity work.reg(behavior)

port map ( d => partial_product, q => full_product,

en => result_en, reset => reset );

...

Mixed Example

…

multiplier_sr : entity work.shift_reg(behavior)

port map ( d => multiplier, q => mult_bit,

load => mult_load, clk => clk );

product <= full_product;

process (clk, reset)

-- variable declarations for control_section

-- …

begin

-- sequential statements to assign values to control signals

-- …

end process;

end mixed;

Concurrent vs Sequential

• Behavioral part for a combinational system divided

into 2 categories

• Concurrent assignment statements

• Simple signal assignment

• Conditional signal assignment (when…else)

• Selected signal assignment (with…select)

• Sequential assignment statements

• If statement (if…then…else)

• Case statement (case…when)

• Loop statement (For-Loop & While-Loop)

Concurrent Assignment Statements

• Defines an interconnected block by assigning values to signals

• Executes continuously

• Order of statements in a body is not affected

• Eg :

signal_name <= expression;

“when…else” Statements

Architecture beh of

Begin

I0 <= ‘1’ when D =

I1 <= ‘1’ when D =

I2 <= ‘1’ when D =

I3 <= ‘1’ when D =

End beh;

dec_norm_we is

“00”

“01”

“10”

“11”

else

else

else

else

‘0’;

‘0’;

‘0’;

‘0’;

“when…else” Statements

Entity dec_we is

Port( D

: in

I

: out

End dec_we;

std_logic_vector(1 downto 0);

std_logic_vector(3 downto 0));

Architecture beh of dec_we is

Begin

I <= “0001” when D=“00” else

“0010” when D=“01” else

“0100” when D=“10” else

“1000” when D=“11”;

End beh;

“with…select” Statements

Architecture beh of dec_sel is

Begin

with D select

I <=

End beh;

“0001” when “00”,

“0010” when “01”,

“0100” when “10”,

“1000” when “11”;

Sequential Assignment Statements

• The order of the statements is significant and can affect the

semantics of the code

• To differentiate from concurrent assignment, sequential assignment

must be separated

• Sequential assignments are enclosed inside a “process statement”

to distinguish from concurrent assignments

“if…then…else” Statements

Architecture beh of dec_if is

Begin

process (D)

begin

if D=“00” then

I <= “0001”;

elsif D=“01” then

I <= “0010”;

elsif D=“10” then

I <= “0100”;

else

I <= “1000”;

end if;

end process;

End beh;

“case…when” Statements

Architecture beh

Begin

process (D)

begin

case (D) is

when “00” =>

when “01” =>

when “10” =>

when “11” =>

end case;

end process;

End beh;

of dec_cs is

I

I

I

I

<=

<=

<=

<=

“0001”;

“0010”;

“0100”;

“1000”;

Loop Statements

Library ieee;

Use ieee.std_logic_1164.all;

Entity numbits is

Port(

D

count

End numbits;

: in

: out

std_logic_vector(1 to 3);

integer range 0 to 3);

Architecture beh of numbits is

Begin

process (D)

variable tmp : integer;

begin

tmp := 0;

for i in 1 to 3 loop

if D(i) = ‘1’ then

tmp := tmp + 1;

end if;

end loop;

count <= tmp;

end process;

End beh;

Mixed Behavioral Statements

• Processes are concurrent

• Sequential activity within each process

Nesting of statements :

• Concurrent statements in a concurrent statement

• Sequential statements in a concurrent statement

• Sequential statements in a sequential statement

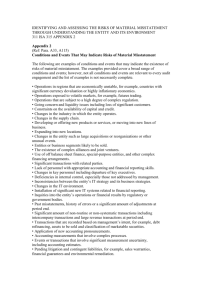

Basic Design Methodology

Requirements

RTL Model

Simulate

Synthesize

Gate-level

Model

ASIC or FPGA

Simulate

Place & Route

Timing

Model

Simulate

Test Bench