The LC-3 as a von Neumann Machine

advertisement

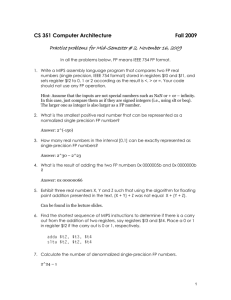

1 The von Neumann Model – Chapter 4 COMP 2620 Dr. James Money COMP 2620 The LC-3 as a von Neumann Machine The LC-3 as a von Neumann Machine Note the two kinds of arrowheads in the diagram: – – Filled in – control signals for the processing of data elements Not Filled in – denotes data elements and the flow of data along the path The ALU has two input data elements and one output The ALUK line controls the operation performed by the ALU The LC-3 as a von Neumann Machine Note the lines with the slash through them and the number next to it This indicates the number of bits transmitted along the data and/or control path Same notation applies to both data and control paths Memory Memory contains the storage elements along with the MAR for addressing the memory elements The MDR holds the contents of a memory location to/from storage MAR is 16 bits, so the address space is 216 The MDR is 16 bits indicating each memory location is 16 bits Input/Output There are two: – – Keyboard Monitor For the keyboard, there are two registers: – – KBDR – keyboard data register which has the ASCII code if the keys struck KBSR – keyboard status register for status about the keys struck Input/Output The monitor has also two registers: – – DDR – ASCII code of the character to be displayed on the screen DSR – the associated status information for the character to be printed on the screen We will talk more about these in detail in Chapter 8 Processing Unit This consists of the – – ALU – arithmetic and logic unit Eight registers R0,R1,…,R7 Use to store temporary values Also used as operands for operations Processing Unit The ALU only has three operations: – – – Addition Bitwise AND Bitwise NOT We will have to spend some time implementing the other functions to achieve full assembly language Control Unit This contains the parts to control flow of the program executing It contains the finite state machine, which directs all activity Processing is carried out step-by-step and not clock cycle by clock cycle There is the CLK input to the finite state machine which specifies how long each clock cycle lasts Control Unit The Instruction Register (IR) is input to finite state machine and has the current instruction This is input to the finite state machine since it determines what activities must be carried out The Program Counter (PC) keeps track of the next instruction to be executed Control Unit Note all the outputs from the finite state machine are controls These control processing in various parts of the computer For example, the ALUK of 2 bits controls which operation is performed by the ALU Another is the GateALU which controls whether the output of the ALU is provided to the processor during the current clock cycle. Instruction Processing The most basic unit of processing is the instruction There are two parts: – – Opcode – what the instruction does Operands – the parameters to the opcode, for example Registers Constants Instruction Processing Each instruction is 16 bits, or one word on the LC-3 The bits are numbered left to right from [15] to [0]. Bits [15:12] contain the opcode There are at most 24 = 16 opcodes Bits [11:0] are operands Instruction Cycle Each instruction is handled in a systematic way through a sequence of steps call the instruction cycle Each step is called a phase There are six phases to the cycle Instruction Cycle The six phases of the instruction cycle are: – – – – – – Fetch Decode Evaluate Address Fetch Operands Execute Store Result FETCH Fetch obtains the next instruction from memory and loads it into the IR of the control unit We first use the PC to find the address of the next instruction FETCH The FETCH stage takes multiple steps: – – – MAR is loaded with the value of PC and increment the PC Memory is interrogated which results in the instruction being placed in the MDR The IR is loaded with the contents of the MDR Note the PC must be incremented at the same time FETCH Note that the first step takes 1 machine cycle The second one can take multiple machine cycles Step 3 takes on machine cycle DECODE This step looks at the highest 4 bits to determine what to do A 4-to-16 decoder decides which of the 16 opcodes is to be processed Input is IR[15:12] The output line is the one that corresponds to the opcode EVALUATE ADDRESS This phase reads the memory address needed to process the instruction An example is the LDR – – – Causes a value stored in memory to be loaded into a register The memory location is in the form base+offset This final memory location is being evaluated at this step FETCH OPERANDS This phase obtains the source operands For the LDR example, the MAR is loaded with the address of the EVALUATE ADDRESS phase and reading memory with data in the MDR For ADD, this would be obtaining the values for the source operands Execute In this phase, the instruction is actually executed For ADD, this is the step of performing the addition in the ALU STORE RESULT The last phase is to write the result to the correct location This may involve writing to memory or registers Instruction Cycle Once STORE RESULT is done, the control unit starts again with a new machine instruction It begins with FETCH and repeats The PC already has the location of the next instruction to execute Continues until processing order breaks Example: LC-3 ADD Instruction LC-3 has 16-bit instructions. – Each instruction has a four-bit opcode, bits [15:12]. LC-3 has eight registers (R0-R7) for temporary storage. – Sources and destination of ADD are registers. “Add the contents of R2 to the contents of R6, and store the result in R6.” Example: LC-3 LDR Instruction Load instruction -- reads data from memory Base + offset mode: – – add offset to base register -- result is memory address load from memory address into destination register “Add the value 6 to the contents of R3 to form a memory address. Load the contents of that memory location to R2.”