COEN 4730

advertisement

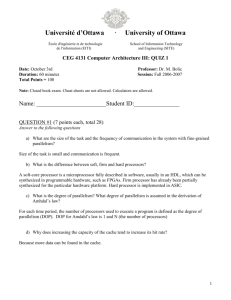

COEN 4730 (COEN 173) Computer Architecture Credits and contact hours: 3 credit course, meeting for 3 50-minute periods each week. Course coordinator: George Corliss Text: John L. Hennessy and David Patterson, Computer Architecture: A Quantitative Approach, Fourth Edition, Morgan Kaufham, 2007. Catalog description: Review of basic computer architecture. Evaluation of architecture performance. Design and evaluation of instruction sets. Pipeline processors and instruction scheduling. Vector processors. Memory hierarchy and design including cache, main and virtual memories. Memory protection schemes. Input/output and its relation to system performance. COEN design elective in the area of hardware. Prerequisites: Senior standing, 3.000 GPA, and COEN 4710 (COEN 171) Computer Hardware; or consent of instructor. Elective: COEN design elective in the area of hardware. Professional component: Engineering science 50 % Engineering design 50 % Course Goals: To provide students the ideas and concepts required to understand the architectures of modern microprocessors, including instruction set principles, instruction-level parallelism, memory hierarchy designs, and I/O; to provide students the analytical tools for assessing processor performance; and to provide students the opportunity to become familiar with the Internet and the technical literature as sources of current information on the topics of the course. Specific outcomes of instruction By the end of this course, students should be able to perform the following tasks: 1. Describe analytical methods for measuring and reporting processor performance. 2. Apply Amdahl’s law to determine the speedup of a processor resulting from processor enhancements. 3. Classify various instruction set architectures. 4. Describe a basic processor pipeline. 5. List and discuss the various types of pipeline hazards. 6. Describe loop unrolling, scheduling, and forwarding as used for pipeline hazard elimination. 7. Describe techniques for static branch prediction. 8. Describe hardware techniques for dynamic branch prediction. 9. Describe a typical floating-point pipeline. 10. Describe the MIPS pipeline. 11. Define instruction-level parallelism (ILP). 12. List and discuss three types of instruction dependencies. 13. Describe dynamic scheduling as a technique for overcoming data hazards. 14. Describe dynamic scheduling with a scoreboard. 15. Describe the Tomasulo algorithm. 16. Discuss branch penalty reduction with dynamic hardware prediction. 17. Describe a simple superscalar architecture as a device for taking advantage of more ILP with multiple issue. 18. Discuss compiler support for exploiting more ILP. 19. Define conditional and predicated instructions. 20. Discuss compiler speculation and hardware speculation. 21. Describe the memory hierarchy. 22. Discuss block placement, block identification, block replacement, and write policy as they apply to any level of the memory hierarchy. 23. Describe the concept of and basic structure of a cache. 24. Define direct mapped, associative, and set associative. 25. Discuss the analytical assessment of cache performance. 26. List and describe several techniques for reducing cache misses. 27. List and describe several techniques for reducing cache miss penalties. 28. List and describe several techniques for reducing cache hit time. 29. List and describe several techniques for improving main memory bandwidth. 30. List and discuss several differences between caches and virtual memory. 31. Discuss protection in memory hierarchy. 32. Describe memory protection in a modern processor. 33. Describe several levels of RAID. Student outcomes addressed by the course: Partial fulfillment of Criterion 3 objectives A, C, E, I, J Brief list of topics to be covered Fundamentals of Computer Design (10%) Instruction-level Parallelism and Its Exploitation (25%) 2 Exploiting Instruction-Level Parallelism (20%) 3 Multi-Processors and Thread-Level Parallelism: (20%) 4 Memory-Hierarchy Design: (15%) Storage Systems: (10%) Last modified: December 19, 2011 H&P Chapter 1 H&P Chapter H&P Chapter H&P Chapter H&P Chapter 5 H&P Chapter 6