ppt

advertisement

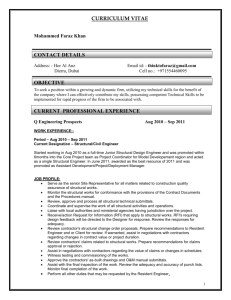

Mohammed Anvar P.K AP/ECE Al-ameen Engineering College Kulappully,Shoranur-2 Feedback sequential circuits are the most common example of fundamental mode circuits. In such circuits, inputs are not normally allowed to change simultaneously. The analysis procedure assumes that inputs change one at a time, allowing enough time between successive changes for the circuit to settle into a stable internal state. This differs from clocked circuits, in which multiple inputs can change at almost arbitrary times without affecting the state, and all input values are sampled and state changes occur with respect to a clock signal. feedback sequential circuits may be structured as Mealy or Moore circuits A circuit with n feedback loops has n binary state variables and 2n states. Mohammed Anvar PK,AP/ ECE, Al-Ameen Engg College Mohammed Anvar PK,AP/ ECE, Al-Ameen Engg College • Feedback sequential circuits are the most common example of fundamental mode circuits. • In such circuit inputs are normally allowed to change simultaneously • In the analysis procedure assumes that input change one at a time and allowing enough time between successive changes for the circuit to settle into a stable internal state Mohammed Anvar PK,AP/ ECE, Al-Ameen Engg College Transition table/excitation table Mohammed Anvar PK,AP/ ECE, Al-Ameen Engg College The state of the feedback loop (and the circuit) can be written as a function of the current state(present state) and input, and enumerated by a transition table as shown in Figure A transition table has one row for each possible combination of the state variables In a fundamental-mode circuit, a total state is a particular combination of internal state (the values stored in the feedback loops) and input state (the current value of the circuit inputs). A stable total state is a combination of internal state and input state such that the next internal state predicted by the transition table is the same as the current internal state(present state) . If the next internal state is different, then the combination is an unstable total state. To complete the analysis of the circuit, we must also determine how the outputs behave as functions of the internal state and inputs. Mohammed Anvar PK,AP/ ECE, Al-Ameen Engg College Mohammed Anvar PK,AP/ ECE, Al-Ameen Engg College Next state , Y Present Output State, y CD=00 CD=01 CD=10 CD=11 Q A A A B A 0 B B B B A 1 At any time, the circuit is in a particular internal state and a particular input is applied to it; we called this combination the total state of the circuit. Let us start at the stable total state “A/00” (y = A,CD = 00), as shown in Figure Now suppose that we change D to 1. The total state moves to one cell to the right; we have a new stable total state, A/01. The D input is different, but the internal state and output are the same as before. Next, let us change C to 1. The total state moves one cell to the right to A/11, which is unstable. The next-state entry in this cell sends the circuit to internal state B, so the total state moves down one cell, to B/11. Examining the next-state entry in the new cell, we find that we have reached a stable total state. Mohammed Anvar PK,AP/ ECE, Al-Ameen Engg College Consider the circuit Mohammed Anvar PK,AP/ ECE, Al-Ameen Engg College Next state and output equation Excitation table Mohammed Anvar PK,AP/ ECE, Al-Ameen Engg College Some transitions in flow table will not occur in practice because of the assumption that both w1 and w2 cannot change simultaneously In state A the circuit is stable under the evaluation w2w1 =00, its input cannot change to 11 without passing through the valuation 01 or 10 in which case the new state would be B or C respectively Thus the transition from A under w2w1=11 can be left unspecified similarly if the circuit is stable in state B in which case w1w1=01 it is impossible to change to D by changing the inputs w2w1=10 this entry should also be unspecified If the circuit is stable state C under w2w1=11 it is not possible to go to A by changing w2w1=00 directly However the transition is possible by changing the inputs one at a time because the circuit is stable in C for both w2w1=01 and w2w1=10 Mohammed Anvar PK,AP/ ECE, Al-Ameen Engg College modified flow table Flow diagram Mohammed Anvar PK,AP/ ECE, Al-Ameen Engg College Steps :1. Derive the state diagram and primitive flow table that realize the required functional behavior 2. Reduce the number of states of primitive flow table using state reduction technique 3. Derive transition table/excitation table 4. Obtain the next state and output equations 5. Construct a circuit that implement these expression Mohammed Anvar PK,AP/ ECE, Al-Ameen Engg College A race condition is said to exist in an asynchronous sequential circuit when 2 or more binary state variable changes value in response to a change input variable. when unequal delays are encountered a race condition may cause , a state variable to change in an unpredictable manner For exmpl. A state variable must change from 00 to 11.the difference delay may cause the following possibilities State change:- 00 -11 possibility 1:- 00 -10 -11(1st variable is faster than 2nd variable) Possibility 2:- 00-01-11(2nd variable is faster that 1st variable) Thus the order by which the state variable change may not be known in advance Mohammed Anvar PK,AP/ ECE, Al-Ameen Engg College There are mainly two types of races ◦ Non critical race:-if the final stable state that the circuit reaches does not depend on the order in which the state variable change ◦ Critical race:-if it is possible to end up with two or more different stable states depending on the order in which the state variable change Mohammed Anvar PK,AP/ ECE, Al-Ameen Engg College Mohammed Anvar PK,AP/ ECE, Al-Ameen Engg College Mohammed Anvar PK,AP/ ECE, Al-Ameen Engg College The state diagram and tables are convenient for describing of FSM that have only few inputs and Output For larger machines the designers often Use a different form of representation called the Algorithmic State Machine(ASM) chart. An ASM chart is a type of flow chart that can be used to represent the state transitions and generated outputs for an FSM . The three types of elements used in ASM are Mohammed Anvar PK,AP/ ECE, Al-Ameen Engg College Mohammed Anvar PK,AP/ ECE, Al-Ameen Engg College Mohammed Anvar PK,AP/ ECE, Al-Ameen Engg College Mohammed Anvar PK,AP/ ECE, Al-Ameen Engg College Mohammed Anvar PK,AP/ ECE, Al-Ameen Engg College Mode 5 counter Mohammed Anvar PK,AP/ ECE, Al-Ameen Engg College Mohammed Anvar PK,AP/ ECE, Al-Ameen Engg College Mohammed Anvar PK,AP/ ECE, Al-Ameen Engg College Transient behavior: -Output could produce glitches(a short pulse) when input variables change. Glitches occur when the paths between inputs and output have different delays. Hazards :- ◦ Definitions. ◦ Finding hazards. ◦ Eliminating hazards. Mohammed Anvar PK,AP/ ECE, Al-Ameen Engg College Static Hazards: Static-1 Hazard : Two input combinations that :-differ in only one variable .-both produce logic 1 .-possibly produce Logic 0 glitch during input variable transition. Static-0 Hazard : Two input combinations that -differ in only one variable -Both produce logic 0 -Possibly produce Logic 1 glitch during input variable transition Dynamic hazards: -The output could change more than once during input transitions-Caused by multiple paths with different delays from input to the output Mohammed Anvar PK,AP/ ECE, Al-Ameen Engg College Programmable Logic Devices (PLD) General purpose chip for implementing circuits Can be customized using programmable switches Main types of PLDs PLA PAL ROM Mohammed Anvar PK,AP/ ECE, Al-Ameen Engg College Fixed AND array (decoder) Inputs Programmable Connections Programmable OR array Outputs (a) Programmable read-only memory (PROM) Inputs Programmable Connections Programmable AND array Fixed OR array Outputs Programmable OR array Outputs (b) Programmable array logic (PAL) device Inputs Programmable Connections Programmable AND array Programmable Connections (c) Programmable logic array (PLA) device Comparing PALs and PLAs ◦ PALs have the same limitations as PLAs (small number of allowed AND terms) plus they have a fixed OR plane less flexibility than PLAs ◦ PALs are simpler to manufacture, cheaper, and faster (better performance) ◦ PALs also often have extra circuitry connected to the output of each OR gate The OR gate plus this circuitry is called a macrocell SPLDs (PLA, PAL) are limited in size due to the small number of input and output pins and the limited number of product terms ◦ Combined number of inputs + outputs < 32 or so CPLDs contain multiple circuit blocks on a single chip Each block is like a PAL: PAL-like block ◦ Connections are provided between PAL-like blocks via an interconnection network that is programmable ◦ Each block is connected to an I/O block as well PAL-like block PAL-like block I/O block I/O block Structure of a CPLD Interconnection wires PAL-like block PAL-like block I/O block I/O block Internal Structure of a PAL-like Block ◦ Includes macrocells Usually about 16 each ◦ Fixed OR planes OR gates have fan-in between 5-20 ◦ XOR gates provide negation ability XOR has a control input PAL-like block PAL-like block DQ DQ DQ More on PAL-like Blocks ◦ CPLD pins are provided to control XOR, MUX, and tri-state gates ◦ When tri-state gate is disabled, the corresponding output pin can be used as an input pin The associated PAL-like block is then useless ◦ The AND plane and interconnection network are programmable ◦ Commercial CPLDs have between 2-100 PAL-like blocks Example CPLD ◦ Use a CPLD to implement the function f = x1x3x6' + x1x4x5x6' + x2x3x7 + x2x4x5x7 (from interconnection wires) x1 x2 x3 x4 x5 x6 x7 unused PAL-like block 0 1 0 f D Q • The internal PLDs are called Configurable Functional Blocks (FBs or CFBs) • Each FB has 36 inputs and 18 Macrocells (effectively a “36V18”) • Each CLPD is packaged in a plastic-leaded chip carrier (PLCC) • The number of I/O pins are much less than the total number of Macrocells in family of devices Mohammed Anvar PK,AP/ ECE, Al-Ameen Engg College 36 Signal pins 18 outputs Global Clock Global set/reset Global 3 state control Mohammed Anvar PK,AP/ ECE, Al-Ameen Engg College 18 Output enable signals XC9500 I/O Block Switch matrix for XC95108 • Could be anything from a limited set of multiplexers to a full crossbar. • Multiplexer -- small, fast, but difficult fitting • Crossbar -- easy fitting but large and slow 1 FPGA ◦ SPLDs and CPLDs are relatively small and useful for simple logic devices Up to about 20000 gates ◦ Field Programmable Gate Arrays (FPGA) can handle larger circuits No AND/OR planes Provide logic blocks, I/O blocks, and interconnection wires and switches Logic blocks provide functionality Interconnection switches allow logic blocks to be connected to each other and to the I/O pins IOB IOB IOB CLB CLB CLB CLB CLB IOB CLB IOB IOB IOB IOB IOB Input/Output Block IOB SM CLB SM CLB IOB SM CLB SM CLB SM IOB Configurable Logic Block CLB SM SM CLB SM SM CLB CLB CLB CLB IOB IOB IOB IOB Mohammed Anvar PK,AP/ ECE, Al-Ameen Engg College Switch Matrix Mohammed Anvar PK,AP/ ECE, Al-Ameen Engg College Mohammed Anvar PK,AP/ ECE, Al-Ameen Engg College