V. - St. Aloysius Institute of Technology, Jabalpur

advertisement

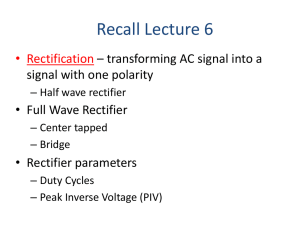

ST. ALOYSIUS INSTITUTE OF TECHNOLOGY, JABALPUR 2015-16 SAIT, JABALPUR DEPARTMENT OF ELECTRICAL & ELECTRONICS ENGINEERING LABORATORY – ELECTRONIC DEVICES & CIRCUITS LAB (B-408) SUBJECT - ELECTRONIC DEVICES & CIRCUITS SUBJECT CODE: EX-304 BRANCH – EX SEMESTER - III (GRADING) LIST OF EXPERIMENTS 1. To study and plot the waveform of Half Wave Rectifier. 2. To study and plot the waveform of Full Wave Rectifier. 3. To study and plot the waveform of Clipper circuit. 4. To study and plot the waveform of Clamper circuit. 5. To study and plot the characteristics of Varactor Diode. 6. To Study and plot the characteristics of Zener Diode. 7. To study and plot the characteristics of Schottkey Diode. 8. To study and plot the characteristic of UJT. 9. To study and plot the characteristics of JFET. 10. To study and plot the characteristics of MOSFET. DEPATRMENT OF ELECTRICAL & ELECTRONICS Page 1 ST. ALOYSIUS INSTITUTE OF TECHNOLOGY, JABALPUR 2015-16 INDEX S.NO. NAME OF EXPERIMENT 1. To study and plot the waveform of Half Wave Rectifier. 2. To study and plot the waveform of Full Wave Rectifier. 3. To study and plot the waveform of Clipper circuit. 4. To study and plot the waveform of Clamper circuit. 5. To study and plot the characteristics of Varactor Diode. 6. To Study and plot the characteristics of Zener Diode. 7 To study and plot the characteristics of Schottkey Diode. 8 To study and plot the characteristic of UJT. 9. To study and plot the characteristics of JFET. 10. To study and plot the characteristics of MOSFET. PAGE NO. DATE GRADE/ TOTAL SIGNATURE DEPATRMENT OF ELECTRICAL & ELECTRONICS Page 2 ST. ALOYSIUS INSTITUTE OF TECHNOLOGY, JABALPUR __/__/201_ 2015-16 EXPERIMENT NO.-01 AIM:- To study and plot the waveform of Half Wave Rectifier. APPARATUS REQUIRED:S.NO. APPARATUS REQUIRED 1 Half Wave Rectifier Trainer Kit TYPE RANGE QUANTITY 1 2 3 THEORY:The rectifiers and filters are the initial stage of the DC power supply, which is essential for the operation of many electronics devices and circuits. A rectifier is a circuit which uses one or more diodes to convert AC voltage into pulsating DC voltage. It may broadly categorized in 2 types:1. Half Wave Rectifier. 2. Full Wave Rectifier. Half Wave Rectifier:- The fig. shows the circuit of Half Wave Rectifier, it uses one diode. AC 230V is step-down by transformer giving AC voltage Vi, during positive half cycle of Vi, diode D gets forward biased and it conducts. The resulting current IL flows through load RL providing the rectified O/P voltage VO across it. During negative half cycle diode becomes reverse biased. Hence no current (ignoring the extremely small reverse saturation current IO) flow through the diode. Hence the O/P voltage VO is zero. The pure sinusoidal voltage Vi gets converted into unidirectional voltage VO. DEPATRMENT OF ELECTRICAL & ELECTRONICS Page 3 ST. ALOYSIUS INSTITUTE OF TECHNOLOGY, JABALPUR 2015-16 Analysis of this O/P shows that DC O/P voltage Vdc is given by (i) DC O/P voltage Vdc is given by Vdc = V0 = Vm π Where Vm is the peak value of the I/P voltage Vi. (ii) Ripple Factor γ = AC voltage at I/P DC voltage at O/P = 1.21 Rectifier Efficiency :- Rectifier efficiency is defined as the ratio of dc power delivered to load to AC I/P power from transformer secondary. Po(dc) Efficiency = Pin(ac) Po(dc) = Pin(dc) V 2 dc RL = V 2 rms /R L rd +R L rd= forward biased resistance of each diode. PROCEDURE:1. Study the circuit provided on the front panel of the kit. 2. Switch ON the circuit. 3. Connect the CRO across the secondary of the Transformer. 4. Measure the peak value of the secondary voltage (Vm) and note it. 5. Connect points A-A and 1-3 using patch cords. 6. Observe the O/P on CRO at the O/P and note down the peak value of the O/P waveforms. 7. Calculate the V dc using formula given. 8. Calculate the Ripple Factor(r) 9. Draw the I/P and O/P waveforms. DEPATRMENT OF ELECTRICAL & ELECTRONICS Page 4 ST. ALOYSIUS INSTITUTE OF TECHNOLOGY, JABALPUR 2015-16 OBSERVATIONS:(a) AC input voltage Vi = ----------- V (b) DC output voltage Vdc = ---------- V (c) DC output voltage theoretically, 𝑉𝑑𝑐 𝑉 2𝑉𝑚 = 0.482 𝑉𝑑𝑐 (d) Ripple Factor 𝛾 = 𝑉𝐴𝐶 = 0.482 𝐷𝐶 RESULT:- Thus HWR is studied to obtain the efficiency. PRECAUTIONS:1. All connections should be right and tight and as per the circuit diagram. 2. Proper range of measuring instruments should be selected. 3. DEPATRMENT OF ELECTRICAL & ELECTRONICS Page 5 ST. ALOYSIUS INSTITUTE OF TECHNOLOGY, JABALPUR 2015-16 VIVA-VOCE DEPATRMENT OF ELECTRICAL & ELECTRONICS Page 6 ST. ALOYSIUS INSTITUTE OF TECHNOLOGY, JABALPUR __/__/201_ 2015-16 EXPERIMENT NO.-02 AIM:- To study and plot the waveform of Full Wave Rectifier. APPARATUS REQUIRED:S.NO. APPARATUS REQUIRED 1 Full Wave Rectifier Trainer Kit TYPE RANGE QUANTITY 2 3 THEORY:The rectifiers and filters are the initial stage of the DC power supply, which is essential for the operation of many electronics devices and circuits. A rectifier is a cicuit which uses one or more diodes to convert AC voltage into pulsating DC voltage. It may broadly categorized in 2 types:1. Half Wave Rectifier. 2. Full Wave Rectifier. There are two types of Full Wave Rectifiers. These are Full Wave Centre Tapped and Full Wave Bridge Rectifier. The O/P voltage is same for both. DEPATRMENT OF ELECTRICAL & ELECTRONICS Page 7 ST. ALOYSIUS INSTITUTE OF TECHNOLOGY, JABALPUR 2015-16 Full Wave Center Tapped Rectifier:- Full Wave Center Tapped Rectifier allows a uni-directional current to flow through the load during the entire input cycle, giving a DC output voltage that pulsates every half cycle of the input. The fig. shows the center tapped full wave rectifier which consist of two diodes D1 and center tapped transformer. AC 230V is stepped down by the transformer giving a voltage at secondary winding. The half of this voltage is developed between center tap and upper winding and remaining in other winding. During positive half cycle of input, let polarities of secondary voltage are as shown in fig. i.e. terminal A is positive w.r.t. terminal B, which Forward Bias D1(ON) and Reverse Bias D2(OFF) giving a load current through R L as indicated in fig. During negative half cycle of input, terminal B is positive w.r.t. terminal A, so D2 become ON and D1 become OFF giving load current IL due to D2 in the same direction during both positive and negative portions of input cycle. Therefore, the O/P voltage developed across load RL is a full wave rectified dc voltage as shown in fig. The analysis of the circuit shows that 𝑉𝑑𝑐 = 2𝑉𝑚 𝜋 Where Vm peak value of AC voltage VS 𝑉𝑟𝑚𝑠 = Ripple Factor = 𝑉𝑟𝑚𝑠 𝑉𝑑𝑐 𝑉𝑚 √2 Ripple Factor = 0.482 Rectifier Efficiency :- Rectifier efficiency is defined as the ratio of dc power delivered to load to AC I/P power from transformer secondary. Po(dc) Efficiency = Pin(ac) Po(dc) = Pin(dc) V 2 dc RL = V 2 rms /R L rd +R L rd = forward biased resistance of each diode. DEPATRMENT OF ELECTRICAL & ELECTRONICS Page 8 ST. ALOYSIUS INSTITUTE OF TECHNOLOGY, JABALPUR 2015-16 Full Wave Bridge Rectifier:- Full Wave Bridge Rectifier allows a uni-directional current to flow through the load during the entire input cycle, giving a DC output voltage that pulsates every half cycle of the input. A commonly used circuit for supplying large amount of dc power is the Bridge Rectifier. The operation of the circuit is as follows. The AC I/P 230V /50HZ is applied to the primary of 12-0V step-down transformer whose output at the secondary obtained is equal to 12V/50HZ AC voltage. This voltage is the input for the bridge rectifier. During the +ve half cycle of input Vi, Diodes D1 and D2 conducts developing the output voltage across RL. At this instant Diodes D3 and D4 remains in reverse biased. On the other hand, during the –ve half cycle of the input voltage Vi, Diode D1 and D2 are reverse biased and hence referred as open, and conduction occurs through Diode D3 and D4. Hence for both the cycles voltages obtained across the load resistor giving full wave rectified output. The pure sinusoidal voltage Vi gets converted into uni-directional voltage Vo. Analysis of this output shows that (a) DC output voltage Vdc is given by Vdc=Vo=2Vm/ π Where Vm is the peak value of the input voltage Vi. (b) Ripple Factor = 0.482 PROCEDURE:1. Study the circuit provided on the front panel of the kit. 2. Switch ON the circuit. 3. Connect the CRO across the secondary of the Transformer. 4. Measure the peak value of the secondary of the Transformer. 5. For HWR connect points A-A and 1-3 using patch chords. 6. Observe the O/P on CRO at the O/P and note down the peak value of the O/P Waveforms. 7. Calculate the Vdc using formula given. 8. Calculate the Ripple Factor (r) 9. Draw the I/P and O/P waveforms . 10. For full wave bridge rectifier connect point A&B of Transformer to the point A&B of diodes to form a configuration of full bridge rectifier as shown in fig. 11. Repeat the procedures 6 to 10 for FWR. DEPATRMENT OF ELECTRICAL & ELECTRONICS Page 9 ST. ALOYSIUS INSTITUTE OF TECHNOLOGY, JABALPUR 2015-16 12. For bridge rectifier connect point A&B to the bridge rectifier circuit and observe the O/P. 13. Repeat the procedures 6 to 10 for the same. OBSERVATIONS:(a) AC input voltage Vi = ----------- V (b) DC output voltage Vdc = ---------- V (c) DC output voltage theoretically, 𝑉𝑑𝑐 𝑉 2𝑉𝑚 = 0.482 𝑉𝑑𝑐 (d) Ripple Factor 𝛾 = 𝑉𝐴𝐶 = 0.482 𝐷𝐶 The ripple factor is same as that for the Full Wave Center Tapped Rectifier but has the advantage that the PIV across each Diode is the peak voltage across the load = Vm and not 2Vm as in the two Diode Full Wave Rectifier. RESULT:- Thus Full Wave Center Tapped & Full Wave Bridge Rectifier are studied to obtain the efficiency of each. So we conclude that Full Wave Bridge Rectifier is preferred than Full Wave Center Tapped and Half Wave Rectifier. PRECAUTIONS:PRECAUTIONS:1. All connections should be right and tight and as per the circuit diagram. 2. Proper range of measuring instruments should be selected. 3. DEPATRMENT OF ELECTRICAL & ELECTRONICS Page 10 ST. ALOYSIUS INSTITUTE OF TECHNOLOGY, JABALPUR 2015-16 VIVA-VOCE DEPATRMENT OF ELECTRICAL & ELECTRONICS Page 11 ST. ALOYSIUS INSTITUTE OF TECHNOLOGY, JABALPUR __/__/201_ 2015-16 EXPERIMENT NO.-03 AIM:- To study and plot the waveform of Clipper circuit.. APPARATUS REQUIRED:S.NO. APPARATUS REQUIRED TYPE 1 Clipper Circuit Trainer Kit 2 CRO 3 Function Generator 4 Patch Cord RANGE QUANTITY 1 As per requirement THEORY:Biased Positive Diode Clipper:If we connect I/P signal to circuit & short socket S1 & 1 then we get shunt positive clipper and if sockets S1 and 2 are shorted then we get biased shunt positive clipper. When I/P voltage is positive then diode will conduct and during negative I/P voltage diode will not conduct .It may be noted that the clipping takes place during positive cycle when Vi >V1. O/P +V +V Vin > V1 V1 t I/P T/2 T/2 -V -V T I/P Waveform T O/P Waveform Fig 1. The clipping level can be shifted up or down by varying the bias voltage V1. Negative Biased Diode Clipper:In this Ckt, clipping takes place during the negative half cycle only when the I/p voltage Vi<V1. The clipping level can be shifted up or down by varying the bias voltage (-V1). DEPATRMENT OF ELECTRICAL & ELECTRONICS Page 12 ST. ALOYSIUS INSTITUTE OF TECHNOLOGY, JABALPUR O/P Wave forms:- I/P 2015-16 +V +V -V1 -V -V T Fig (2) T I/P Waveform O/P Waveform Combination/Compound Clipper:Compound Clipper is combination of both Positive biased & negative biased clipper. For this S1 & 2 and S2 & 2 are shorted. Combination Clipped I/P + Vin +V O/P V1 a 0 b V1 -V - Vin T O/P Waveform I/P Waveform Fig (3) PROCEDURE:1) Study the circuit provided on the front Panel of kit. 2) Apply a +5V; 1 KHz sine wave I/P Vi from function generator. 3) Switch 'ON' the Power Supply. 4) Connect S1 & 1. It is shunt positive clipper. Observe & note Clipping level & amplitude of O/P. 5) Connect S1 & 2. It is shunt biased positive clipper. Observe & note voltage V1. Vary V1 & note Corresponding clipping level & amplitude of O/P as shown fig. 1. 6) Connect S2 & 1. It is shunt negative clipper. Observe & note Clipping level & amplitude of O/P. 7) Connect S2 & 2. It is shunt biased negative clipper. Observe & note voltage V1. Vary V1 & note corresponding clipping level & amplitude of O/P as shown in fig. DEPATRMENT OF ELECTRICAL & ELECTRONICS Page 13 ST. ALOYSIUS INSTITUTE OF TECHNOLOGY, JABALPUR 2015-16 8) Connect S1 & 2, S2 & 2. It is biased combination clipper. Observe & note voltage V1 & V2. Change V1,V2 & note corresponding positive & negative clipping level & amplitude of O/P as shown fig. 3. OBSERVATION:1) For Positive Clipper:I/P positive half cycle amplitude (+V) = -----------V. I/P negative half cycle amplitude (-V) = ------------V. O/P amplitude for positive half cycle of I/P O/P amplitude for negative half cycle of I/P 2) = -----------V. = -----------V. For Positive Biased Clipper:I/P positive half cycle amplitude (+V) = -----------V. I/P negative half cycle amplitude (-V) = ------------V. Note down clipping voltage level for different reference voltage V1 on CRO. Compare clipping level as per given in theory of positive biased clipper. (Fig. 1). 3) 4) For Negative Clipper: I/P positive half cycle amplitude (+V) = -----------V. I/P negative half cycle amplitude (-V) = ------------V. O/P amplitude for positive half cycle of I/P = -----------V. O/P amplitude for negative half cycle of I/P = -----------V. For Negative Biased Clipper:I/P positive half cycle amplitude (+V) = -----------V. I/P negative half cycle amplitude (-V) = ------------V. Note down clipping voltage level for different reference voltage V1 on CRO. Compare clipping level as per given in theory of negative biased clipper. (Fig. 2). 5) For Combination Biased Clipper:I/P positive half cycle amplitude (+V) = -----------V. I/P negative half cycle amplitude (-V) = ------------V. DEPATRMENT OF ELECTRICAL & ELECTRONICS Page 14 ST. ALOYSIUS INSTITUTE OF TECHNOLOGY, JABALPUR 2015-16 Note down positive & negative clipping voltages level for different reference voltage V1 & V2 on CRO. Compare the clipping levels as per given in theory of combination biased clipper. ( Fig. 3). RESULT:By changing the reference voltages +V1 & -V1 clipping level can be changed for Positive, Positive Biased Clipper, Negative, Negative Biased Clipper and Combination Biased Clipper. PRECAUTIONS:1. All connections should be right and tight and as per the circuit diagram. 2. Proper range of measuring instruments should be selected. 3. DEPATRMENT OF ELECTRICAL & ELECTRONICS Page 15 ST. ALOYSIUS INSTITUTE OF TECHNOLOGY, JABALPUR 2015-16 VIVA-VOCE DEPATRMENT OF ELECTRICAL & ELECTRONICS Page 16 ST. ALOYSIUS INSTITUTE OF TECHNOLOGY, JABALPUR __/__/201_ 2015-16 EXPERIMENT NO.-04 AIM:- To study and plot the waveform of Clamper circuit. APPARATUS REQUIRED:S.NO. APPARATUS REQUIRED 1 Trainer Kit TYPE RANGE QUANTITY 2 3 4 THEORY:The process by which the waveform can be shifted to a particular part of it (say positive or negative peak) is called the clamping. The circuit, which performs this function, is called as the clamping circuit or simply a clamper. A clamping circuit introduces (or restores) a DC level to an AC signal. Thus a clamping circuit is also known as DC restorer. These circuits are used in TV receiver to restore the original DC reference signal to the video signal. To study the clamper, it can be classified as 1) Unbiased clamper. 2) Biased clamper. The Unbiased Clamper is classified into 1) Positive clamper. 2) Negative clamper. It is possible to clamp a waveform positively at 0V by connecting a DC battery in series with the source, whose emf is equal to the peak value of the input signal. However, it is a very crude way of achieving the required clamping action and therefore is not used in actual practice. A clamper using a DC battery in series with the source is shown in fig 1. + Vi = VmSinwt V0 Fig 1 DEPATRMENT OF ELECTRICAL & ELECTRONICS Page 17 ST. ALOYSIUS INSTITUTE OF TECHNOLOGY, JABALPUR 2015-16 Positive Clamper:Another clamping circuit using diode is shown in fig 2. The circuit consists of a diode and capacitor C is popularly known as a diode clamper. + V i = VmSinωt V0 Fig 2 The working of the circuit can be understood as follows. When a sine wave is applied at the input then during the negative half cycle of the input voltage (Vi) the diode is forward biased and the current flows through the circuit. As a result of this, the capacitor C is charged to a voltage equal to the negative peak value (i.e.-Vm). Once the capacitor is fully charged to –Vm, it cannot discharge because the diode cannot conduct in reverse direction. That means, the capacitor C acts as a battery with an emf equal to the –Vm. This voltage is then added to the input signal so that the output voltage is equal to the sum of the AC input signal and the capacitor voltage Vm i.e. V0 = Vi + Vm = Vm Sin wt + Vm ---------(1) From equation (1) it is clear that a DC voltage Vm is added to the input signal. This causes the waveform to clamp positively at 0V. Negative Clamper:To clamp the input signal waveform negatively at 0V is called as negative clamper. The circuit diagram is shown in fig 3 C + Vi = VmSinwt D V0 Fig 3 The operation of this circuit is exactly reverse to that of the positive clamper. Here the diode is forward biased during the positive half cycle of the input signal. Therefore the capacitor is charged to DEPATRMENT OF ELECTRICAL & ELECTRONICS Page 18 ST. ALOYSIUS INSTITUTE OF TECHNOLOGY, JABALPUR 2015-16 a voltage equal to the positive peak of the input signal (i.e.Vm), with left plate positive and right plate negative of the capacitor. Hence the output voltage is equal to V0 = Vi – Vm = Vm Sin wt –Vm. -----------------(2) From equation (2) it is clear that a DC voltage Vm is substracted from the input signal. This causes the waveform to clamp negatively at 0V. In unbiased clamper , the clamping level can’t be change for the fixed value of capacitor. So, biased clampers are used. Biased Clamper:Like in clippers, it is possible to have biased clampers. A biased clamper means that the clamping can be done at any voltage level other than zero. If the amplitude of the input signal changes continuously then the practical bias clamper is as shown in fig. 4. C C D R Vi = VmSinWt D V0 Vi = VmSinWt R O/P V0 + VB=V dc VB=V dc + (A) Positive biased clamper (B) negative biased clamper In this circuit a high value resistor is connected in parallel with the diode. The purpose of this resistor is to provide a discharge path for the capacitor. The high value for this resistor is used to produce a time constant, which is large enough than the period of the input signal waveform. For good clamping action, the value of time constant should be at least 10 times the period of the input signal waveform. Fig 4. (A) Shows biased positive clamper & fig (B) shows biased negative clamper. PROCEDURE: 1. Study the circuit provided on the front panel of the kit. 2. Switch ‘ON’ the power supply. 3. Make the connections for positive unbiased clamper by connecting diode D1 in circuit (fig 2). 4. Apply a sine wave of around 1 KHz, 5Vp-p at the input terminals. Note its amplitude and time period. 5. Observe and note the amplitude and clamping level of positive clamped output on the CRO. DEPATRMENT OF ELECTRICAL & ELECTRONICS Page 19 ST. ALOYSIUS INSTITUTE OF TECHNOLOGY, JABALPUR 2015-16 6. Now remove the connections of positive clamper and make connection for negative clamper by connecting diode D2 in ckt. (Fig 3). Repeat step (4) & (5). 7. Now Make the connection for biased positive clamper (diode D1) and observe the input and output waveforms for different biased voltages. Note biased voltage, clamping level and amplitude of O/P. 8. Repeat step (8) for biased negative clamper (diode D2). Input & Output Waveform for Unbiased Clamper:V 0 V 0 2V Vi Vp p Vc 0 t 0 0 Vp -t -t -Vc -2Vp (a) AC Signal (b) Negatively clamped AC Signal (c) Positively clamped AC Signal Input & Output Waveform for Biased Clamper:V0 Clamping at 0V 0 -VB -t Clamping at -VB RESULT:-From the experiment it can be concluded that for a positive clamper the I/P waveform is shifted i.e. positively clamped at a Vc i.e. voltage across capacitor, for a negative clamper the I/P waveform is clamped negatively at a voltage Vc. Similarly, for biased clamper the I/P waveform can be clamped at the desired biased voltage. PRECAUTIONS:1. All connections should be right and tight and as per the circuit diagram. 2. Proper range of measuring instruments should be selected. 3. DEPATRMENT OF ELECTRICAL & ELECTRONICS Page 20 ST. ALOYSIUS INSTITUTE OF TECHNOLOGY, JABALPUR 2015-16 VIVA-VOCE DEPATRMENT OF ELECTRICAL & ELECTRONICS Page 21 ST. ALOYSIUS INSTITUTE OF TECHNOLOGY, JABALPUR __/__/201_ 2015-16 EXPERIMENT NO.-05 AIM:- To study and plot the characteristics of Varactor Diode. APPARATUS REQUIRED:S.NO. APPARATUS REQUIRED 1 Trainer Kit TYPE RANGE QUANTITY 2 3 4 THEORY: A reversed-biased PN-junction can be compared to a charged capacitor. The P and N regions ( away from the space charge region) are essentially low resistance areas due to high concentration of majority carriers. The space-charge region, which is depleted of majority carriers, serves as an effective insulation between the P and N regions. The P and N regions act as the plates of the capacitor while the space-charge region acts as the insulating dielectric. The reverse-biased PNjunction thus has an effective capacitance, whose value is given as: EA C= W where E (the Greek letter “epsilon”) is the permittivity of the semiconductor material, A is the area of the junction, and W is the width of the space-charge region. The width W of the space-charge region is approximately proportional to the square root of the reverse bias voltage V. The area A and permittivity E being constant, we can write Eq. as 𝐶= 𝐾 √𝑉 As the reverse bias increases, the space-charge region becomes wider, thus effectively increasing the plate separation and decreasing the capacitance. Silicon diode optimized for this variable-capacitance effect are called varactors. Fig. shows the two symbols used to represent a varactor diode. It also DEPATRMENT OF ELECTRICAL & ELECTRONICS Page 22 ST. ALOYSIUS INSTITUTE OF TECHNOLOGY, JABALPUR 2015-16 shows graphically how the capacitance of a varactor diode varies with the reverse-bias voltage. Typically, the capacitance variation might be 2-12pF, or 20-28 pF, or perhaps 28-76pF. C Cmax or Symbol Cmin 0 Reverse voltage Fig. Varactor diode characteristic and its symbol. PROCEDURE: 1. Study the circuit arrangement given on front panel of the kit. 2. Switch ON the power supply 3. Connect capacitance meter across “ variable capacitance c’ indicated on front panel of the kit 4. Vary the voltage smoothly and note down capacitance across varactor diode 5. Plot the graph between voltage and capacitance. OBSERVATION: Vi (mV) Variable capacitance (nF) DEPATRMENT OF ELECTRICAL & ELECTRONICS Page 23 ST. ALOYSIUS INSTITUTE OF TECHNOLOGY, JABALPUR 2015-16 RESULT:We have studied characteristics of varactor diode, from which we can conclude that if the Vi increases the barrier capacitance decreases. PRECAUTIONS:1. All connections should be right and tight and as per the circuit diagram. 2. Proper range of measuring instruments should be selected. 3. DEPATRMENT OF ELECTRICAL & ELECTRONICS Page 24 ST. ALOYSIUS INSTITUTE OF TECHNOLOGY, JABALPUR 2015-16 VIVA-VOCE DEPATRMENT OF ELECTRICAL & ELECTRONICS Page 25 ST. ALOYSIUS INSTITUTE OF TECHNOLOGY, JABALPUR __/__/201_ 2015-16 EXPERIMENT NO.-06 AIM:- To Study and plot the characteristics of Zener Diode. APPARATUS REQUIRED:S.NO. APPARATUS REQUIRED 1 Trainer Kit TYPE RANGE QUANTITY 2 3 4 THEORY: A Zener diode shunt regulator is shown in Fig 1. Since the Zener is connected in parallel (or shunt) with the load, the circuit is said to be a shunt regulator. A resistance (RS) is connected in a series to the zener Diode which limit the current in the circuit. Hence it is also known as series current limiting resistor. The output voltage VL is taken across the load resistance RL, which is also the voltage across Zener diode. To observe the proper operation, the input voltage (Vi) must be greater than the Zener Voltage (Vz). Thus ensures that Zener diode operates in the Reverse breakdown Region. The Input Current (I) through Limiting resistor R is given by the relation I = Vi – Vz (1) RS Where Vi = Unregulated DC I/P Voltage to the circuit. DEPATRMENT OF ELECTRICAL & ELECTRONICS Page 26 ST. ALOYSIUS INSTITUTE OF TECHNOLOGY, JABALPUR I R - IL Iz + + Vi Unregulated Reg. O/P Voltage Vz RL - I/P Voltage 2015-16 + Vo - Fig 1:- Zener Diode Vz = Zener Voltage The ideal Zener diode acts as a constant voltage source of voltage (Vz). But a practical zener diode has a finite value of resistance called zener resistance (Rz). Because of the zener resistance, there is a voltage drop across it which is equal to IzRz. Therefore the voltage across the zener diode is given by expression. VL = Vz = IzRz ------------------------- ( 2 ) Let the zener resistance is negligible , then the load voltage is VL = Vz ------------------( 3 ) And the current through the load resistance is given by the relation. IL = VL / RL -----------------------( 4 ) From the circuit it is clear that I = Iz + IL & Iz = I – IL ----------------- ( 5 ) Operation:The operation of the circuit can be discussed under following two heads . 1). Line Regulation with Varying input Voltage:The Load RL is constant & if I/P voltage Vi varies within the limits then the circuit provides constant O/P voltage. As RL is constant . So IL is constant, hence from equation (5) , Iz = I. As the I/P voltage increase, the current I increases so Iz increases within the limits Izmin – Izmax. So zener diode remains in Reverse breakdown state. But the voltage drop across series Resistance R increases therefore keeping the O/P voltage constant at Vz value & Vice Versa. So As the I/P voltage changes within limits O/P remains constant. 2). Load Regulation with varying load Resistance (RL) Consider the operation with Load RL Changes & input voltage Vi constant. As I/P voltage Vi constant so from equation (3) I = Iz + IL, current I is constant so as Iz decreases / increases then IL increases / decreases respectively. If Load Resistance RL decreases then current IL increases , current IZ decreases within limits IZmin – Izmax . So Zener diodes remains in breakdwon thereby keeping a constant O/P voltage equals to Vz value. As the circuit provides a DEPATRMENT OF ELECTRICAL & ELECTRONICS Page 27 ST. ALOYSIUS INSTITUTE OF TECHNOLOGY, JABALPUR 2015-16 constant O/P voltage nearly equal to Vz if input voltage & Load RL changes so it is called as Zener diode shunt voltage regulator. PROCEDURE:1) 2) 3) 4) Study the circuit provided on the front panel of the kit. Connect Zener diode ZD1 of Vz = 6.2V in the circuit. Connect all the voltmeters at the input Vi & O/P Vo side. Connect all the milliammeter at their respective places ( Optional or short the terminals by patchcords) Switch ON the Power Supply . Keep Load Resistance RL constant vary the input voltage Vi from 0 to 12V in steps & note down the corresponding O/P voltage Vo for each step. Now , keep I/P voltages vi constant at the voltage greater than Vz value say Vi = 10V constant, vary the Load RL & note O/P voltage V0 in steps. Keep input Vi = 10v, note RL & R value using digital multimeter. Find current I, IL & Iz from equation (1), (4) & (5) respectively. Repeat the above steps for the other Diode. 5) 6) 7) 8) 9) 10) OBSERVATION:R = ---------, Vz1 = ---------V. Vz2 = ---------V. 1). Line Regulation with RL constant:RL = ___________ K Unregulated I/P (Vi) 2). Regulated (Vo) Load Regulation with Input Vi constant:Vi = ______________V. Load Resistance RL Regulated O/P Vo Min. Med. Max. DEPATRMENT OF ELECTRICAL & ELECTRONICS Page 28 ST. ALOYSIUS INSTITUTE OF TECHNOLOGY, JABALPUR 2015-16 Repeat the above for the other Zener Diode RESULT:The Circuit provides a constant O/P voltage for Zener Diode ZD1, Vo = _________V. If the I/P voltage Vi changes from ______ V to ______V and if RL changes from _____ to ______K. PRECAUTIONS:1. All connections should be right and tight and as per the circuit diagram. 2. Proper range of measuring instruments should be selected. 3. VIVA-VOCE DEPATRMENT OF ELECTRICAL & ELECTRONICS Page 29 ST. ALOYSIUS INSTITUTE OF TECHNOLOGY, JABALPUR __/__/201_ 2015-16 EXPERIMENT NO.-07 AIM:- To study and plot the characteristics of Schottkey Diode. APPARATUS REQUIRED:S.NO. APPARATUS REQUIRED TYPE RANGE 1 Schottkey Diode Trainer Kit 2 CRO 3 Function Generator 4 Power Supply 5 Voltmeter 0-10V 6 Multimeter 0-25mA QUANTITY 1 THEORY:It is also called Schottkey Barrier Diode and Hot-Carrier Diode. It is mainly used as a rectifier at signal frequencies in RF range. It has more uniform junction region and is more rugged than PIN Diode. Construction:- It is a metal semi-conductor junction diode with no depletion layer. It uses a metal (like Gold, Silver, Platinum, Tungsten etc.). On one side of the junction and usually an N- type doped silicon semi-conductor on the other side. The Diode and its schematic symbol in following fig. DEPATRMENT OF ELECTRICAL & ELECTRONICS Page 30 ST. ALOYSIUS INSTITUTE OF TECHNOLOGY, JABALPUR 2015-16 Operation:- When the Diode is unbiased, electron on the N-side have lower energy levels than electron in the metal. Hence, they cannot surmount the junction barrier(called Schottkey Barrier) for going over to the metal. When the Diode is Forward Biased, conduction electrons on the N-side gain enough energy to cross the junction and enter the metal. Since these electrons plunge into the metal with very large energy, they are commonly called ‘Hot Carriers’. That is why this Diode is often referred to as Hot Carrier Diode. The external V-I Characteristics of a schottkey diode is same as that of a P-N Junction diode, but the physical mechanisms involved are most complicated. The voltage drop across schottkey diode is much less than that of a P-N Junction Diode for the same forward current. Thus a cutin voltage of about 0.3V is reasonable for Schottkey Diode as against 0.6V for P-N Junction Diode barrier. Hence the former is closer to the ideal Diode clamp than the latter. This Diode possesses two unique features as compared to an ordinary P-N Junction Diode. It is Unipolar device because it has electrons as majority carriers on both sides of the junction. An ordinary P-N Junction Diode is a bipolar device because it has both electrons and holes as majority carriers. Since no holes are available in metal, there is no depletion layer or stored charges to worry about. Hence diode can switch OFF faster than a bipolar diode. Because of these qualities, Schottkey Diode can easily rectify signals of frequencies exceeding 1MHZ . The figure shown on the front panel of the kit is a Half Wave Rectifier for higher signal frequencies. This can produce an almost Half Wave Rectified output. PROCEDURE:1. Study the circuit provided on front panel of the kit. 2. Apply the sine wave I/P Vi from function generator. Connect the CRO at the O/P VO side. 3. Keep I/P voltage constant (greater than 1V), vary the signal frequency fi from 100HZ to 1MHZ in regular steps and note the corresponding half wave rectified O/P for each signal frequency. Plot the same on the graph. 4. Repeat the above steps for different signal frequencies. DEPATRMENT OF ELECTRICAL & ELECTRONICS Page 31 ST. ALOYSIUS INSTITUTE OF TECHNOLOGY, JABALPUR 2015-16 5. OPTIONAL: The V-I Characteristics of Schottkey Diode can be determined by connecting an external power supply with Anode Positive and Cathode Negative (i.e. in Forward Bias state), connect the milliammeter and voltmeter in the circuit. Now vary the I/P voltage in steps of 0.1V upto 10V and note the corresponding voltage and current of diode. RESULT:- The characteristics of Schottkey Diode as a high frequency Half Wave Rectifier is studied. PRECAUTIONS:1. All connections should be right and tight and as per the circuit diagram. 2. Proper range of measuring instruments should be selected. 3. VIVA-VOCE DEPATRMENT OF ELECTRICAL & ELECTRONICS Page 32 ST. ALOYSIUS INSTITUTE OF TECHNOLOGY, JABALPUR __/__/201_ 2015-16 EXPERIMENT NO.-08 AIM:- To study and plot the characteristics of UJT. APPARATUS REQUIRED:S.NO. APPARATUS REQUIRED 1 Trainer Kit TYPE RANGE QUANTITY 2 3 4 THEORY: This is used in switching circuit. The UJT & SCR are the most efficient of the devices which undertake this work. These devices have impedance in OFF condition under forward bias until the signal is applied. After switching ON their impedance decreases shortly. UJT is original called as double based diode & also known as filamentary transistor. B2 Base Emitter B2 E DEPATRM TRICAL & ELECTRONICS E E N T O F E LPE C N Page 33 ST. ALOYSIUS INSTITUTE OF TECHNOLOGY, JABALPUR 2015-16 In consists of a lightly doped silicon bar with a heavily doped P-type material attached to it firmly, closer to end B2, producing a single P.N. junction. There are three terminals, emitter E formed by the P-material, B1 & B2. At the bottom and the top of the silicon bar, the arrow is in the direction of the convention current. The emitter connection is shown at an angle to the vertical. The inter-base resistance is the resistance between B2 & B1 i.e. the total resistance of the bar from end B2 to end B1 with the emitter open. B2 Equivalent Circuit B2 Emitter P + VBB RB2 A E E P N N A RB1 RBB B1 B1 Fig (b) From the equivalent circuit shown fig (b) RBB = RB2 + RB1 . As already pointed out RB1 B2A > B1A so that RB2 3 2 potential at point A. is VA = RB1 RB1+ RB2 .VBB DEPATRMENT OF ELECTRICAL & ELECTRONICS Page 34 ST. ALOYSIUS INSTITUTE OF TECHNOLOGY, JABALPUR RB1 RB1+ RB2 = Let 2015-16 Called intrinsic stand OFF ratio. So VA = VBB As VBB is applied, VA is developed between point A & B1. This reverse biases the junction . If the barrier voltage of the P.N. junction is VB ,the total reverse bias voltage equal VA + VB = VBB + VB. For silicon VB is 0.7v . Hence emitter junction will not be forward biased unless it is applied voltage VE > VBB + VB. This value of VE is called peak point voltage VP. Operation of Circuit : 1) First keep VBB = 0 and Increase the ammeter Voltage VE & note corresponding emitter current IE for every steps of VE. 2) Now keep VBB >0 nearly about 15v , the Emitter voltage VE is increased in steps & every time the corresponding ammeter current is to be noted. Initially in cut OFF region as VE increases from Zero slight leakage current flows from terminal B2 to the emitter. This current is due to the minority carriers in the reverse biased diode. I E begins to flow & increasing till the Peak voltage Vp & current Ip is reached. After this VE falls down with increase in IE . Hence this region is called negative resistance region. This region extends till values point the region beyond valley point is called saturation region. The nature of graph will be as shown below. Negative Cut off resistance region VP region Saturation region Valley point VE VV Leakage PROCEDURE: 1) 2) 3) 4) Ip Iv IE current Study the circuit provided on front panel of kit. Set VBB = 0. Connect the Ammeter & voltmeter at their respective places. Connect VE and gradually increase the VE = VEB voltage. DEPATRMENT OF ELECTRICAL & ELECTRONICS Page 35 ST. ALOYSIUS INSTITUTE OF TECHNOLOGY, JABALPUR 2015-16 5) Note down VBE1 & IE (Emitter current). Plot the graph between IE & VE. 6) Now set VBB > 0 such as VBB = 5v, 10, 15v etc. & repeat the step 4 & 5. OBSERVATIONS:1) VBB = 0 Sr. No 2) VEB1 IE (mA) VEB1 IE VBB = 15 V. Sr. No RESULT: For the UJT 2N2646 , peak point voltage & valley voltage is found be respectively. ___ & ____ PRECAUTIONS:1. All connections should be right and tight and as per the circuit diagram. 2. Proper range of measuring instruments should be selected. 3. DEPATRMENT OF ELECTRICAL & ELECTRONICS Page 36 ST. ALOYSIUS INSTITUTE OF TECHNOLOGY, JABALPUR 2015-16 VIVA-VOCE DEPATRMENT OF ELECTRICAL & ELECTRONICS Page 37 ST. ALOYSIUS INSTITUTE OF TECHNOLOGY, JABALPUR __/__/201_ 2015-16 EXPERIMENT NO.-09 AIM:- To study and plot the characteristics of JFET. APPARATUS REQUIRED:S.NO. APPARATUS REQUIRED 1 Trainer Kit TYPE RANGE QUANTITY 2 3 4 THEORY: The field effect transistor (FET) is a three terminal unipolar solid state device in which the current is controlled by an electric field as in vacuum tube. It is classified as 1) Junction field-effect transistor (JFET). 2) Metal oxide semiconductor field-effect transistor (MOSFET) or insulated gate field effect transistor (IGFET).The JFET can be divided depending upon their structure as follows. 1) N-channel JFET. DEPATRMENT OF ELECTRICAL & ELECTRONICS Page 38 ST. ALOYSIUS INSTITUTE OF TECHNOLOGY, JABALPUR 2015-16 2) P-channel JFET. D N-type Ptttttttt ype type G D N-type P-type P-type N-type G S S The construction of an N-channel & P-channel JFET is shownP-inChannel fig (1). N- Channel The N-channel JFET consists of an N-type semiconductor bar with two P-type heavily doped regions diffused on opposite sides of its middle part. The P-type regions form two PN junctions. The space between the junctions (i.e. N-type region) is called the channel. Both P-type regions are connected internally and a single wire is taken out in the form of a terminal called the gate (G). Other two terminals are called drain (D) and source (S). The drain (D) is the terminal through which electrons leave the semiconductor bar and source S is a terminal through which the electrons enter the semiconductor. Whenever a voltage is applied across the drain and source terminals, a current flow through the N-channel. The current consists of only one of carrier (i.e. electrons). Therefore the field-effect transistor is called a unipolar device. Symbol of N-channel and P-channel JFET are as shown in fig (2). below. D D G + G + _ _ VGG1 VDD ID _ _ VDD VGG2 + + S DEPATRMENT OF ELECTRICAL & ELECTRONICS S Page 39 ST. ALOYSIUS INSTITUTE OF TECHNOLOGY, JABALPUR 2015-16 Characteristics of JFET: 1) V.I. or Drain Characteristics :These curve give relationship between the drain current (ID) and drain to source voltage (VDS) for different values of gate to source voltage (VGS). To obtain the characteristic, first of all adjust the gate-to-source voltage (VGS) to zero volt. Then increase the drain-to-source voltage (VDS) in small suitable steps and record the corresponding values of drain current (ID) at each step. Now, if a graph is plotted with VDS along x axis and drain current along the Y axis, a curve marked VGS=0 is obtained as shown in fig (4). A similar procedure may be used to obtain curve for different values of VGS = -1,-2,-3 and –4. ID VGS =0 VGS =-1V VGS =-2V VGS =-3V VGS =-4V 0 VDS Fig.4 Drain Characteristics 2) Transfer characteristics: This curve gives the relationship between drain current (ID) and gateto-source voltage (VDS). To obtain this curve, keep the VDS voltage to a suitable fix voltage. Then increase the gate-to-source in small suitable steps. Now if a graph is plotted with V GS along the x axis and drain current (ID) along y-axis, a curve is obtained as shown in fig (5). A similar procedure may be used to obtain curve at different values of gate-to-source voltage (VGS). IDSS Drain current ID (mA) VGS (off) =VP 0 D E P A T R M E N T O F E L E C T R I-V CGSA L & E L E C T R O N I C S Page 40 ST. ALOYSIUS INSTITUTE OF TECHNOLOGY, JABALPUR 2015-16 The upper end of the curve is shown by the drain current value equal to IDSS, while lower end is indicated by voltage equal to VGS (off) or Vp. It may be noted that the curve is part of a parabola and expressed by the equation. PROCEDURE:A. For Drain Characteristics. 1) Study the circuit provided on the front panel of the kit. 2) Connect the milliammeter and voltmeters at the respective places. 3) Keep the VGG and VDD at minimum positions. 4) Switch ‘ON’ the power supply. 5) Keep the VGS at fix value say VGS =0 V. 6) Now increase the VDD in steps and note down the readings of ID and VDS with the 0.5 V interval of VDS. 7) Plot the graph with VDS along X-axis and ID along Y-axis. 8) Repeat steps 6 to 8 for different values of VGS. B. For transfer characteristics. a) Keep the VDS at constant voltage say VDS = 1 V. b) Now increase the value VGG and note the readings of ID and VGS with the 1 V intervals of VGS. c) Plot the graph with VGS along X-axis and ID along Y-axis. d) Repeat steps (a), (b), (c) for different values of VDS. OBSERVATIONS :1) For drain characteristics. VGS = 0V : VGS = -1V Sr. No. : VGS = -2V : VGS = -3V : VDS (V) VGS = -4V ID (mA) DEPATRMENT OF ELECTRICAL & ELECTRONICS Page 41 ST. ALOYSIUS INSTITUTE OF TECHNOLOGY, JABALPUR 2015-16 2) Transfer Characteristics : VD S = --------------- V (Constant) Sr. No. VGS (V) ID (mA) RESULT: The Drain & Transfer char. of JFET has been studied. From the expt. it can be conclude that the depletion layer increases and decreases as the gate to source voltage is reduced & increased respectively. PRECAUTIONS:1. All connections should be right and tight and as per the circuit diagram. 2. Proper range of measuring instruments should be selected. 3. DEPATRMENT OF ELECTRICAL & ELECTRONICS Page 42 ST. ALOYSIUS INSTITUTE OF TECHNOLOGY, JABALPUR 2015-16 VIVA-VOCE DEPATRMENT OF ELECTRICAL & ELECTRONICS Page 43 ST. ALOYSIUS INSTITUTE OF TECHNOLOGY, JABALPUR __/__/201_ 2015-16 EXPERIMENT NO.-10 AIM:- To study and plot the characteristics of MOSFET. APPARATUS REQUIRED:S.NO. APPARATUS REQUIRED 1 Trainer Kit TYPE RANGE QUANTITY 2 3 4 5 DEPATRMENT OF ELECTRICAL & ELECTRONICS Page 44 ST. ALOYSIUS INSTITUTE OF TECHNOLOGY, JABALPUR 2015-16 THEORY:The MOSFET is an abbreviation for Metal-Oxide Semiconductor Field-Effect Transistor. Like JFET it has source (S), gate (G) & drain (D). However unlike JFET, the gate of a MOSFET is insulated from the channel, because of this, the MOSFET is sometimes known as IGFET (Insulated Gate Field Effect Transistor). Basically the MOSFETs are of two types namely Depletion type MOSFET & Enhancement type MOSFET. The device operates in the depletion mode when the gate voltage is negative. The device operates in Enhancement mode when the gate voltage is positive. Depletion type MOSFET can be operated in either depletion or enhancement mode therefore it is also called as Depletion – enhancement (DE) type MOSFET. Enhancement-type MOSFET: The enhancement-type MOSFET has no depletion mode and it operates only in enhancement mode. It differs in construction from the depletion -type MOSFET in the sense that it has no physical channel. Fig. (1) shows the basic structure of the N-channel enhancement type MOSFET.. DEPATRMENT OF ELECTRICAL & ELECTRONICS Page 45 ST. ALOYSIUS INSTITUTE OF TECHNOLOGY, JABALPUR 2015-16 Fig. (1) Shows the normal biasing polarities for the N-channel enhancement-type D Drain D SiO2 Layer N N + Gate G P P VDD G + N N VGG S S Source (a) Basic construction (b) Formation of invertion layer. Fig.1: Enhancement type MOSFET Drain characteristics for Enhancement-type MOSFET:-Fig (2) (a) shows the drain characteristics for N-channel Enhancement-type MOSFET. It may be noted from this figure, that the gate-to-source voltage (VGS) is less than Threshold voltage VGS(th), there is no drain current. However, in actual practice, an extremely small value of drain current does flow through the MOSFET. This current DEPATRMENT OF ELECTRICAL & ELECTRONICS Page 46 ST. ALOYSIUS INSTITUTE OF TECHNOLOGY, JABALPUR 2015-16 flow is due to the presence of thermally generated electrons in the P-type substrate. When the value of VGS is kept above VGS(Th), a significant drain current flows. The values of drain current increases with the increases in gate-to-source voltage. It is because of the fact that the width of inversion layer widen of increased value of VGS and therefore allows more number of free electrons to pass through it. The drain current reaches its saturation value above a certain value of drain-to-source voltage (VDS). VGS1 > VGS2 > VGS3 > VGS(th) VGS = VGS1 VGS2 Drain current Drain current I D (A) ID (A) VGS3 VGS(th) VGS = VGS(th) 0 Drain-to-source 0 voltage (VDS)V (a) Drain characteristics Fig. 2:- Gate -to-source voltage (VGS)V (b) Transfer characteristics Characteristics for N-channel enhancement-type MOSFET. Transfer Characteristic for Enhancement-type MOSFET: Fig.(2) (b) shows the transfer characteristic for N-channel enhancement type MOSFET. It may be noted from this figure that there is no drain current when the gate-to-source voltage, VGS = 0. However, if VGS is increases rapidly as shown in figure. The relation gives the drain current at any point along the curve, ID = K [VGS – VGS (th)]2 Where K is a constant, whose value depends on the type of MOSFET. Its value can be determined from the data sheet by taking specified value of drain current called ID(ON) at the given value of VGS DEPATRMENT OF ELECTRICAL & ELECTRONICS Page 47 ST. ALOYSIUS INSTITUTE OF TECHNOLOGY, JABALPUR and then substituting these values in the above equation. 2015-16 Incidentally, it may be noted that enhancement-type MOSFET does not have an IDSS parameter like JFET and depletion-type MOSFET. PROCEDURE:(1) Study the circuit provided on the front panel of the Kit. (2) Connect voltmeter VGS, VDS and milliammeter ID in the circuit as shown. (3) Keep VGS = 0, Vary VDD, note VDS & ID for each step. (4) Repeat steps (3) for VGS = + 1V, VGS = + 2V, VGS = VGS (th) etc. (5) From step (4), find the minimum gate-to-source voltage VGS called as threshold voltage VGS (th) for which significant value of current ID flows. Plot a drain character between VDS on X-axis, ID on Y-axis for fixed values of VGS. (6) Keep VDD = constant (say 12 V) vary VGG in steps & note corresponding VGS & ID. Plots a Transfer characteristic between VGS on X-axis ID on Y-axis. OBSERVATION:(1) Drain Characteristics VGS = constant VDD VDS V V ID mA 0 1 (2) Repeat above steps for different values of VGS say 1V, 2V etc. (3) Transfer Characteristics VDD = constant VGG VGS ID V V mA 0 0.1 0.2 DEPATRMENT OF ELECTRICAL & ELECTRONICS Page 48 ST. ALOYSIUS INSTITUTE OF TECHNOLOGY, JABALPUR 2015-16 RESULT: The Enhancement type N-channel MOSFET becomes ‘ON’ when gate voltage applied VGS (th) is positive VGS & is found to be --------V. PRECAUTIONS:1. All connections should be right and tight and as per the circuit diagram. 2. Proper range of measuring instruments should be selected. 3. DEPATRMENT OF ELECTRICAL & ELECTRONICS Page 49 ST. ALOYSIUS INSTITUTE OF TECHNOLOGY, JABALPUR 2015-16 VIVA-VOCE DEPATRMENT OF ELECTRICAL & ELECTRONICS Page 50