Logic gate - WordPress.com

advertisement

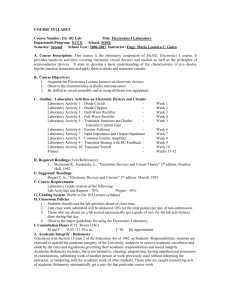

REPUBLIC OF YEMEN Saba University Collage of Engineering & Computer Communication Department Prepared by Youssef Ali Saleh Asssggaf Supervised by Teacher Mohammad Al Jarban. June 2008 Introduction There are two kinds of Electronic circuit ( Analog & Digital ). Electronic circuit was Analog but now Electronic Digital circuits are become more vulgar . even in Electronic Analog circuit Applications . In 30 years ago, all When we talk about Electronic Digital Circuit we should know some information about Logic Circuit & Logic Gates which used binary numbers (1-0). So, I was starts in this research with some of the important information about Logic Circuits and Logic Family. This research is prepared in 10/06/2008 AD by Youssef Ali Saleh Asssggaf and supervised by Teacher Mohammad Al Jarban. We will talk about: Logic Gate Logic Family Diode logic (DL) Direct-coupled transistor logic (DCTL) Resistor-transistor logic (RTL) Diode-transistor logic (DTL) Emitter coupled logic (ECL) also known as Current-mode logic (CML) Transistor-transistor logic (TTL) and variants P-type Metal Oxide Semiconductor logic (PMOS) N-type Metal Oxide Semiconductor logic (NMOS) Complementary Metal-Oxide Semiconductor logic (CMOS) I hope that you got benefit and enjoy with it . Youssef Assaggaf Logic gate A logic gate performs a logical operation on one or more logic inputs and produces a single logic output. Because the output is also a logic-level value, an output of one logic gate can connect to the input of one or more other logic gates. The logic normally performed is Boolean logic and is most commonly found in digital circuits. Logic gates are primarily implemented electronically using diodes or transistors, but can also be constructed using electromagnetic relays, fluidics, optics, or even mechanical elements. In electronic logic, a logic level is represented by a voltage or current, (which depends on the type of electronic logic in use). Each logic gate requires power so that it can source and sink currents to achieve the correct output voltage. In logic circuit diagrams the power is not shown, but in a full electronic schematic, power connections are required. Truth table A truth table is a table that describes the behaviour of a logic gate. It lists the value of the output for every possible combination of the inputs and can be used to simplify the number of logic gates and level of nesting in an electronic circuit. In general the truth table does not lead to an efficient implementation; a minimization procedure, using Karnaugh maps, the Quine– McCluskey algorithm or a heuristic algorithm is required for reducing the circuit complexity. Background The simplest form of electronic logic is diode logic. This allows AND and OR gates to be built, but not inverters, and so is an incomplete form of logic. Further, without some kind of amplification it is not possible to have such basic logic operations cascaded as required for more complex logic functions. To build a complete logic system, valves (vacuum tubes) or transistors can be used. The simplest family of logic gates using bipolar transistors is called resistor-transistor logic, or RTL. Unlike diode logic gates, RTL gates can be cascaded indefinitely to produce more complex logic functions. These gates were used in early integrated circuits. For higher speed, the resistors used in RTL were replaced by diodes, leading to diode-transistor logic, or DTL. It was then discovered that one transistor could do the job of two diodes in the space of one diode even better, by more quickly switching off the following stage, so transistor-transistor logic, or TTL, was created. In virtually every type of contemporary chip implementation of digital systems, the bipolar transistors have been replaced by complementary field-effect transistors (MOSFETs) to reduce size and power consumption still further, thereby resulting in complementary metal-oxidesemiconductor (CMOS) logic. For small-scale logic, designers now use prefabricated logic gates from families of devices such as the TTL 7400 seriesby Texas Instruments and the CMOS 4000 series by RCA, and their more recent descendants. Increasingly, these fixed-function logic gates are being replaced by programmable logic devices, which allow designers to pack a large number of mixed logic gates into a single integrated circuit. The field-programmable nature of programmable logic devices such as FPGAs has removed the 'hard' property of hardware; it is now possible to change the logic design of a hardware system by reprogramming some of its components, thus allowing the features or function of a hardware implementation of a logic system to be changed. Electronic logic gates differ significantly from their relay-and-switch equivalents. They are much faster, consume much less power, and are much smaller (all by a factor of a million or more in most cases). Also, there is a fundamental structural difference. The switch circuit creates a continuous metallic path for current to flow (in either direction) between its input and its output. The semiconductor logic gate, on the other hand, acts as a high-gain voltage amplifier, which sinks a tiny current at its input and produces a low-impedance voltage at its output. It is not possible for current to flow between the output and the input of a semiconductor logic gate. Another important advantage of standardised integrated circuit logic families, such as the 7400 and 4000 families, is that they are cascadable. This means that the output of one gate can be wired to the inputs of one or several other gates, and so on. Systems of arbitrary complexity can be built without great concern of the designer for the internal workings of the gates, provided the limitations of each integrated circuit are considered. The output of one gate can only drive a finite number of inputs to other gates, a number called the 'fanout limit'. Also, there is always a delay, called the 'propagation delay', from a change in input of a gate to the corresponding change in its output. When gates are cascaded, the total propagation delay is approximately the sum of the individual delays, an effect which can become a problem in high-speed circuits. Additional delay can be caused when a large number of inputs are connected to an output, due to the distributed capacitance of all the inputs and wiring and the finite amount of current that each output can provide. Logic gates and hardware NAND and NOR logic gates are the two pillars of logic, in that all other types of Boolean logic gates (i.e., AND, OR, NOT, XOR, XNOR) can be created from a suitable network of just NAND or just NOR gate(s). They can be built from relays or transistors, or any other technology that can create an inverter and a two-input AND or OR gate. Hence the NAND and NOR gates are called the universal gates. For an input of 2 variables, there are 16 possible boolean algebraic functions. These 16 functions are enumerated below, together with their outputs for each combination of inputs variables. A B 0 A AND B A>B* A A<B* B A XOR OUTP B UT A OR B A NOR B A XNOR B NOT B A≥B* NOT A INPU T 0011 0101 0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 1010 1011 1100 A≤B* A NAND B 1 1101 1110 1111 The four functions labeled with a "*" are the logical implication functions: "A ≤ B" can be read as "A implies B"; it follows that "A > B" is "A does not imply B". These four functions are less common and are usually not implemented directly as logic gates. Symbols A synchronous 4-bit up/down decade counter symbol (74LS192) in accordance with ANSI/IEEE Std. 91-1984 and IEC Publication 60617-12. There are two sets of symbols in common use, both now defined by ANSI/IEEE Std 911984 and its supplement ANSI/IEEE Std 91a1991. The "distinctive shape" set, based on traditional schematics, is used for simple drawings and is quicker to draw by hand. It is sometimes unofficially described as "military", reflecting its origin if not its modern usage. The "rectangular shape" set, based on IEC 60617-12, has rectangular outlines for all types of gate, and allows representation of a much wider range of devices than is possible with the traditional symbols. The IEC's system has been adopted by other standards, such as EN 60617-12:1999 in Europe and BS EN 60617-12:1999 in the United Kingdom. The goal of IEEE Std 91-1984 was to provide a uniform method of describing the complex logic functions of digital circuits with schematic symbols. These functions were more complex than simple AND and OR gates. They could be medium scale circuits such as a 4-bit counter to a large scale circuits such as a microprocessor. The 1984 version did not include the "distinctive shape" symbols.[1] These were added to the 1991 supplement with this note: "The distinctiveshape symbol is, according to IEC Publication 617, Part 12, not preferred, but is not considered to be in contradiction to that standard." In the 1980s, schematics were the predominant method to design both circuit boards and custom ICs known as gate arrays. Today custom ICs and the field-programmable gate array are typically designed with Hardware Description Languages (HDL) such as Verilog or VHDL. The need for complex logic symbols has diminished and distinctive shape symbols are still the predominate style. Typ e Distinctive shape Rectangular shape Boolean algebra between A &B Truth table INP UT A B 0 0 1 1 0 1 0 1 AN D OUTP UT A AND B 0 0 0 1 INP UT OR A+B A B 0 0 1 1 0 1 0 1 INP UT NO A T 0 1 OUTP UT A OR B 0 1 1 1 OUTP UT NOT A 1 0 In electronics a NOT gate is more commonly called an inverter. The circle on the symbol is called a bubble, and is generally used in circuit diagrams to indicate an inverted (active-low) input or output.[1][2] INP UT A NA ND 0 0 1 1 OUTPU T A B NAND B 0 1 1 1 0 1 1 0 INP UT A B 0 0 1 1 0 1 0 1 NO R OUTP UT A NOR B 1 0 0 0 In practice, the cheapest gate to manufacture is usually the NAND gate. Additionally, Charles Peirce showed that NAND gates alone (as well as NOR gates alone) can be used to reproduce the functions of all the other logic gates. The 7400 chip, containing four NANDs. The two additional pins supply power (+5 V) and connect the ground. Two more gates are the exclusive-OR or XOR function and its inverse, exclusive-NOR or XNOR. The two input Exclusive-OR is true only when the two input values are different, false if they are equal, regardless of the value. If there are more than two inputs, the gate generates a true at its output if the number of trues at its input is odd ([2]). In practice, these gates are built from combinations of simpler logic gates. INP UT XOR A B 0 0 1 1 0 1 0 1 OUTP UT A XOR B 0 1 1 0 INP UT A XNOR 0 0 1 1 OUTPU T A B XNOR B 0 1 1 0 0 0 1 1 DeMorgan equivalent symbols By use of De Morgan's theorem, an AND gate can be turned into an OR gate by inverting the sense of the logic at its inputs and outputs. This leads to a separate set of symbols with inverted inputs and the opposite core symbol. These symbols can make circuit diagrams for circuits using active low signals much clearer and help to show accidental connection of an active high output to an active low input or vice-versa. Symbolically, a NAND gate can also be shown using the OR shape with bubbles on its inputs, and a NOR gate can be shown as an AND gate with bubbles on its inputs. The bubble signifies a logic inversion. This reflects the equivalency due to De Morgans law, but it also allows a diagram to be read more easily, or a circuit to be mapped onto available physical gates in packages easily, since any circuit node that has bubbles at both ends can be replaced by a simple bubble-less connection and a suitable change of gate. If the NAND is drawn as OR with input bubbles, and a NOR as AND with input bubbles, this gate substitution occurs automatically in the diagram (effectively, bubbles "cancel"). This is commonly seen in real logic diagrams - thus the reader must not get into the habit of associating the shapes exclusively as OR or AND shapes, but also take into account the bubbles at both inputs and outputs in order to determine the "true" logic function indicated. Storage of bits Related to the concept of logic gates (and also built from them) is the idea of storing a bit of information. None of the gates discussed up to here can store a value by itself: when the inputs change, the outputs immediately react. It is possible to make a storage element either through a capacitor (which stores charge due to its physical properties) or by feedback. Connecting the output of a gate to the input causes it to be put through the logic again, and choosing the feedback correctly allows it to be preserved or modified through the use of other inputs. A set of gates arranged in this fashion is known as a "latch", and more complicated designs that utilize clocks (signals that oscillate with a known period) and change only on the rising edge are called edgetriggered "flip-flops". The combination of multiple flip-flops in parallel, to store a multiple-bit value, is known as a register. When using any of these gate setups the overall system has memory; it is then called a sequential logic system since its output can be influenced by its previous state(s). These registers or capacitor-based circuits are known as computer memory. They vary in performance, based on factors of speed, complexity, and reliability of storage, and many different types of designs are used based on the application. Logic family In computer engineering, a logic family may refer to one of two related concepts. A logic family of monolithic digital integrated circuit devices is a group of electronic logic gates constructed using one of several different designs, usually with compatible logic levels and power supply characteristics within a family. Many logic families were produced as individual components, each containing one or a few related basic logical functions, which could be used as "building-blocks" to create systems or as so-called "glue" to interconnect more complex integrated circuits. A "logic family" may also refer to a set of techniques used to implement logic within large scale integrated circuits such as a central processor, memory, or other complex function. Some such logic families, such as Complementary Pass-transistor Logic, use static techniques. Other such logic families, such as domino logic, use clocked dynamic techniques to minimize size, power consumption, and delay. Before the widespread use of integrated circuits, various solid-state and vacuum-tube logic systems were used but these were never as standardized and interoperable as the integrated circuit devices. The beginning The list of packaged building-block logic families can be divided into categories, listed here in rough chronological order of introduction along with their usual abbreviations: Diode logic (DL) Direct-coupled transistor logic (DCTL) Complementary transistor logic (CTL) Resistor-transistor logic (RTL) Resistor-capacitor transistor logic (RCTL) Diode-transistor logic (DTL) Emitter coupled logic (ECL) also known as Current-mode logic (CML) Transistor-transistor logic (TTL) and variants P-type Metal Oxide Semiconductor logic (PMOS) N-type Metal Oxide Semiconductor logic (NMOS) Complementary Metal-Oxide Semiconductor logic (CMOS) Bipolar Complementary Metal-Oxide Semiconductor logic (BiCMOS) Integrated Injection Logic (I2L) The families (DL, RTL, DTL, and ECL) were derived from the logic circuits used in early computers, originally implemented using discrete components. One example is the Philips NORbits family of logic building blocks. The PMOS and I2L logic families were used for relatively short periods, mostly in special purpose custom LSI (Large Scale Integrated Circuits) devices and are generally considered obsolete. For example, early digital clocks or electronic calculators may have used one or more PMOS devices to provide most of the logic for the finished product. The F14 CADC, Intel 4004, Intel 4040, and Intel 8008 microprocessors and their support chips were PMOS. Of these families, only five (ECL, TTL, CMOS, NMOS, and BiCMOS) are currently still in widespread use. ECL is used for very high speed applications because of its price and power demands, while NMOS logic is mainly used in VLSI (Very Large Scale Integrated Circuits) applications such as CPUs and memory chips which fall outside of the scope of this article. Present-day "building block" logic gate ICs are based on the ECL, TTL, CMOS, and BiCMOS families. Monolithic integrated circuit logic families table The following logic families would either have been used to build up systems from functional blocks such as flip-flops, counters, and gates, or else would be used as "glue" logic to interconnect very-large scale integration devices such as memory and processors. Not shown are some early obscure logic families from the early 1960's such as direct-coupled transistor logic, which did not become widely available.. Power Typical Toggl per gate supply Fa Descriptio Propagati e speed @1 MHz voltage V Introducti mily n on delay (ns) (MHz) (mW) (range) on year RT Resistor__ 4 10 3.3 1963 L transistor logic DT Diode__ __ 10 5 1962 L transistor logic CM AC/ACT 3 125 0.5 CM HC/HCT 9 30 0.5 4000B/74 30 5 1.2 OS 3.3 or 5 (2-6 or 4.5 to 5.5) 5 (2-6) 1985 10V (3- 1970 1982 OS CM OS C 18) TT L Original series TT L 10 25 10 33 3 1 TT H 6 43 22 TT S 3 110 19 TT LS 10 33 2 TT ALS 4 34 1.3 TT F 3.5 100 5.4 TT AS 2 105 8 TT AS 2 105 8 EC ECL III 1 500 60 EC MECL I 8 EC ECL 10K 2 125 25 EC ECL 100K .75 350 40 L L L L L L L L L 31 5 (4.755.25) 5 (4.755.25) 5 (4.755.25) 5 (4.755.25) 5 (4.755.25) 5 (4.55.5) 5 (4.755.25) 5 (4.55.5) 5 (4.55.5) -5.2(5.19 - -5.21) -5.2 1964 -5.2(5.19 - -5.21) -4.5(-4.2 - -5.2) 1971 L HCT has TTL compatible levels Approximately half speed and power at 5 volts Several manufacturers 1964 Low power 1964 High speed 1969 Schottky high speed 1976 1979 Low power Schotky high speed Advanced Low power Schottky Fast 1980 Advanced Schottky 1980 Advanced Schottky 1968 Improved ECL 1976 1962 L L Remarks the first CPU built from integrated circuits (the AGC) used RTL. Introduced by Signetics, Fairchild 930 line became industry standard in 1964 ACT has TTL Compatible levels 1981 first integrated logic circuit commercially produced Motorola EC L L ECL 100KH EC ECL 100K 1 250 25 .75 350 40 -5.2(-4.9 - -5.5) -4.5(-4.2 - -5.2) 1981 1981 Diode logic Diode logic or Diode-resistor logic, is a circuit style that uses diodes to construct Boolean logic gates for circuits. Only non-inverting functions may be implemented, so it is not a complete logic family. Furthermore, such circuits are non-restoring: the output of any gate is further from a perfect 0 or 1 than the input, so only a few gates may be chained together. For these reasons, such circuits do not qualify as digital logic. Nevertheless, some gates may be constructed in the style of a digital logic family. Pure diode logic has never been popular, as it has almost no advantages besides extreme simplicity. None of these things are true of diode–transistor logic. Overview A logic gate should act as a voltage source, and provide one of two voltage levels to represent the Boolean logic result. Diode-resistor gates work by using any of an array of diodes to drive one of these levels, and if all the diodes are off, allowing a resistor to drive the output instead. The resistor is always on, but any diode acting as a voltage source will override it. Non-restoring logic Digital logic is characterized by signal restoration. True and false or 1 and 0 are represented by two specific voltage levels. If the inputs to a digital logic gate is close their respective levels, the output will be closer or exactly equal to its desired level. Gates may be integrated in large numbers because each gate tends to remove noise at its input. Diodes and resistors cannot remove noise, and diodes always add noise. The p-n junction in a diode ceases to conduct at less than a certain voltage difference. This voltage difference, typically 0.6—0.8 V, is added to or subtracted from the input of every gate. The feasible number of logic stages thus depends on the difference between the high and low voltages. Unlike true logic families, diode-resistor gates use the inputs as a voltage source to drive the output. A voltage source is characterized by its electrical resistance. Other voltage sources in diode logic are implemented by resistors. To work properly, the inputs must be better voltage sources than the resistors. If a weak source (for example, another large resistor) is connected to the input, the gate's resistor will continue to override the weakened diode. No inversion Diodes ideally pass the input voltage directly to the output when turned on. The only way to achieve an output opposite to the input is to disconnect all the diodes and use only the resistor. There is no way to use the resistor only when an input is applied, nor to obtain a voltage from the diode which isn't a constant difference from the input. Current switching One sense where diodes are superior to transistors is in handling large currents. If voltage is neglected, diodes are good at forming OR gates for multiple current sources. OR gate construction Diode OR gate: example with two inputs To construct an OR gate with n logic inputs, the following components are required: n diodes a resistor of much more resistance than anything you wish to turn the gate on n + 2 electrical nodes are used (counting ground as a node). The circuit of a two-input gate is shown opposite. The cathode of every diode is connected to the output at Node 1. A resistor connects Node 1 to ground (low voltage, Node 2), and the remaining n nodes are the inputs. Whenever a logic 1 is present at the anode of a diode, it forward-biases that diode, causing it to conduct. The input can then induce a current at the output through the diode, to cause the output voltage to be closer to 1. If a logic 0 is present at the anode of every diode, they are all reverse-biased and the resistor drives node 1 low. AND gate construction Diode AND gate: example with two inputs To construct an AND gate with n logic inputs, the following components are required: n diodes a resistor of much more resistance than anything you wish to turn the gate off An example circuit is shown on the right. The resistor connects Node 1 to a the supply voltage at Node 2. Nodes 4 and 5 are the inputs. The output is obtained at Node 1. If a logic 1 is present at the cathode of every diode, then they are all reverse biased, remaining in a high-impedance state, and Node 1 is held high by the power supply through the resistor. If a logic 0 is present at any input, it forward-biases that diode and may hold Node 1 low through the diode. Direct-coupled transistor logic A special type of RTL logic. A DCTL gate is one wherein the bases of the transistors are connected directly to inputs without any base resistors. Without the base resistors, DCTL gates are more economical and simpler to fabricate onto integrated circuits than RTL gates with base resistors. Resistor–transistor logic Schematic of basic two-input RTL NOR gate. Resistor–transistor logic (RTL) is a class of digital circuits built using resistors as the input network and bipolar junction transistors (BJTs) as switching devices. RTL is the earliest class of transistorized digital logic circuit used; other classes include diode–transistor logic (DTL) and transistor–transistor logic (TTL). Contents 1 Function 2 Advantages 3 Limitations 4 Speeding up RTL Function In Transistor Component Circuits IBM informs us, “The logical function is performed by the input resistor network and the invert function is accomplished by the common emitter transistor configuration.” Advantages The primary advantage of RTL technology was that it involved a minimal number of transistors, which was an important consideration before integrated circuit technology, as transistors were the most expensive component to produce. Early IC logic production (such as Fairchild's in 1961) used the same approach briefly, but quickly transitioned to higherperformance circuits such as diode–transistor logic and then transistor–transistor logic (starting 1963 at Sylvania), since diodes and transistors were no more expensive than resistors in the IC. Limitations The obvious disadvantage of RTL is its high current dissipation when the transistor conducts to overdrive the output biasing resistor. This requires that more current be supplied to and heat be removed from RTL circuits. In contrast, TTL circuits minimize both of these requirements. Lancaster says that integrated circuit RTL NOR gates (which have one transistor per input) may be constructed with "any reasonable number" of logic inputs, and gives an example of an 8input NOR gate. A standard integrated circuit RTL NOR gate can drive up to 3 other similar gates. Alternatively, it has enough output to drive up to 2 standard integrated circuit RTL "buffers", each of which can drive up to 25 other standard RTL NOR gates. Speeding up RTL Various companies applied the following speed-up methods to discrete RTL. Transistor switching speed has increased steadily from the first transistorized computers through the present. The GE Transistor Manual (7th ed., p.181, or 3rd ed., p.97 or intermediate editions) recommends gaining speed by using higher-frequency transistors, or capacitors, or a diode from base to collector to present saturation. Placing a capacitor in parallel with each input resistor decreases the time needed for a driving stage to back bias a driven stage's base-emitter junction. Engineers and technicians use “RCTL” (resistor capacitor transistor logic) to designate gates equipped with “speed-up capacitors.” The Lincoln Laboratory TX-0 computer's circuits included some RCTL. Using a high collector supply voltage and diode clamping decreased collector-base and wiring capacitance charging time. This arrangement required diode clamping the collector to the design logic level. This method was also applied to discrete DTL (diode–transistor logic).[6] Another method used a diode and a resistor, a germanium and a silicon diode, or three diodes in an arrangement that reduced the voltage applied to the base as the collector approached saturation. Because the transistor went less deeply into saturation, the transistor accumulated fewer stored change carriers. Therefore, less time was required to clear stored charge during transistor turn off.[4] Because DTL usually required a diode in series with the transistor's base terminal, this method applied more directly to DTL. None of these methods found their way into major integrated logic families—at least not in direct integration of the discrete implementations. Diode–transistor logic. Schematic of basic two-input DTL NAND gate. Diode–Transistor Logic (DTL) is a class of digital circuits built from bipolar junction transistors (BJT), diodes and resistors; it is the direct ancestor of transistor–transistor logic. It is called diode– transistor logic because the logic gating function (e.g. AND) is performed by a diode network and the amplifying function is performed by a transistor (contrast this with RTL and TTL). Contents 1 Operation 2 Speed disadvantage 3 CTDL Operation With the simplified circuit shown in the picture the voltage at the base will be near 0.7 volts even when one input is held at ground level, which results in unstable or invalid operation. Two diodes in series with R3 are commonly used to lower the base voltage and prevent any base current when one or more inputs are at low logic level. The IBM 1401 used DTL circuits almost identical to this simplified circuit, but solved the base bias level problem mentioned above by alternating NPN and PNP based gates operating on different power supply voltages instead of adding extra diodes. Speed disadvantage A major advantage over the earlier resistor–transistor logic is the increased fan-in. However, the propagation delay is still relatively large. When the transistor goes into saturation from all inputs being high, charge is stored in the base region. When it comes out of saturation (one input goes low) this charge has to be removed and will dominate the propagation time. One way to speed it up is to connect a resistor to a negative voltage at the base of the transistor which aids the removal of the minority carriers from the base. The above problem is solved in TTL by replacing the diodes of the DTL circuit with a multiple-emitter transistor, which also slightly reduces the required area per gate in an integrated circuit implementation. CTDL Another way to speed up DTL is to add a capacitor across R3, and a small inductor in series with R2. This technique was used in the IBM 1401, where it was called CTDL (complemented transistor diode logic). Emitter-coupled logic In electronics, emitter-coupled logic, or ECL, is a logic family in which current is steered through bipolar transistors to implement logic functions. ECL is sometimes called current-mode logic[2] or current-switch emitterfollower (CSEF) logic.[3][4] The chief characteristic of ECL is that the transistors are never in the saturation region and can thus change states at very high speed. Its major disadvantage is that the circuit continuously draws current, which means it requires a lot of power. Motorola ECL 10,000 basic gate circuit diagram History ECL was invented in August 1956 at IBM by Hannon S. Yourke[6]. Originally called current steering logic, it was used in the Stretch, IBM 7090, and IBM 7094 computers. While ECL circuits in the mid-1960s through the 1990s consisted of a differential amplifier input stage to perform logic, followed by an emitter follower to drive outputs and shift the output voltages so they will be compatible with the inputs, Yourke's current switch, also known as ECL, consisted only of differential amplifiers. To provide compatible input and output levels, two complementary versions were used, an NPN version and a PNP version. The NPN output could drive PNP inputs, and vice-versa. "The disadvantages are that more different power supply voltages are needed, and both pnp and npn transistors are required." Yourke's current switch, c. 1955. Motorola introduced their first digital monolithic integrated circuit line, MECL I, in 1962. Explanation TTL and related families use transistors as digital switches where transistors are either cut off or saturated, depending on the state of the circuit. ECL gates use differential amplifier configurations at the input stage. A bias configuration supplies a constant voltage at the midrange of the low and high logic levels to the differential amplifier, so that the appropriate logical function of the input voltages will control the amplifier and the base of the output transistor (this output transistor is used in common collector configuration). The propagation time for this arrangement can be less than a nanosecond, making it for many years the fastest logic family. Characteristics Other noteworthy characteristics of the ECL family include the fact that the large current requirement is approximately constant, and does not depend significantly on the state of the circuit. This means that ECL circuits generate relatively little power noise, unlike many other logic types which typically draw far more current when switching than quiescent, for which power noise can become problematic. In an ALU - where a lot of switching occurs - ECL can draw lower mean current than CMOS. Power supplies and logic levels The ECL circuits available on the open market usually operated with negative power supplies (5.2 volts), and logic levels incompatible with other families. This meant that interoperation between ECL and other logic families, such as the popular TTL family, required additional interface circuits. The fact that the high and low logic levels are relatively close meant that ECL suffers from small noise margins, which can be troublesome. At least one manufacturer, IBM, made ECL circuits for use in the manufacturer's own products; the power supplies were substantially different from those used in the open market. Usage The drawbacks associated with ECL have meant that it has been used mainly when high performance is a vital requirement. Other families (particularly advanced CMOS variants) have replaced ECL in many applications, even mainframe computers. However, some experts predict increasing use of ECL in the future, particularly in conjunction with more widespread adoption of advanced semiconductors such as gallium arsenide, which has always been seen as the semiconductor of the future, but cannot be produced as cheaply or cleanly as silicon and is toxic. Older high-end mainframe computers, such as the Enterprise System/9000 members of IBM's ESA/390 computer family, used ECL;[8] current IBM mainframes use CMOS. The equivalent of emitter-coupled logic made out of FETs is called source-coupled FET logic (SCFL). Positive emitter-coupled logic Positive emitter-coupled logic, or PECL, is a further development of the emitter-coupled logic (ECL) technology and requires a positive 5V supply instead of a negative 5V supply. The Low-voltage positive emitter-coupled logic (LVPECL) is an improved version of PECL to meet lower voltage requirements. PECL is a differential signaling system and mainly used in high speed and clock distribution circuits. Logic Levels: V ee Vl ow V high Vc c G 2. 3. 5. ND 2 V 0 V 0 V Transistor–transistor logic Transistor–Transistor Logic (TTL) is a class of digital circuits built from bipolar junction transistors (BJT), and resistors. It is called transistor–transistor logic because both the logic gating function (e.g., AND) and the amplifying function are performed by transistors (contrast this with RTL and DTL). It is notable for being a widespread integrated circuit (IC) family used in many applications such as computers, industrial controls, test equipment and instrumentation, consumer electronics, synthesizers, etc. Because of the wide use of this logic family, signal inputs and outputs of electronic equipment may be called "TTL" inputs or outputs, signifying compatibility with the voltage levels used. Contents 1 History 2 Theory 3 Comparison with other logic families 4 Sub-types 5 Inverters as analog amplifiers 6 Applications History A real-time clock built of TTL chips designed about 1979. TTL logic was invented in 1961 by James L. Buie of TRW, "particularly suited to the newly developing integrated circuit design technology." The first commercial integrated-circuit TTL devices were manufactured by Sylvania in 1963, called the Sylvania Universal High-Level Logic family (SUHL). The Sylvania parts were used in the controls of the Phoenix missile. TTL became popular with electronic systems designers after Texas Instruments introduced the 5400 series with military temperature range in 1964 and the later 7400 series of ICs, specified over a lower range, in 1966. The Texas Instruments 7400 family became an industry standard. Compatible parts were made by Motorola, AMD, Fairchild, Intel, Intersil, Mullard, Siemens, Signetics, SGS-Thomson (STMicroelectronics Inc.), National Semiconductor and many other companies, even in the former Soviet Union. Not only did third parties make compatible TTL parts, but compatible parts were made using many other circuit technologies as well. The term "TTL" is applied to many successive generations of bipolar logic, with gradual improvements in speed and power consumption over about two decades. The last widely available family, 74AS/ALS Advanced Schottky, was introduced in 1985.[3] As of 2008, Texas Instruments continues to supply the more general-purpose chips in numerous obsolete technology families, albeit at increased prices. Typically, TTL logic chips integrate no more than a few hundred transistors. Functions within a single package generally range from a few logic gates to a microprocessor bit-slice. TTL also became important because its low cost made digital techniques economically practical for tasks previously done by analog methods.[4] The Kenbak-1, one of the first personal computers, used TTL for its CPU instead of a microprocessor chip, which was not available in 1971.[5] The 1973 Xerox Alto and 1981 Star workstations, which introduced the graphical user interface, used TTL circuits integrated at the level of ALUs and bitslices, respectively. Most computers used TTL-compatible logic between larger chips well into the 1990s. Until the advent of programmable logic, discrete bipolar logic was used to prototype and emulate microarchitectures under development. Theory Simplified schematic of a two-input TTL NAND gate. Standard TTL NAND, one of four in 7400 TTL contrasts with the preceding resistor–transistor logic (RTL) and diode–transistor logic (DTL) generations by using transistors not only to amplify the output, but also to isolate the inputs. The p-n junction of a diode has considerable capacitance, so changing the logic level of an input connected to a diode, as in DTL, requires considerable time and energy. As shown in the top schematic at right, the fundamental concept of TTL is to isolate the inputs by using a common-base connection, and amplify the function using a common emitter connection. Note that the base of the output transistor is driven high only by the forward-biased base–collector junction of the input transistor. The second schematic adds to this a "totem-pole output". When V2 is off (output equals 1), the resistors turn V3 on and V4 off, resulting in a stronger 1 output. When V2 is on, it activates V4, driving 0 to the output. The diode forces the emitter of V3 to ~0.7 V, while R2, R4 are chosen to pull its base to a lower voltage, turning it off. By removing pull-up and pull-down transistors from the output stage, this allows the strength of the gate to be increased without proportionally affecting power consumption. TTL is particularly well suited to integrated circuits because the inputs of a gate may all be integrated into a single base region to form a multiple-emitter transistor. Such a highly customized part might increase the cost of a circuit where each transistor is in a separate package. However, by combining several small on-chip components into one larger device, it reduces the cost of implementation on an IC. As with all bipolar logic, a small amount of current must be drawn from a TTL input to ensure proper logic levels. The total current drawn must be within the capacities of the preceding stage, which limits the number of nodes that can be connected (the fanout). All standardized common TTL circuits operate with a 5-volt power supply. A TTL input signal is defined as "low" when between 0 V and 0.8 V with respect to the ground terminal, and "high" when between 2.2 V and 5 V (precise logic levels vary slightly between sub-types). Use of the TTL logic levels was so ubiquitous that complex circuit boards often contained chips made by many manufacturers in different logic families, selected based on availability and cost. Logic gates could often be treated as ideal Boolean devices without concern for harmful electrical incompatibilities. Like most integrated circuits of the period 1965–1990, TTL devices were usually packaged in through-hole, dual in-line packages with between 14 and 24 lead wires, usually made of epoxy plastic but also commonly ceramic. Beam-lead chips without packages were made for assembly into larger arrays as hybrid integrated circuits. Parts for military and aerospace applications were packaged in flat packs, a form of surface-mount package, with leads suitable for welding or soldering to printed circuit boards. Today, many TTL-compatible devices are available in surfacemounted packages. Comparison with other logic families Generally, TTL devices consume more power than an equivalent CMOS device at rest, but power consumption does not increase with clock speed as rapidly as for CMOS devices. Compared to contemporary ECL circuits, TTL uses less power and has easier design rules, but is typically slower. Designers can combine ECL and TTL devices in the same system to achieve best overall performance and economy. TTL was less sensitive to damage from electrostatic discharge than early CMOS devices. Due to the output structure of TTL devices, the output impedance is asymmetrical between the high and low state, making them unsuitable for driving transmission lines. This is usually solved by buffering the outputs with special line driver devices where signals need to be sent through cables. ECL, by virtue of its symmetric output structure, doesn't have this drawback. The typical "totem-pole" output structure often has a momentary overlap between the upper and lower transistors, resulting in a substantial pulse of current drawn from the supply. These pulses can couple in unexpected ways between multiple integrated circuit packages, resulting in reduced noise margin and lower performance. TTL systems usually have a decoupling capacitor for every one or two IC packages, so that a current pulse from one chip does not momentarily reduce the supply voltage to the others. Several manufacturers now supply CMOS logic equivalents with TTL compatible input and output levels, usually bearing part numbers similar to the equivalent TTL component and with the same pin-out diagrams. For exsmple, the 74HCT00 series provides many drop-in replacements for bipolar 7400 series parts, but uses CMOS technology. Sub-types Sucessive generations of technology produced compatible parts with improved power consumption, switching speed or both. Although vendors uniformly marketed these various product lines as TTL with Schottky diodes, some of the underlying circuits, such as used in the LS family, could rather be considered DTL.[9] Variations of and successors to the basic TTL family, which has a typical gate propagation delay of 10ns and a power dissipation of 10mW per gate, for a power-delay product (PDP) or switching energy of about 100 pJ, include: Low-power TTL (L), which traded switching speed (33ns) for a reduction in power consumption (1mW) (now essentially replaced by CMOS logic) High-speed TTL (H), with faster switching speed than standard TTL (6ns) but significantly higher power dissipation (22mW) Schottky TTL (S), introduced in 1969, which used Schottky diode clamps at gate inputs to prevent charge storage and speed switching time. These gates operated more quickly (3ns) but had higher power dissipation (19mW) Low-power Schottky TTL (LS) — used the higher resistance values of low-power TTL and the Schottky diodes to provide a good combination of speed (9.5ns) and reduced power consumption (2mW), and PDP of about 20 pJ. Probably the most common type of TTL since these were used as glue logic in microcomputers; essentially replacing the former H, L, and S sub-families. Fast (F) and Advanced-Schottky (AS) variants of LS from Fairchild and TI, respectively, circa 1985, with "Miller-killer" circuits to speed up the low-to-high transition. These families achieved PDPs of 10 pJ and 4 pJ, respectively, the lowest of all the TTL families. Most manufacturers offer commercial and extended temperature ranges; for example Texas Instruments 7400 series parts are rated from 0 to 70°C, and 5400 series devices over the military-specification temperature range of −55 to +125°C. Radiation-hardened devices are offered for space applications Special quality levels and high-reliability parts are available for military and aerospace applications. Low-voltage TTL (LVTTL) for 3.3-volt power supplies and memory interfacing. Inverters as analog amplifiers While designed for use with logic-level digital signals, a TTL inverter can be biassed to be used as an analog amplifier. Such amplifiers may be useful in instruments that must convert from analog signals to the digital domain, but would not ordinarily be used where analog amplification is the primary purpose. [10] TTL inverters can also be used in crystal oscillators where their analog amplifcation ability is significant in analysis of oscillator performance. Applications Before the advent of VLSI devices, TTL integrated circuits were a standard method of construction for the processors of mini-computer and mainframe processors; such as the DEC VAX and Data General Eclipse, and for equipment such as machine tool numerical controls, printers, and video display terminals. As microprocessors became more functional, TTL devices became important for "glue logic" applications, such as fast bus drivers on a motherboard, which tie together the function blocks realized in VLSI elements. CMOS Static CMOS Inverter Complementary metal–oxide–semiconductor (CMOS) is a major class of integrated circuits. CMOS technology is used in microprocessors, microcontrollers, static RAM, and other digital logic circuits. CMOS technology is also used for a wide variety of analog circuits such as image sensors, data converters, and highly integrated transceivers for many types of communication. Frank Wanlass got a patent on CMOS in the 1960's (US Patent 3,356,858). CMOS is also sometimes referred to as complementary-symmetry metal–oxide– semiconductor. The words "complementary-symmetry" refer to the fact that the typical digital design style with CMOS uses complementary and symmetrical pairs of p-type and n-type metal oxide semiconductor field effect transistors (MOSFETs) for logic functions. Two important characteristics of CMOS devices are high noise immunity and low static power consumption. Significant power is only drawn when the transistors in the CMOS device are switching between on and off states. Consequently, CMOS devices do not produce as much waste heat as other forms of logic, for example transistor-transistor logic (TTL) or NMOS logic, which uses all n-channel devices without p-channel devices. CMOS also allows a high density of logic functions on a chip. The phrase "metal–oxide–semiconductor" is a reference to the physical structure of certain field-effect transistors, having a metal gate electrode placed on top of an oxide insulator, which in turn is on top of a semiconductor material. Instead of metal (usually aluminum in the very old days), current gate electrodes (including those up to the 65 nanometer technology node) are almost always made from a different material, polysilicon, but the terms MOS and CMOS nevertheless continue to be used for the modern descendants of the original process. Metal gates have made a comeback with the advent of high-k dielectric materials in the CMOS process, as announced by IBM and Intel for the 45 nanometer node and beyond [1]. Contents 1 Technical details o 1.1 Structure 1.1.1 Example: NAND gate 1.1.2 Example: NAND gate in physical layout o 1.2 Power: switching and leakage o 1.3 Analog CMOS Technical details "CMOS" refers to both a particular style of digital circuitry design, and the family of processes used to implement that circuitry on integrated circuits (chips). CMOS circuitry dissipates less power and is denser than other implementations having the same functionality. As this advantage has grown and become more important, CMOS processes and variants have come to dominate, so that the vast majority of modern integrated circuit manufacturing is on CMOS processes.[citation needed] Structure CMOS logic uses a combination of p-type and n-type metal–oxide–semiconductor field-effect transistors (MOSFETs) to implement logic gates and other digital circuits found in computers, telecommunications equipment, and signal processing equipment. Although CMOS logic can be implemented with discrete devices (for instance, in an introductory circuits class), typical commercial CMOS products are integrated circuits composed of millions (or hundreds of millions) of transistors of both types on a rectangular piece of silicon of between 0.1 and 4 square centimeters.[citation needed] These devices are commonly called "chips", although within the industry they are also referred to as "die" (singular) or "dice", "dies", or "die" (plural). In CMOS logic, a collection of n-type MOSFETs are arranged in a pull-down network between the output node and the lower-voltage power supply rail, named Vss, which often has ground potential. Instead of the load resistor of NMOS logic gates, CMOS logic gates have a collection of p-type MOSFETs in a pull-up network between the output and the higher-voltage rail, named Vdd. Pull-up and pull-down refer to the idea that the output node, which exhibits some internal capacitance, is charged or discharged by the connected pull-up and pull-down networks. By asserting or de-asserting the inputs to the CMOS circuit, individual transistors along the pull-up and pull-down networks become conductive, and a path is connected from the output node to one of the voltage rails. A digital CMOS circuit cannot be in a pull-up and pull-down state at the same time, except when switching between the two states. Each input is connected to both the pull-up and pull-down networks in a complementary fashion, so that when an n-type transistor on the pulldown path is off, the p-type on the pull-up path is on, and vice-versa. CMOS logic dissipates less power than NMOS logic circuits because CMOS dissipates power only when switching (dynamic power). On a typical ASIC in a modern 90 nanometer process, switching the output might take 120 picoseconds, and happen once every ten nanoseconds. NMOS logic dissipates power whenever the output is low (static power), because there is a current path from Vdd to Vss through the load resistor and the n-type network. n-type MOSFETs are complementary to p-type because they turn on when their gate voltage goes sufficiently below their source voltage, and because they can pull the drain all the way to Vdd. Thus, if both a n-type and p-type transistor have their gates connected to the same input, the n-type MOSFET will be on when the p-type MOSFET is off, and vice-versa. Example: NAND gate NAND gate in CMOS logic As an example, shown on the right is a circuit diagram of a NAND gate in CMOS logic. If both of the A and B inputs are high, then both the n-type transistors (bottom half of the diagram) will conduct, neither of the p-type transistors (top half) will conduct, and a conductive path will be established between the output and Vss, bringing the output low. If either of the A or B inputs is low, one of the n-type transistors will not conduct, one of the p-type transistors will, and a conductive path will be established between the output and Vdd, bringing the output high. Another advantage of CMOS over NMOS is that both low-to-high and high-to-low output transitions are fast since the pull-up transistors have low resistance when switched on, unlike the load resistors in NMOS logic. In addition, the output signal swings the full voltage between the low and high rails. This strong, more nearly symmetric response also makes CMOS more resistant to noise. See Logical effort for a method of calculating delay in a CMOS circuit. Example: NAND gate in physical layout The physical layout of a NAND circuit (based on the CMOS logic example given) This example shows a NAND logic device drawn as a physical representation as it would be manufactured. The physical layout perspective is a "bird's eye view" of a stack of layers. The circuit is constructed on a P-type substrate. The polysilicon, diffusion, and n-well are referred to as "base layers" and are actually inserted into trenches of the P-type substrate. The contacts penetrate an insulating layer between the base layers and the first layer of metal (metal1) making a connection. The inputs to the NAND (illustrated in green coloring) are in polysilicon. The CMOS transistors (devices) are formed by the intersection of the polysilicon and diffusion: N diffusion for the N device; P diffusion for the P device (illustrated in salmon and yellow coloring respectively). The output ("out") is connected together in metal (illustrated in cyan coloring). Connections between metal and polysilicon or diffusion are made through contacts (illustrated as black squares. The physical layout example matches the NAND logic circuit given in the previous example. The N device is manufactured on a P-type substrate. The P devices is manufactured in an Ntype well (n-well). A P-type substrate "tap" is connected to VSS and an N-type n-well tap is connected to VDD to prevent latchup. Power: switching and leakage CMOS circuits dissipate power by charging and discharging the various load capacitances (mostly gate and wire capacitance, but also drain and some source capacitances) whenever they are switched. The charge moved is the capacitance multiplied by the voltage change. Multiply by the switching frequency to get the current used, and multiply by voltage again to get the characteristic switching power dissipated by a CMOS device: P = CV2f. A different form of power consumption became noticeable in the 1990s as wires on chip became narrower and the long wires became more resistive. CMOS gates at the end of those resistive wires see slow input transitions. During the middle of these transitions, both the NMOS and PMOS networks are partially conductive, and current flows directly from Vdd to Vss. The power thus used is called crowbar power. Careful design which avoids weakly driven long skinny wires has ameliorated this effect, and crowbar power is nearly always substantially smaller than switching power. Both NMOS and PMOS transistors have a threshold gate-to-source voltage, below which the current through the device drops exponentially. Historically, CMOS designs operated at supply voltages much larger than their threshold voltages (Vdd might have been 5 V, and Vth for both NMOS and PMOS might have been 700 mV). But as supply voltages have come down to conserve power the Vdd to Vss short circuit is avoided. However, to speed up the designs, manufacturers have switched to gate materials which lead to lower voltage thresholds and a modern NMOS transistor with a Vth of 200 mV has a significant subthreshold leakage current. Designs (e.g. desktop processors) which try to optimize their fabrication processes for minimum power dissipation during operation have been lowering Vth so that leakage power begins to approximate switching power. As a result, these devices dissipate considerable power even when not switching. Leakage power reduction using new material and system design is critical to sustaining scaling of CMOS. The industry is contemplating the introduction of High-k Dielectrics to combat the increasing gate leakage current by replacing the silicon dioxide that are the conventional gate dielectrics with materials having a higher dielectric constant. A good overview of leakage and reduction methods are explained in the book Leakage in Nanometer CMOS Technologies ISBN 0-387-25737-3. Analog CMOS Besides digital applications, CMOS technology is also used for analog applications. For example, there are CMOS operational amplifier ICs available in the market. CMOS technology is also widely used for RF applications all the way to microwave frequencies. Indeed, CMOS technology is used for mixed-signal (analog+digital) applications. BiCMOS In integrated circuit technologies, BiCMOS, also called BiMOS, refers to the integration of bipolar junction transistors and CMOS technology into a single device. This technology has commercial application in amplifier and discrete component logic design. More recently it has become the technology of choice for power electronics products[citation needed] such as voltage regulators. History Historically, integrating bipolar and metal–oxide–semiconductor (MOS) transistors into a single device proved difficult and uneconomical. So until now most integrated circuits have used one or the other, according to application requirements. Bipolar transistors offer high speed, high[citation needed] gain, and low output resistance, whereas CMOS technology offers high input resistance, which translates to simple, low-power logic gates. For years designers of circuits utilizing discrete components have realized the advantages of integrating the two technologies; however, lacking implementation in integrated circuits, application was restricted to fairly simple designs. In the 1990s[citation needed], modern integrated circuit (IC) fabrication technologies began to make BiCMOS a reality. This technology rapidly found application in amplifiers and analog power management circuits, and has some advantages in digital logic. BiCMOS circuits use the characteristics of each type of transistor most appropriately. Generally this means that high current circuits use metal–oxide–semiconductor field-effect transistor (MOSFETs) for efficient control, and portions of specialized very high performance circuits use bipolar devices. Examples of this include radio frequency (RF) oscillators, bandgap-based references and low noise circuits. The Pentium, Pentium Pro, and SuperSPARC microprocessors also used BiCMOS[citation needed]. Advantages MOS circuits are ideally suited for use in logic (digital) applications because of their low current consumption. Bipolar devices are critical for creating accurate voltage references and when very low noise is required. Since the early 1990's power MOS devices (power FETs) are also used extensively in BiCMOS ICs for switching or regulating high currents as this can be done easily with low complexity control circuits. The major mixed-signal semiconductor suppliers all have power BiMOS processes for these applications. Freescale's SMARTMOS process is an example of a commercially successful BiCMOS process which uses the characteristics of the different transistors very effectively. Other companies' BiCMOS process include Texas Instruments' LBC process, and Maxim's BCDMOS. Difficulties BiCMOS as a fabrication process is not currently as commercially viable for some applications such as microprocessors as either BJT or CMOS fabrication. Unfortunately, many of the improvements to CMOS fabrication, for example, do not transfer directly to BiCMOS fabrication. An inherent difficulty arises from the fact that fine tuning of both the BJT and MOS components is impossible without adding many extra fabrication steps, and consequently increasing the cost. Finally, in the area of high performance logic, BiCMOS may never offer the (relatively) low power consumption of CMOS alone. nMOS logic nMOS logic uses n-type metal-oxide-semiconductor field effect transistors (MOSFETs) to implement logic gates and other digital circuits. nMOS transistors have three modes of operation: cut-off, triode, and saturation (sometimes called active). The n-type MOSFETs are arranged in a so-called "pull-down network" (PDN) between the logic gate output and negative supply voltage, while a resistor is placed between the logic gate output and the positive supply voltage. The circuit is designed such that if the desired output is low, then the PDN will be active, creating a current path between the negative supply and the output. As an example, here is a NOR gate in nMOS logic. If either input A or input B is high (logic 1, = True), the respective MOS transistor acts as a very low resistance between the output and the negative supply, forcing the output to be low (logic 0, = False). When both A and B are high, both transistors are conductive, creating an even lower resistance path to ground. The only case where the output is high is when both transistors are off, which occurs only when both A and B are low, thus satisfying the truth table of a NOR gate: A AB NOR B 0 0 1 0 1 0 1 0 0 1 1 0 While nMOS logic is easy to design and manufacture (a MOSFET can be made to operate as a resistor, so the whole circuit can be made with nMOSFETs), it has several shortcomings as well. The worst problem is that a DC current flows through an nMOS logic gate when the PDN is active, that is whenever the output is low. This leads to static power dissipation even when the circuit sits idle. Also, nMOS circuits are slow to transition from low to high. When transitioning from high to low, the transistors provide low resistance, and the capacitative charge at the output drains away very quickly. But the resistance between the output and the positive supply rail is much greater, so the low to high transition takes longer. Using a resistor of lower value will speed up the process but also increases static power dissipation. Additionally, the asymmetric input logic levels make nMOS circuits susceptible to noise. These disadvantages are why nMOS logic was supplanted by CMOS logic both in low-power and in high-speed digital circuits, such as microprocessors, during the 1980s. pMOS logic pMOS logic uses p-type metal-oxide-semiconductor field effect transistors (MOSFETs) to implement logic gates and other digital circuits. pMOS transistors have three modes of operation: cut-off, triode, and saturation (sometimes called active). The p-type MOSFETs are arranged in a so-called "pull-up network" (PUN) between the logic gate output and positive supply voltage, while a resistor is placed between the logic gate output and the negative supply voltage. The circuit is designed such that if the desired output is high, then the PUN will be active, creating a current path between the positive supply and the output. While pMOS logic is easy to design and manufacture (a MOSFET can be made to operate as a resistor, so the whole circuit can be made with pMOSFETs), it has several shortcomings as well. The worst problem is that a DC current flows through a pMOS logic gate when the PUN is active, that is whenever the output is high. This leads to static power dissipation even when the circuit sits idle. Also, pMOS circuits are slow to transition from high to low. When transitioning from low to high, the transistors provide low resistance, and the capacitative charge at the output drains away very quickly. But the resistance between the output and the negative supply rail is much greater, so the high to low transition takes longer. Using a resistor of lower value will speed up the process but also increases static power dissipation. Additionally, the asymmetric input logic levels make pMOS circuits susceptible to noise. Though initially easier to manufacture, pMOS logic was supplanted by nMOS logic because nMOS is faster than pMOS. Integrated injection logic Simplified schematic of an I2L inverter. Integrated Injection Logic (IIL, I2L, or I2L) is a class of digital circuits built with multiple collector bipolar junction transistors (BJT). When introduced it had speed comparable to TTL yet was almost as low power as CMOS, making it ideal for use in VLSI (and larger) integrated circuits. Although the logic levels are very close (High: 0.7V, Low: 0.2V), I2L has high noise immunity because it operates by current instead of voltage. Operation IIL circuit The heart of an I2L circuit is the common emitter open collector inverter. Typically, an inverter consists of an NPN transistor with the emitter connected to ground and the base biased with a forward current. The input is supplied to the base as either a current sink (low logic level) or as a high-z floating condition (high logic level). The output of an inverter is at the collector. Likewise, it is either a current sink (low logic level) or a high-z floating condition (high logic level). To understand how the inverter operates, it is necessary to understand the current flow. If the bias current is shunted to ground (low logic level), the transistor turns off and the collector floats (high logic level). If the bias current is not shunted to ground because the input is high-z (high logic level), the bias current flows through the transistor to the emitter, switching on the transistor, and allowing the collector to sink current (low logic level). Because the output of the inverter can sink current but cannot source current, it is safe to connect the outputs of multiple inverters together to form a wired AND gate. When the outputs of two inverters are wired together, the result is a twoinput NOR gate because the configuration (NOT A) AND (NOT B) is equivalent to NOT (A OR B). This logical relationship is known as De Morgan's Theorem.