sdr - implementation of low frequency trans

advertisement

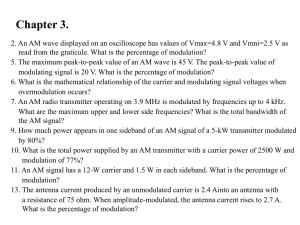

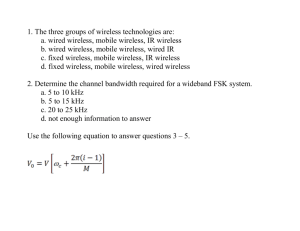

AN FPGA BASED RECONFIGURABLE TRANSRECEIVER FOR SDR. Author:Ishwar.c.Hilli Guide :Smt Chinna v.Gowdar Asst.Professor RYMEC Bellary ABSTRACT: A software-defined radio (SDR) allows for digital communication systems to simply implement more refined coding and modulation technologies, which is tremendously important in convention the ever-increasing demands of the wireless communication industry. Software defined radio (SDR) technology enables implementation of wireless devices that support multiple air interfaces and modulation formats, which is very important if consider proliferation of wireless standards. To enable such functionality SDR is using reconfigurable hardware platform such as Field Programmable Gate Array (FPGA).This Paper presents Design and implementation procedure of 64 bit QPSK trans-receiver on VIRTEX 5.5 fpga kit. INDEX TERMS: SDR,QPSK,PRBS generator, RRC filter, DDS. INTRODUCTION: The term software radio, which turned out to be later the term software defined radio, was initially presented by prof. Joseph Mitola [9], as a methodology for executing a re-programmable and re-configurable radio handset. Advantages and focal points of SDR handset frameworks got to be obvious after the improvement of countless for wireless communication networks. The terminal hardware of administrators was obliged to bolster particulars of more models at the same time. This had obliged the need to actualize a handset framework that has the capacity bolster various encryptions, modulation and signal handling strategies. Handset frameworks actualized as per the idea of SDRs, speak to an answer for these issues and difficulties. One conceivable methodology for the acknowledgment of SDR handset frameworks is the utilization of FPGA equipment segments. FPGA stage is appealing on account of its great execution, low power utilization and configurability. Quadrature phase shift keying (QPSK) is a modulation plan which sends a couple of bits for each image, expanding information rate by a component of two. Other modulation plans, for example, 8PSK and 16PSK build information rate significantly further, sending triplets and quadruplets of bits per image. A common issue in QPSK and in wireless communication is transmitter synchronization, or the synchronization of the oscillator at the Receiver with the oscillator at the transmitter [1]. Keeping in mind the end goal to do as such, DDS must be affixed at both transmitter and recipient. This gives the neighborhood oscillator at the collector with a recurrence modification. In any case, once this remedy is made, a static phase blunder called phase shift will even now exist. In QPSK frameworks [4], this phase shift will be any various of 90 degrees.this can be evacuated through RRC channel. QPSK THEORY: QPSK (or 4PSK) is a modulation system that encodes information focused on the phase edge between two waveforms. The two waveforms are signified as an in-phase part, I(t), and an out-of-phase segment, Q(t). This data is adjusted with a bearer signal and transmitted. The numerical representation of the transmitted signal, is Here I,Q and f0 denotes the carrier frequency and the vectors I, Q carry one bit information each. Fig. 1. QPSK constellation grid. The received signal is demodulated and the decoded data can be symbolized as a constellation diagram on an x-y plane in expressions of symbols. Fig 1 illustrates the possible symbols at 45, 135, 225 and 315 degrees respectively. Each symbol in the constellation signifies two bits of information that are decoded centered on their position in the constellation. The stint quadrature aptly describes this technique of modulation because the data is represented based on the quadrant the symbol is located in. In higher order phase-shift keying modulation like 8PSK or 16PSK, the constellation diagram becomes more packed in order to represent more symbols. Performance of any radio system be contingent on the effectiveness of the modulation scheme used. The two most significant types that decide the thorough efficiency of the modulation scheme are power efficiency and bandwidth efficiency. Power efficiency is the ability of a modulation technique to realm the quality (e.g. BER) of the signal with nominal signal power. It is well-defined as the ratio of signal energy per bit to noise spectral density (Eb/No) required to achieve a particular BER. Bandwidth efficiency is the capability of a modulation technique to transfer more data at the given bandwidth, which decides the system/channel capacity. It is defined as the ratio of data rate in bits per second to allocated bandwidth in Hertz (R/B). There exists a essential adjustment in any communication system between the power efficiency and bandwidth efficiency as one can be achieved only at the expense of the other. THE MODEL OF QPSK Two BPSK modulated signals assembled together represent a QPSK signal by exhausting two orthogonal carrier signals [3]. We can represent QPSK signals by: At the receiver, the received signal is downconverted to the baseband by multiplying it by the carrier frequency. QPSK principally practices the configuration shown in Fig. 2 with numerous blocks, particular for QPSK. Fig.2 QPSK Transmitter-Receiver scheme Specifications Carrier frequency : 1.5 MHz Transmitter O/P : 1MHz, -5dBm Modulation : 64 bit QPSK Data rate : 50 KHz Carrier acquisition : 0.00002 sec DESIGN FLOW PROCESS: The entire process of design simulation to bit file generation and implementation onto the hardware is as shown below. Fig3 :Design process flow Simulation of the design flow was done using Simulink’s system Generator, a system level modeling software from Xilinx [6]. This software can be used for designing and simulating DSP systems for FPGAs in a visual data flow environments such as MATLAB/ Simulink [7]. It offers flexibility to simulate the signal processing algorithms and verify their functionalities at the bit-level without translating the design into hardware. Design was simulated and verified using System Generator. The HDL Netlist was generated for Spartan 3AN FPGA –xc3s700an-4fgg484. The VHDL code was then synthesized, translated, mapped in ISE design Suite by modifying the constraints and pin-outs. Finally, the bitstream was generated and loaded on FPGA-3AN starter kit to complete the implementation process. PROPOSED BLOCK DIAGRAM: Fig 4 :Schematic of low frequency trans-receiver First the prbs sequence is generated and demuxed into i-phase and q-phase and the data sequence is converted to bipolar from unipolar.then the sequence is passed through RRC filter (0.5 roll off) then it is multipleed with carrier signal generated by DDS and then transmits after multiplexing and the same but reverse process takes place at receiver side. RESULTS: Fig5: Frequency Response of RRC filter (rolloff=0.5) Fig6: Frequency Response of Low Pass matching filter Fig 7:Implementation result on fpga virtex5.5 CONCLUSION: SDR of low frequency trans-receiver was effectively actualized on a solitary FPGA chip. The deliberate results demonstrate that transmitter info matches with the beneficiary yield. Matlab reenactments were additionally done to pick up understanding to the current issue. The general activity is a brilliant illustration of actualizing an equipment issue in software. Likewise it gives a minimal effort, low power arrangement. FPGA usage may further give adaptability in tweaking the configuration for distinctive information rates, Modulation sorts, Carrier Frequency, Filter sorts and so forth making the outline adequately reconfigurable. Future work would include utilization of lapse coding/ translating, bearer recuperation algorithms,reduction in use of zone and force, Other modulation procedures and so forth to convey a versatile altered outline. References 1) Shahana K, Ravi Kumar Gupta, K.S.Parikh, “ sdr - implementation of low frequency trans-receiver on fpga”, Internatioal Conference on Signal Processing and Integrated Networks (SPIN), 2014. 2) Veerendra Bhargav Alluri, J. Robert Heath, Michael Lhamon, “A New Multichannel, Coherent Amplitude Modulated, Time-Division Multiplexed, Software-Defined Radio Receiver Architecture, and Field-ProgrammableGate-Array Technology Implementation”, IEEE TRANSACTIONS ON SIGNAL PROCESSING, VOL. 58, NO. 10, OCTOBER 2010. 3) Prashant D. Thombare , Ameed M. Shah, “ Low Power QPSK Modulator on FPGA” International Journal of Advanced Research in Computer Science and Software Engineering, Volume 4, Issue 1, January 2014 4) Rehan Muzammil, M.Salim Beg, Mohsin M. Jamali, “ A Dynamically Reconfigurable Transceiver for Software Defined Radio”, International Journal of Computer Applications (0975 – 8887) Volume 76– No.17, August 2013. 5) Chris Dick, Fred Harris, and Michael Rice, “Synchronization in software radios-carrier and timing recovery using FPGA”, Journal of VLSI Signal Processing, Vol. 36, pp. 57-71, Kluwer academic publishers, Netherland, 2000. 6) Hazim Salah Abdulsatar, Kareem Jabbar Tijil, Ali Hashim Jryian, “ Low power Transceiver Structure for Wireless and Mobile Systems Based SDR Technology Using MATLAB and System Generator”, International Journal of Engineering and Advanced Technology (IJEAT) ISSN: 2249 – 8958, Volume-3, Issue-2, December 2013. 7) Teena Sakla, Divya Jain,Sandhya Gautam , “Implementation of digital qpsk modulator by using vhdl / matlab”, International Journal of Engineering Science and Technology Vol. 2(9), 2010, 4827-4831. 8) J. Hwang, B. Milne, N. Shirazi, J. Strommer, “System Level Tools for DSP in FPGAs,” Xilinx Inc., 2001. 9) Tarik Kazaz, Merima Kulin, Mesud Hadzialic “Design and Implementation of SDR Based QPSK Modulator on FPGA”2001.