Chipsets Featured In New Mobile Phones

advertisement

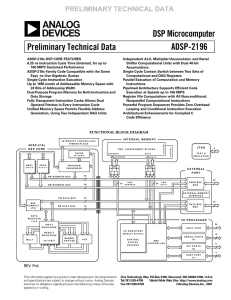

Analog Device Chipsets Featured In New Mobile Phones Eric Tong April 6, 2004 Agenda Background AD20msp430 SoftFone® Chipset Digital Baseband Controller - AD6526 ADSP-2181 Why ADSP-2181 Not ADSP-21061 Question Background December 15, 2003 – Analog Devices joint development with TCL Mobile Communication Co., Ltd. on GSM mobile phones Why TCL Mobile Communication CO. – Population • 1.3 billion in China • 28 million in Shanghai and Beijing – TCL Customer • 9.8 Million in 2003 • 100.8 Million US Dollars Net Profit in 2003 AD20msp430 SoftFone® Chipset Analog Devices’ Fourth Generation GSM BaseBand Chipset – Color Displays, Camera, Games, and Polyphonic Ring Tones Consists Two Chips – Digital Baseband Controller • AD6522, AD6526, AD6528 – Analog/Mixed-Signal Interface Chip • AD6521, AD6535 AD6526 Description Second Device of the AD20msp430 series of SoftFone® GSM Baseband Processors Designed to be – fully integrated – easy to use – compatible with GSM900, DCS 1800 and PCS 1900 handsets – Direct PC data Interface Includes – Analog Devices ADSP-218X DSP core – ARM® Controller AD6526 Functional Block Diagram 16-bit Fixed Point Processor Data and Program SRAM Speech Encoding / Decoding Hardware Interface – Radio – Keypad – Display Operating Voltage Range 1.7-1.9V ADSP-2181 Description Singe-Chip Microcomputer Optimized for DSP ADSP-2100 Family Base Architecture – – – – – – – – – ALU, MAC, Shifter Data Address Generators Program Sequences Two Serial Ports 16-bit Internal DMA Port Byte DMA Port Programmer Timer Flag I/O Extensive Interrupt Capabilities ADSP-2181 Block Diagram ADSP-2181 (Parallel) In One Processor Cycle, ADSP-2181 can – – – – – Generate the Next Program Address Fetch the Next Instruction Perform One or Two Data Moves Update One or Two Data Address Pointers Perform a Computational Operation At the same time, the processor continues to – – – – Receive and transmit data through the two serial ports Receive and/or Transmit Data through the Internal DMA Port Receive and/or Transmit Data Through the Byte DMA Port Decrement Timer ADSP-2181 Block Diagram ADSP-2181Data Transfer Five Internal Buses 1. 2. 3. 4. 5. Program Memory Address (PMA) Bus – 14 bits Data Memory Address (DMA) Bus – 14 bits Program Memory Data (PMD) Bus – 24 bits Date Memory Data (DMD) Bus – 16 bits Result (R) Bus – 16 bits 16-bits Internal DMA Port Why ADSP-2181 Not ADSP-21061 Fast External Memory Access – – – – External Address Bus External Data Bus Internal DMA Port Byte DMA Port Simultaneously Communication Port – Two 5-bits Serial Port Why ADSP-2181 Not ADSP-21061 Parallel Operation – ADSP-21061 is designed for FIR filter – ADSP-2181 is designed for Signal Convolution PowerDown Control Logic – Protect from Sudden High Signal Power Other Features – Double Metal – Low Power (1.7V Vs 5.0 V) Why ADSP-2181 Not ADSP-21061 Size Why ADSP-2181 Not ADSP-21061 References: http://en.wikipedia.org/wiki/Shanghai#People_and_Culture http://www.analog.com/UploadedFiles/Data_Sheets/505104853 ADSP2181_d.pdf http://www.analog.com/Analog_Root/productPage/productHome /0%2C2121%2CAD20MSP430%2C00.html http://www.analog.com/UploadedFiles/Data_Sheets/280128552 AD6526_pra.pdf http://www.analog.com/Analog_Root/sitePage/pressReleaseHo me/0,2145,ContentID%253D29116%2526aind%253D%2526La nguage%253DEnglish%2526resourceWebLawID%253D,00.htm l http://biz.yahoo.com/bw/040223/235640_1.html References: http://www.analog.com/processors/epPressRelease/0,2458,level 4%253D%25252D1%2526ContentID%253D27252%2526level1 %253D431%2526level2%253D%25252D1%2526level3%253D %25252D1%2526resourceWebLawID%253D36,00.html http://www.analog.com/Analog_Root/productPage/productHome /0%2C2121%2CAD6522%2C00.html http://www.nokia.com/nokia/0,,54665,00.html http://www.analog.com/UploadedFiles/Product_Briefs/12458878 8ad6526.pdf