PPTX - ECpE Senior Design

advertisement

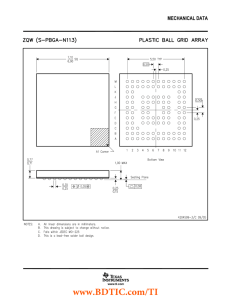

SDDEC1004 HIGH SPEED WIRED DATA COLLECTION Honeywell Bob Dearth Michael Retzler Brad Lucht ISU Prof. Zhengdao Wang Zachary Coffin, Cpr E Radell Young, E E William Zimmerman, E E* REQUIREMENTS / SPECIFICATION PROBLEM / NEED STATEMENT Honeywell’s Kansas City Plant needs a method to collect experimental data very quickly over a distance of 300 feet. All previous designs are now too slow and error-prone to collect useful data. REQUIREMENTS/SPECIFICATION CONCEPT DESCRIPTION Transmitter and Receiver Commercial Off-the-Shelf Components Speed requirements Cost constraints Availability Cat-5e Frequency Response Availability and Cost Onboard Battery CONCEPT BLOCK DIAGRAM Piezo Film Sensor Measurement Specialties, Inc. LDT 1-028K/L Piezo Film Sensor Measurement Specialties, Inc. LDT 1-028K/L Piezo Film Sensor Measurement Specialties, Inc. LDT 1-028K/L Piezo Film Sensor Measurement Specialties, Inc. LDT 1-028K/L Transmitter 9V Battery Voltage Biasing Voltage Biasing Voltage Biasing Voltage Biasing 1.8V Regulator Texas Instruments TPS76918 A to D Texas Instruments ADS931 A to D Texas Instruments ADS931 A to D Texas Instruments ADS931 A to D Texas Instruments ADS931 8 8 8 8 Parity Texas Instruments CD74ACT280 Parity Texas Instruments CD74ACT280 Parity Texas Instruments CD74ACT280 Parity Texas Instruments CD74ACT280 9 9 9 MUX 16:1 Texas Instruments ADG706 MUX 16:1 Texas Instruments ADG706 MUX 16:1 Texas Instruments ADG706 3.3V Regulator Texas Instruments TPS76933 24 MHz Crystal ECS Inc. ECS-240-12-4X Clock Generator Texas Instruments CDCE913PW 4-bit Counter Texas Instruments CD74HCT163E LVDS Transciever National Semiconductor DS92LV040A Reset Logic 8 300ft cat-5e LVDS Transciever National Semiconductor DS92LV040A Clock Generator Texas Instruments CDCE913PW Reciever USB Transciever ST Ericsson ISP1508A Windows XP Computer REQUIREMENTS/SPECIFICATION OPERATING ENVIRONMENT Equipment shall be used indoors in a regulated testing environment. Transmitter shall be housed in a larger device, in a cavity no larger than 3x3x1/2 inches. Nature of experiments inhibits wireless communication. Data is to be retrieved on a Windows XP machine. REQUIREMENTS/SPECIFICATION USER INTERFACE DESCRIPTION Data shall be made available in a table format on a Windows XP computer There may be an optional power indicator LED on the transmitter board REQUIREMENTS/SPECIFICATION FUNCTIONAL REQUIREMENTS Convert four analog voltage signals from provided piezoelectric sensors to 8-bit digital signals at a minimum rate of 2 million samples per second Data collection and transmission must start from a time approximately T-4 second, and end no earlier than T-5us System shall use wired connection Maximum Voltage Supply 24V DC Minimize error REQUIREMENTS/SPECIFICATION NON-FUNCTIONAL REQUIREMENTS Budget $100 per transmitter Transmitting device shall be no larger than 3x3x½ inches in volume REQUIREMENTS/SPECIFICATION MARKET / LITERATURE SURVEY Chipset optimized for performance at target price All-in-one chips too expensive and too high latency Cable specified for availability and cost considerations REQUIREMENTS/SPECIFICATION DELIVERABLES Chipset meeting all design requirements (cost, size, performance) Schematic has been created in Cadence Footprints for some chips were not provided in datasheets – this delayed PCB generation PROJECT PLAN: WORK BREAKDOWN – CONTRIBUTION BY MEMBER Task ZC RY MM Chipset Specification 50% 45% 5% Documentation 30% 70% Schematics 100% Testing 40% 40% Poster 45% 55% BZ 20% PROJECT PLAN: RESOURCE REQUIREMENTS Manufacturing equipment to produce hundreds of transmitter boards Sensors and appropriate biasing circuitry as analog input sources Windows XP data capture environment PROJECT PLAN: PROJECT SCHEDULE PROJECT PLAN: RISKS Loss of team member – Mazdi Masud Signal loss too great New team member – Bill Zimmerman Specify more robust cable – Shielded Cat-6 On-board latency too great Add clocked register between multiplexers and LVDS SYSTEM DESIGN SYSTEM REQUIREMENTS / ANALYSIS PCB layout to connect chips as necessary No less than 3.3V energy source A combination of several button cell batteries may provide a more cost-effective solution than standard 9V cells SYSTEM DESIGN FUNCTIONAL DECOMPOSITION Transmitter board Accepts four voltage signals (current version takes a range of -150 to +150 Volts, as specified by piezo sensor) Applies 1-bit odd parity to each channel Transmits over four channels (three data, one clock, eight conductors) in LVDS Receiver board Regenerates clock signal Decodes LVDS data and sends to USB UART Windows XP Aligns data samples to satisfy parity check DETAILED DESIGN HW/SW SPECIFICATIONS – CHIPSET Measurement Specialties, - Inc. LDT 1-028K/L (Piezo, 4x) Texas Instruments - TPS76918DBVR (Voltage Regulator, 2x) Texas Instruments - TPS76933DBVR (Voltage Regulator, 2x) Texas Instruments - ADS931E (AtoD, 4x) Texas Instruments - CD74AC280M96 (Parity, 4x) Texas Instruments - ADG706BRUZ (MUX, 3x) ECS Inc. - ECS-240-12-4X (24MHz Crystal) Texas Instruments - CDCE913PW (Clock Generator, 2x) Texas Instruments - CD74HCT163E (Counter) National Semiconductor - DS92LV040ATLQA (LVDS Transceiver, 2x) ST Ericsson - ISP1506ABS (USB Transceiver) Fairchild Semiconductor - 74VHC04MX (Inverters) Texas Instruments - SN74LV27ADR (NOR gates) DETAILED DESIGN I/O SPECIFICATIONS The individual sample bits are transmitted in the following 12-bit pattern: Time (sec) 0 4.16667E-08 8.33333E-08 0.000000125 1.66667E-07 2.08333E-07 0.00000025 2.91667E-07 3.33333E-07 0.000000375 4.16667E-07 4.58333E-07 Channel 1 bit Channel 2 bit Channel 3 bit Channel 4 bit A0 B0 C0 (Clock) A1 B1 C1 (Clock) A2 B2 C2 (Clock) A3 B3 C3 (Clock) A4 B4 C4 (Clock) A5 B5 C5 (Clock) A6 B6 C6 (Clock) A7 B7 C7 (Clock) AP BP CP (Clock) D0 D3 D6 (Clock) D1 D4 D7 (Clock) D2 D5 DP (Clock) Where 8-bit samples A through D consist of bits 0 through 7 and parity bit ‘P’. DETAILED DESIGN USER INTERFACE SPECIFICATION Once the transmitter board is powered it will continuously transmit data – no interaction required. Data may be collected from the UART as desired DETAILED DESIGN TEST PLAN Testing specifications received from Honeywell Input square waves of frequencies up to 1MHz Signal input to LVDS transmitter must not waver during one clock period due to MUX propagation delay If it does, signal buffer will be required, increasing latency, cost, size, and requiring a different PCB DETAILED DESIGN SIMULATION / PROTOTYPING Complexity of the system prevented simulation Prototype construction is taking longer than anticipated PROTOTYPE BUILD PCB design could not be finalized before receiving chipset Some datasheets did not include device dimensions Second loss of team member reduced available man-hours dedicated to project Obtained chipset, sensors, cable, and final schematic PROTOTYPE TEST RESULTS Typical sensors (supplied by Honeywell) deliver ±150V 300ft of Cat-5e cable was tested for crosstalk and signal degradation Signal loss measured as -10dB at 24MHz Cross-talk measured minimal PROTOTYPE TEST RESULTS Piezo sensor test results Cat-5 Cable test results Voltage measured at 50 attenuation factor Frequency response similar for distinct pairs Crosstalk very low for all pairs PROJECT CLOSURE CONCLUSIONS / LESSONS LEARNED Be Proactive Team members may be motivated by the activities of others Follow a Design Process After a process is selected tasks can more easily be distributed amongst team members Stay Positive Perform to the best of your abilities PROJECT CLOSURE FUTURE WORK PCB must be completed based on measurements of chip dimensions Chips and interface jacks must then be soldered Software to decode data stream Align data samples to satisfy parity check PROJECT SUCCESS – DEMO (SCHEMATIC) PROJECT SUCCESS INNOVATION Multiple transmission methods were investigated in order to determine the best method of achieving success within constraints set by Honeywell. Methods considered include: QAM and coaxial cable Simple Low Voltage Differential Signaling (LVDS) and twisted pairs (category-5) cable LVDS Multi Level Transmitting 4-levels (MLT-4) and Non Return to Zero Inverting (NRZ-I), again with cat-5 cable QUESTIONS