Document

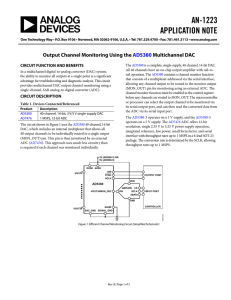

advertisement

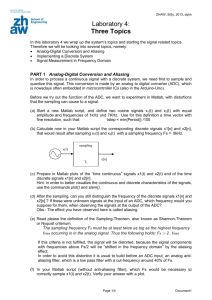

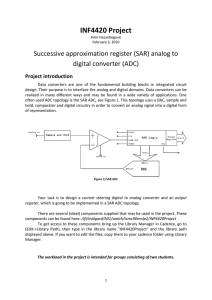

Lab IV Lecture 1 Course Overview Introduce Step 1 Course Web Page: http://www.ece.drexel.edu/courses/ECE-L304 Course Goals • Provide a practical experience in circuit prototyping • Integrate analog and digital circuit design concepts • Increase OrCAD skills • Incorporate system-level and scheduling considerations 2 What Do We Expect of You? • Attendance in lab lecture • Attendance in lab hours • You can work in a group of 2 and turn in one • report You will attend the lab section listed on your schedule • Work outside of lab hours • This course is usually not finished in the allotted lab time 3 What Should You Expect? • The materials and documentation needed to perform the project • Grade feedback on a timely basis • Answers to your questions 4 Grading Policy • The deliverables for each step of the project will receive a numerical grade. The grades for steps which involve circuit design and construction will have several parts, including design, functionality, and quality of construction. • Multi-week labs will receive greater weight 5 Grading Policy • Pre-labs must be turned in with lab reports. • Deliverables are due no later than one week after your scheduled lab meeting. Reports which are late will lose 10% per week until four week have gone by, at which time the report will not be accepted. 6 Grading Policy • Grading • 10% quizzes (2) • 90% labs (7 reports) • Standard Grade Distribution • ≥ 90% A • 80 - 90 B • Etc. 7 The Overall Idea • Design, build, debug and verify a digital recording circuit, or data acquisition system • Accept analog information • Convert to digital form • Save to RAM • Convert back to analog form • Output across a load 8 The Overall Idea Data Bus 8 ADC 8 RAM DAC Control 9 The Overall Idea • Ideally we would like to be able to record an audio (voice) message and then play it back. • We will see that there are real-world limitations that will limit our success, and some compromises will be needed. 10 Step by Step • • • • • • • Step 1 Review of ADC and DAC - simulation Step 2 Build the ADC circuit - hardware Step 3 Build the DAC circuit - hardware Step 4 Introduce static RAM - simulation Step 5 Build the on-board clock - hardware Step 6 Introduce control logic - hardware Step 7 Final changes - hardware 11 Step 1- Review of DAC/ADC • A simulation-based exercise • Observe how analog signals are converted • to digital signals Observe how digital signals are converted to analog signals • The circuits observed are much simpler than those in the hardware you will use, but the concepts are similar 14 Step 1 Prelab • Read “Memory devices, timing models, and • • hierarchical blocks”, A. Motley, MicroSim Corporation, April 1997 through the “The Supporting Logic” section. Review ADC, DAC experiments from ECEL 303 Lab III. Find a box to safely carry around your circuit (6” x 8” x 3” min). 15 Step 1 Tasks • Perform simulation • Follow instructions on web site • Lab Instructions:Step 1 • Complete “Workbook” 16 Step 1 Method • • • • • • Think Discuss Draw Simulate Compare Redraw if needed, but don’t erase 17 Digital to Analog Conversion • Digital signals have discrete levels • MSB - highest weight • LSB - lowest weight • We must convert each N-bit binary value to a unique analog voltage 18 Discrete DAC 19 Discrete DAC 4-bit counter (not part of DAC) TTL voltage levels Summing Amplifier The values of the resistors in the input network of the summing amplifier determines the “weights” of the digital bits. 20 Analog to Digital Conversion 21 ADC - Input Side Schmidt Trigger Analog Input Voltage Comparator “DAC” signal from R-2R Network 22 ADC- Internal Voltage Generation Binary Counter R-2R Network D-Flip Flop ADC Types • The ADC chip we will use (ADC0804) is based on a successive approximation (SA) algorithm • The SA Register and Latch (see the functional diagram on the datasheet, p. 6-6) works like the 74161 counter in our simulation. The Ladder and Decoder contains the R-2R network. • The SA converter type is one of the most commonly used 24 Resolutions of ADC Types Successive Approximation Dual Slope Sigma-Delta Flash Pipeline 0 5 10 15 20 25 Bits Source: Aspects of data acquisition system design, P. Miller, TI Analog Applications, Analog and Mixed-Signal Products, August 1999. 25 Speeds of ADC Types Successive Approximation Dual Slope Sigma-Delta Flash Pipeline 1 100 10000 1E+06 1E+08 1E+10 Samples per Second Source: Aspects of data acquisition system design, P. Miller, TI Analog Applications, Analog and Mixed-Signal Products, August 1999. 26 Step 1 Deliverables • A completed Chapter 11 workbook • • • • • • Discrete DAC summing ckt schematic Discrete DAC summing ckt simulation Integrated Ckt ADC schematics Integrated Ckt ADC simulation Answer Questions Discrete Analog-to-Digital for extra credit (10%) • Due 1 week after lab date, in 7-205 27