inversion layer

advertisement

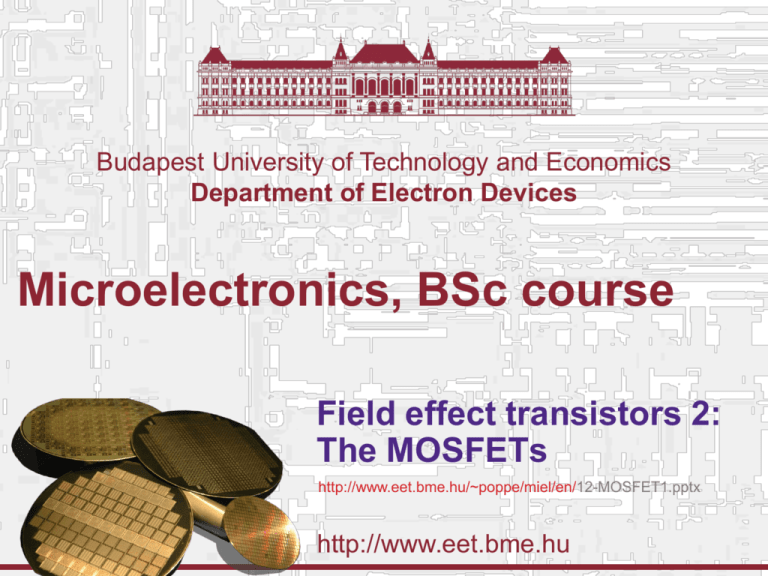

Budapest University of Technology and Economics Department of Electron Devices Microelectronics, BSc course Field effect transistors 2: The MOSFETs http://www.eet.bme.hu/~poppe/miel/en/12-MOSFET1.pptx http://www.eet.bme.hu Budapest University of Technology and Economics Department of Electron Devices The abstraction level of our study: SYSTEM MODULE + GATE CIRCUIT Vin Vout DEVICE G S n+ 05-11-2014 D n+ Microelectronics BSc course, The MOSFETs © András Poppe & Vladimír Székely, BME-EET 2008-2014 2 Budapest University of Technology and Economics Department of Electron Devices Field effect transistors 1 ► FET = Field Effect Transistor – the flow of charge carriers is influenced by electric field Flow Channel depletion layer JUNCTION FET: depletion layers of pnjunctions close the channel Most important parameter: U0 pinch-off voltage ► ► transversal field is used to control Unipolar device: current is conducted by majority carriers Power needed for controlling the device 0 05-11-2014 Microelectronics BSc course, The MOSFETs © András Poppe & Vladimír Székely, BME-EET 2008-2014 3 Budapest University of Technology and Economics Department of Electron Devices Field effect transistors 2 ► MOSFET: oxide Metal-Oxide-Semiconductor FET - depletion layer oxide + inversion layer Bulk First type: depletion mode device Most important parameter: U0 pinch off voltage Bulk Second type: enhancement mode device Most important parameter: VT threshold voltage Most frequently used today 05-11-2014 Microelectronics BSc course, The MOSFETs © András Poppe & Vladimír Székely, BME-EET 2008-2014 4 Budapest University of Technology and Economics Department of Electron Devices Field effect transistors 3 ► Symbols: n channel n channel enhancement mode p channel p channel enhancement mode depletion mode p channel 05-11-2014 n channel depletion mode p channel depletion mode n channel enhancement mode Microelectronics BSc course, The MOSFETs © András Poppe & Vladimír Székely, BME-EET 2008-2014 5 Budapest University of Technology and Economics Department of Electron Devices MOSFETs ► More realistic cross-sectional view of enhnacement mode MOSFETs: Gate oxide Polysilicon Gate Source n+ Drain n+ p substrate Field-Oxide (SiO2) p+ stopper Bulk contact 05-11-2014 Microelectronics BSc course, The MOSFETs © András Poppe & Vladimír Székely, BME-EET 2008-2014 6 Budapest University of Technology and Economics Department of Electron Devices The most modern MOSFETs: ► 2007/2008 05-11-2014 … Intel: Microelectronics BSc course, The MOSFETs © András Poppe & Vladimír Székely, BME-EET 2008-2014 7 Budapest University of Technology and Economics Department of Electron Devices How is it manufactured? 05-11-2014 Microelectronics BSc course, The MOSFETs © András Poppe & Vladimír Székely, BME-EET 2008-2014 8 Budapest University of Technology and Economics Department of Electron Devices Metal gate MOS transistor In-depth structure: Source doping Layout view: Gate Drain doping Thin oxide Source Problems: • metal gate – large VT • requires accurate mask alignment 05-11-2014 Microelectronics BSc course, The MOSFETs © András Poppe & Vladimír Székely, BME-EET 2008-2014 Drain contact 9 Budapest University of Technology and Economics Department of Electron Devices Poly-Si gate MOS transistor In-depth structure: Source doping Layout view: Gate Drain doping thin oxide Source Advantages • smaller VT • self alignment 05-11-2014 Microelectronics BSc course, The MOSFETs © András Poppe & Vladimír Székely, BME-EET 2008-2014 Drain contact 10 Budapest University of Technology and Economics Department of Electron Devices A poli-Si gate nMOS process ► Start with: p type substrate (Si wafer) • cleaing, • grow thick SiO2 – this is called field oxide 05-11-2014 Microelectronics BSc course, The MOSFETs © András Poppe & Vladimír Székely, BME-EET 2008-2014 11 Budapest University of Technology and Economics Department of Electron Devices The poli-Si gate nMOS process ► Create the active zone with photolithography • • • • coat with resist, expose to UV light through a mask, development, removal of exposed resists etching of SiO2 removal of the resist M1: active zone 05-11-2014 Microelectronics BSc course, The MOSFETs © András Poppe & Vladimír Székely, BME-EET 2008-2014 12 Budapest University of Technology and Economics Department of Electron Devices The poli-Si gate nMOS process ► Create the gate structure: • • • • growth of thin oxide deposit poly-Si pattern poly-Si with photolithography etch poly-Si, etch thin oxide (resist, exposure, develop) M2: poly-Si pattern 05-11-2014 Microelectronics BSc course, The MOSFETs © András Poppe & Vladimír Székely, BME-EET 2008-2014 13 Budapest University of Technology and Economics Department of Electron Devices The poli-Si gate nMOS process ► S/D doping (implantation) • the exide (thin, thick) masks the dopants • this way the self-alignment of the gate is assured ► Passivation: deposit PSG 05-11-2014 Microelectronics BSc course, The MOSFETs © András Poppe & Vladimír Székely, BME-EET 2008-2014 14 Budapest University of Technology and Economics Department of Electron Devices The poli-Si gate nMOS process ► Open contact windows through PSG • photolithography (resist, expose pattern, • etching (copy the pattern) • cleaning develop) M3: contact window pattern 05-11-2014 Microelectronics BSc course, The MOSFETs © András Poppe & Vladimír Székely, BME-EET 2008-2014 15 Budapest University of Technology and Economics Department of Electron Devices The poli-Si gate nMOS process ► Metallization • Deposit Al • photolithography, etching, cleaning M4: metallization pattern ► ► The recepy of the process is given, the in-depth structure is determined by the sequence of the masks One needs to specify the shapes on the masks The set of shapes on subsequent masks is called layout 05-11-2014 Microelectronics BSc course, The MOSFETs © András Poppe & Vladimír Székely, BME-EET 2008-2014 16 Budapest University of Technology and Economics Department of Electron Devices Poli-Si gate self-aligned device PSG Structure: Source/drain doping thin oxide poli-Si gate Layout: metallization, contact window W L 05-11-2014 Microelectronics BSc course, The MOSFETs © András Poppe & Vladimír Székely, BME-EET 2008-2014 17 Budapest University of Technology and Economics Department of Electron Devices Steps of the self-aligned poli-Si gate process 1) Open window for the active region M photolitography, field oxide etching 2) Growth of thin oxide 3) Window for hidden contacts M Contacts the poli-Si gate (yet to be deposited) with the active region (after doping). 3) Deposit poli-Si 4) Patterning of poli-Si M 5) Open window through the thin oxide (etching only) 05-11-2014 Microelectronics BSc course, The MOSFETs © András Poppe & Vladimír Székely, BME-EET 2008-2014 18 Budapest University of Technology and Economics Department of Electron Devices Steps of the self-aligned poli-Si gate process 6) n+ doping: Form source and drain regions as well as wiring by diffusion lines. Through the hidden contact poli-Si gate will also be connected to diffused lines. 7) Deposit phosphor-silica glass (PSG) as insulator 8) Open contact windows through PSG-n M 9) Metallization 10) Patterning metallization layer M 05-11-2014 Microelectronics BSc course, The MOSFETs © András Poppe & Vladimír Székely, BME-EET 2008-2014 19 Budapest University of Technology and Economics Department of Electron Devices Layout of a depletion mode inverter ► ► S G D S G Layout == set of 2D shapes on subsequent masks Masks are color coded: ► active zone: red poly-Si: green contact windows: black metal: blue Mask == layout layer D Where is a transistor? Channel between two doped regions: CHANNEL = ACTIVE AND POLY 05-11-2014 Microelectronics BSc course, The MOSFETs © András Poppe & Vladimír Székely, BME-EET 2008-2014 20 Budapest University of Technology and Economics Department of Electron Devices Further topics: ► ► ► ► 05-11-2014 Overview of operation of MOS transistors Characteristics Secondary effects Models Microelectronics BSc course, The MOSFETs © András Poppe & Vladimír Székely, BME-EET 2008-2014 21 Budapest University of Technology and Economics Department of Electron Devices Operation of MOSFETs ► The simplest (logic) model: open (off) / short (on) | VGS | Source (of carriers) Open (off) (Gate = ‘0’) Gate Drain (of carriers) enhancement mode device Closed (on) (Gate = ‘1’) Ron 05-11-2014 | VGS | < | VT | | VGS | > | VT | open short Microelectronics BSc course, The MOSFETs © András Poppe & Vladimír Székely, BME-EET 2008-2014 22 Budapest University of Technology and Economics Department of Electron Devices Operation of MOSFETs ► n-channel device: electrons are flowing ► p-channel device: holes are flowing same operation, change of the signs ► Normally OFF device: at 0 gate (control) voltage the are "open" (enhancement mode device) ► Normally ON device: at 0 gate (control) voltage the are "short" (depletion mode device) 05-11-2014 Microelectronics BSc course, The MOSFETs © András Poppe & Vladimír Székely, BME-EET 2008-2014 23 Budapest University of Technology and Economics Department of Electron Devices Overview of MOSFET types 05-11-2014 Microelectronics BSc course, The MOSFETs © András Poppe & Vladimír Székely, BME-EET 2008-2014 24 Budapest University of Technology and Economics Department of Electron Devices Overview of the operation ► The operation is based on the so called MOS capacitance: As a result of electrical field perpendicular to the gate surface • positive charges accumulate at the metal (gate) • in the p-type semiconductor – first the positive charges are "swept" out and a depletion layer is formed – further increasing the electric field, negative carriers are collected from the bulk under the metal – if the voltage at the surface exceeds a threshold value, the type of the semiconducter gets "inverted": an inversion layer is formed VT threshold voltage – the minimal voltage needed to form the inversion layer; depends on: • the energy levels of the semiconductor material • the thickness and the dielectric constant of the oxide (SiO2) • the doping level and dielectric constant of the semiconductor (Si) 05-11-2014 Microelectronics BSc course, The MOSFETs © András Poppe & Vladimír Székely, BME-EET 2008-2014 25 Budapest University of Technology and Economics Department of Electron Devices Overview of the operation ► Surface phenomena in case of the MOS capacitance Accumulation Depletion Inversion Strong inversion: UF = 2 F Wi WF p ni exp kT WF Wv p ~ exp kT 05-11-2014 F Wi WF kT p N ln U T ln a q q ni ni Microelectronics BSc course, The MOSFETs © András Poppe & Vladimír Székely, BME-EET 2008-2014 26 Budapest University of Technology and Economics Department of Electron Devices The MOS transistor ► MOS capacitance completed by two electrodes at its two sides: ► n-channel ► p-channel 05-11-2014 device: current conducted by electrons device: current conducted by holes Microelectronics BSc course, The MOSFETs © András Poppe & Vladimír Székely, BME-EET 2008-2014 27 Budapest University of Technology and Economics Department of Electron Devices Qualitative operation of the MOSFET ► If VGS > VT, inversion layer is formed the n+ region at the source can inject electrons into the inversion channel the positive potential at the drain induces flow of electrons in the channel, the positive potential of the drain reverse biases the pn junction formed there the electrons drifted there are all sank in the n+ region and the circuit is closed 05-11-2014 Microelectronics BSc course, The MOSFETs © András Poppe & Vladimír Székely, BME-EET 2008-2014 28 Budapest University of Technology and Economics Department of Electron Devices Qualitative operation of the MOSFET the charge density in channel depends on the VGS voltage there is a voltage drop in the channel, thus, the thickness of the inversion layer will deminish along the channel at a given VDSsat saturation voltage the thickness will reach 0, this is the so called pinch-off VDSsat = VGS - VT After this voltage is reached, the MOSFET operates in saturation mode, the drain voltage does not influence the drain current any longer. 05-11-2014 Microelectronics BSc course, The MOSFETs © András Poppe & Vladimír Székely, BME-EET 2008-2014 29 Budapest University of Technology and Economics Department of Electron Devices Qualitative operation of the MOSFET In the pinch-off region the charge transport takes place by means of diffusion current. 05-11-2014 Microelectronics BSc course, The MOSFETs © András Poppe & Vladimír Székely, BME-EET 2008-2014 30 Budapest University of Technology and Economics Department of Electron Devices I-V charactersitics • output charactersitic: ID=f(UDS), parameter: UGS • input characteristc: ID=f(UGS) Output characteristic: In saturation: W n ox ID VGS VT L 2 tox K n ox tox 2 current constant The circuit designer can change the geometry only: the W width and the L length 05-11-2014 Microelectronics BSc course, The MOSFETs © András Poppe & Vladimír Székely, BME-EET 2008-2014 31 Budapest University of Technology and Economics Department of Electron Devices Example Calculate the saturation current of a MOSFET for UGS=5V if K n ox tox 110 A / V 2 VT =1V, and the geometry a) W= 5μm, L=0.4μm , b) W= 0.8μm, L=5μm ! a) ID W K 5 110 6 (U GS VT ) 2 10 (5 1) 2 1110 3 A 11mA L 2 0.4 2 b) ID W K 0.8 110 6 (U GS VT ) 2 10 (5 1) 2 141 10 6 A 141A L 2 5 2 By changing the W/L ratio the drain current can be changed by orders of magnitude 05-11-2014 Microelectronics BSc course, The MOSFETs © András Poppe & Vladimír Székely, BME-EET 2008-2014 32 Budapest University of Technology and Economics Department of Electron Devices I-V charactersitics 6 X 10-4 VDSsat = VGS - VT 5 Voltage controlled current source voltage controlled resistor 4 VGS = 2.5V VGS = 2.0V 3 linear saturation 2 VGS = 1.5V 1 VGS = 1.0V 0 cut-off 0 0.5 1 1.5 2 2.5 VDS (V) nMOS transistor, 0.25um, Ld = 10um, W/L = 1.5, VDD = 2.5V, VT = 0.4V 05-11-2014 Microelectronics BSc course, The MOSFETs © András Poppe & Vladimír Székely, BME-EET 2008-2014 33 Budapest University of Technology and Economics Department of Electron Devices Overview of the physics: ► Charges and potentials at the surface ► The threshold voltage ► The charateristics ► Secondary effects 05-11-2014 Microelectronics BSc course, The MOSFETs © András Poppe & Vladimír Székely, BME-EET 2008-2014 34 Budapest University of Technology and Economics Department of Electron Devices Potentials of the MOS structure U GB U ox U F MS QG QSC QSS Qi C0 ox d ox QG C0U ox QSC qN a S oxide 05-11-2014 semiconductor Microelectronics BSc course, The MOSFETs © András Poppe & Vladimír Székely, BME-EET 2008-2014 35 Budapest University of Technology and Economics Department of Electron Devices Potentials of the MOS structure U GB U ox U F MS Qi QG QSC QSS QG QSC QSS Qi C0U ox 2 s qN a U F QSS QG C0U ox Qi C0 (U GB U F MS ) QSC qN a S 2 s qN a U F QSS QSC qN a 05-11-2014 2 s U F 2 s qN a U F qN a Microelectronics BSc course, The MOSFETs © András Poppe & Vladimír Székely, BME-EET 2008-2014 36 Budapest University of Technology and Economics Department of Electron Devices The threshold voltage of the MOSFET Inversion U F 2 F 05-11-2014 U F 2 F U SB Microelectronics BSc course, The MOSFETs © András Poppe & Vladimír Székely, BME-EET 2008-2014 37 Budapest University of Technology and Economics Department of Electron Devices The threshold voltage of the MOSFET Qi C0 (U GB 2 F U SB MS ) 2 s qN a 2 F U SB QSS VT UGS Q 0 i VT 2 F MS 05-11-2014 Qi C0 U GS VT 2 s qN a QSS C0 C0 2 F U SB Microelectronics BSc course, The MOSFETs © András Poppe & Vladimír Székely, BME-EET 2008-2014 38 Budapest University of Technology and Economics Department of Electron Devices The threshold voltage of the MOSFET VT 2 F MS 2 s qN a QSS C0 C0 2 F U SB Flat-band potential: FB MS QSS C0 Bulk constant: P 2 s qN a C0 VT 2F FB P 2 F USB 05-11-2014 Microelectronics BSc course, The MOSFETs © András Poppe & Vladimír Székely, BME-EET 2008-2014 39 Budapest University of Technology and Economics Department of Electron Devices The charactersitics of an enhnacement mode MOSFET inversion layer Later we shall calculate these! triode region 05-11-2014 saturation Microelectronics BSc course, The MOSFETs © András Poppe & Vladimír Székely, BME-EET 2008-2014 41 Budapest University of Technology and Economics Department of Electron Devices Derivation of the charactersitic inversion layer U(0) = UGS , U(L) = UGD Qi(U) = Qi[U(x)] I D Qi W v dU v E dx dU I D Qi (U )W dx 05-11-2014 L L dU I D dx W Qi dx dx 0 0 Microelectronics BSc course, The MOSFETs © András Poppe & Vladimír Székely, BME-EET 2008-2014 42 Budapest University of Technology and Economics Department of Electron Devices Derivation of the charactersitic L L dU I D dx W Qi dx dx 0 0 inversion layer U GD I D L W Qi (U ) dU U GS Qi C0 U ( x) VT W W C0 2 U GS U VT I D C0 U VT dU U GD L U L 2 U GD W C0 2 2 U GS VT U GD VT ID L 2 GS 05-11-2014 Microelectronics BSc course, The MOSFETs © András Poppe & Vladimír Székely, BME-EET 2008-2014 43 Budapest University of Technology and Economics Department of Electron Devices Derivation of the charactersitic W C0 U GS VT 2 U GD VT 2 ID L 2 inversion layer W C0 F (U GS ) F (U GD ) ID L 2 (U VT ) 2 F (U ) 0 if U V ha T ha if U VT For all regions of operation! 05-11-2014 Microelectronics BSc course, The MOSFETs © András Poppe & Vladimír Székely, BME-EET 2008-2014 44 Budapest University of Technology and Economics Department of Electron Devices The saturation region inversion layer W C0 F (U GS ) F (U GD ) ID L 2 (U VT ) 2 F (U ) 0 ha U VT ha U VT Saturation: UGD < VT For all regions of operation! W C0 2 U GS VT ID L 2 05-11-2014 Microelectronics BSc course, The MOSFETs © András Poppe & Vladimír Székely, BME-EET 2008-2014 45 Budapest University of Technology and Economics Department of Electron Devices Overview of all types of MOSFETs 05-11-2014 Microelectronics BSc course, The MOSFETs © András Poppe & Vladimír Székely, BME-EET 2008-2014 46 Budapest University of Technology and Economics Department of Electron Devices Depletion mode MOSFET Like an enhance mode MOSFET with a negative threshold voltage 05-11-2014 Microelectronics BSc course, The MOSFETs © András Poppe & Vladimír Székely, BME-EET 2008-2014 47 Budapest University of Technology and Economics Department of Electron Devices Capacitances of the MOSFET inversion layer Bulk QG fG (U GS ,U GD ,U GB ) Qi f i (U GS ,U GD ,U GB ) S/D – B capacitance: reverse biased PN junction 05-11-2014 C gs QG U GS Microelectronics BSc course, The MOSFETs © András Poppe & Vladimír Székely, BME-EET 2008-2014 48 Budapest University of Technology and Economics Department of Electron Devices The gate capacitance: Polysilicon gate Source Drain xd n+ xd Ld W n+ Gate-bulk overlap Top view Gate oxide tox n+ L n+ Cross section 05-11-2014 Microelectronics BSc course, The MOSFETs © András Poppe & Vladimír Székely, BME-EET 2008-2014 49 Budapest University of Technology and Economics Department of Electron Devices Secondary effects ► Channel length reduction ► Narrow channel operation ► Temperature dependence ► Subthreshold current 05-11-2014 Microelectronics BSc course, The MOSFETs © András Poppe & Vladimír Székely, BME-EET 2008-2014 50 Budapest University of Technology and Economics Department of Electron Devices Dependence of threshold voltage on geometry Short channel: VT decreases 05-11-2014 Narrow channel: VT increases Microelectronics BSc course, The MOSFETs © András Poppe & Vladimír Székely, BME-EET 2008-2014 51 Budapest University of Technology and Economics Department of Electron Devices Velocity saturation ► Influences 10 the operation of short channel devices 5 Velocity saturation the speed of carriers (due to the collisions) becomes constant 0 c=1.5 0 3 (V/m) In a L = 0.25m channel device a few Volts of D-S voltage may already result in velocity saturation. 05-11-2014 Microelectronics BSc course, The MOSFETs © András Poppe & Vladimír Székely, BME-EET 2008-2014 52 Budapest University of Technology and Economics Department of Electron Devices Velocity saturation ► In short channel device velocity saturation takes place sooner (at lower voltage) 10 0 05-11-2014 Microelectronics BSc course, The MOSFETs © András Poppe & Vladimír Székely, BME-EET 2008-2014 53 Budapest University of Technology and Economics Department of Electron Devices Short channel charactersitics 2.5 X 10-4 Early velocity saturation VGS = 2.5V 2 VGS = 2.0V 1.5 Linear 1 Saturation VGS = 1.5V VGS = 1.0V 0.5 0 0 0.5 1 1.5 2 2.5 VDS (V) nMOS transistor, 0.25um, Ld = 10um, W/L = 1.5, VDD = 2.5V, VT = 0.4V 05-11-2014 Microelectronics BSc course, The MOSFETs © András Poppe & Vladimír Székely, BME-EET 2008-2014 54 Budapest University of Technology and Economics Department of Electron Devices Temperature dependence W C0 U GS VT 2 ID L 2 1 d 0,003... 0.006 / o C dT VT 1,5... 4 mV / o C T 05-11-2014 Microelectronics BSc course, The MOSFETs © András Poppe & Vladimír Székely, BME-EET 2008-2014 55 Budapest University of Technology and Economics Department of Electron Devices Subthreshold current ► Assuming a given VT is rough model; in reality the current vanishes exponentially with the gate voltage: 10-2 linear region quadratic region subthreshold, exponential region VT 10-12 0 05-11-2014 ID ~ IS e (qVGS/nkT) where n 1 VGS (V) 0.5 1 1.5 2 2.5 Microelectronics BSc course, The MOSFETs © András Poppe & Vladimír Székely, BME-EET 2008-2014 56 Budapest University of Technology and Economics Department of Electron Devices Subthreshold current ► Continuous transition between the ON and OFF states Subthreshold is undesired: strong deviation from the switch model I D ~ I 0e qVGS nkT CD , n 1 Cox ► I 0, n – ► Slope empirical parameters, n is typically 1.5 factor: S = n (kT/q) ln (10) (tipically: 60 ..100 mV/decade) – the smaller the better, depends on. Can be reduced by SOI: Si e.g. SIMOX process 05-11-2014 SiO2 Si substrate Microelectronics BSc course, The MOSFETs © András Poppe & Vladimír Székely, BME-EET 2008-2014 57 Budapest University of Technology and Economics Department of Electron Devices Subthreshold ID(VGS) charactersitic VDS : 0 .. 0.5V I D I 0e 05-11-2014 qVGS nkT qV DS 1 e kT Microelectronics BSc course, The MOSFETs © András Poppe & Vladimír Székely, BME-EET 2008-2014 58 Budapest University of Technology and Economics Department of Electron Devices Subthreshold ID(VDS) charactersitic VGS : 0 .. 0.3V I D I 0e 05-11-2014 qVGS nkT qV DS 1 e kT 1 VDS Microelectronics BSc course, The MOSFETs © András Poppe & Vladimír Székely, BME-EET 2008-2014 59 Budapest University of Technology and Economics Department of Electron Devices MOS transistor models ► ► Neded for circuit simulators (SPICE, TRANZ-TRAN, ELDO, SABER, stb) Different levels of complexity: level0, 1, 2, ...n, EKV, BSIM3, BSIM4 05-11-2014 Microelectronics BSc course, The MOSFETs © András Poppe & Vladimír Székely, BME-EET 2008-2014 60 Budapest University of Technology and Economics Department of Electron Devices Examples for MOSFETs inversion layer Photograph by optical microscope SGD SGD Micro-photograph by SEM 05-11-2014 Microelectronics BSc course, The MOSFETs © András Poppe & Vladimír Székely, BME-EET 2008-2014 61 Budapest University of Technology and Economics Department of Electron Devices Some more complex MOS circuits n- & p-channel devices : CMOS circuit, see later 05-11-2014 Microelectronics BSc course, The MOSFETs © András Poppe & Vladimír Székely, BME-EET 2008-2014 62 Budapest University of Technology and Economics Department of Electron Devices Some more complex MOS circuits Designed by CAD tools 05-11-2014 Microelectronics BSc course, The MOSFETs © András Poppe & Vladimír Székely, BME-EET 2008-2014 63