4332-2011-Slides

advertisement

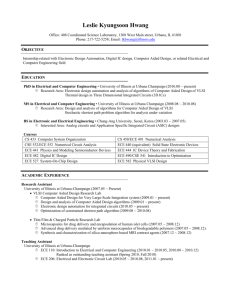

Project SRAM

Stevo Bailey

Kevin Linger

Roger Lorenzo

John Thompson

ECE 4332: Intro to VLSI

PICo’s Projects

1. 1 Mb low-power SRAM

– (Ea)2(tp)(A)(Pidle)

2. 64 kb high-speed cache

– (Ea)(tp)2(A)(Pidle)

ECE 4332: Intro to VLSI

Problem Description

•

•

•

•

•

•

•

1 Mb SRAM

32-bit words

Inputs: address, input word, read, write, clock

Outputs: output word

Robust across process, voltage, and temp

Special features optional

Minimize power

ECE 4332: Intro to VLSI

Claim

We designed and simulated a competitive 1 Mb SRAM.

1. SRAM Architecture

2. Bitcell Optimizations

3. SRAM Model Simulations

4. Layout Optimizations

5. Results and Further Work

ECE 4332: Intro to VLSI

SRAM Block Diagram

Block DeMUX

Row

Decoder

to Write Amp

to Write Amp

to Write Amp

Precharge

Precharge

Precharge

Block 0 [final block

Block

1

diagram]

Block 63

MUX

MUX

MUX

Sense/Write

Amps

Sense/Write

Amps

Sense/Write

Amps

Block MUX

ECE 4332: Intro to VLSI

Claim

1. SRAM Architecture

2. Bitcell Optimizations

3. SRAM Model Simulations

4. Layout Optimizations

5. Results and Further Work

ECE 4332: Intro to VLSI

Bitcell

• 6T-bitcell – 0.816

µm2

WL

WL

BL

2x2 bitcell array

ECE 4332: Intro to VLSI

BLB

Bitcell

ECE 4332: Intro to VLSI

Bitcell

ECE 4332: Intro to VLSI

Bitcell

[SNM monte carlo]

ECE 4332: Intro to VLSI

Claim

1. SRAM Architecture

2. Bitcell Optimizations

3. SRAM Model Simulations

4. Layout Optimizations

5. Results and Further Work

ECE 4332: Intro to VLSI

SRAM Model

LWL2

bitcell

m=1

bitcell

m=c-2

bitcell

m=1

VDD

bitcell

m=r-2

bitcell

m=r-2

LWL1

bitcell

m=1

BL1

bitcell

m=c-2

BLB1

bitcell

m=1

BL2

BLOCK 0

ECE 4332: Intro to VLSI

BLB2

SRAM Model

Rαc

BD

Rαb·c

GWL

LWL

m=1

• C values obtained from parasitic extraction

• R values from NCSU wiki on FreePDK45

(http://www.eda.ncsu.edu/wiki/FreePDK45:Metal_Layers)

Cαc

Cαb·c

m=b-1

WORD LINES (x2)

VDD

BL

BLB

VDD

VDD

BL

BLB VDD

5

m=

c

-1

32

m=

CD

SA

SAB

c

-1

32

5

CDW

WAO

WAOB

READ/WRITE MUX (x2)

ECE 4332: Intro to VLSI

SRAM Model

VDD

VDD

SAE

Out

Out

OutB

BL

SAE

OutB

BLB

BL

BLB

SAE

SAE

SENSE AMP 1

SENSE AMP 2

Sense Amp

1

2

Delay

192 ps

147 ps

ECE 4332: Intro to VLSI

SRAM Model

[We omitted this figure because of copyright laws. The image is in the

Rabaey book and available online. If you really, really need to see it, go

to http://bwrc.eecs.berkeley.edu/icbook/slides.htm, download the

power point slides for chapter 12, and go to slide 57.]

Example decoder with predecoding stage

ECE 4332: Intro to VLSI

SRAM Model

m=7

VDD

m=6

A

m=34

BD

m=6

(x2)

m=7

6:64 BLOCK DECODER

VDD

m=14 for each

m=15

A

GWL

m=193

(x2)

m=15

8:256 ROW DECODER

ECE 4332: Intro to VLSI

SRAM Model Results

ECE 4332: Intro to VLSI

SRAM Model Results

256 Rows, 64 Columns, 64 Blocks

ECE 4332: Intro to VLSI

Timing Diagram

ECE 4332: Intro to VLSI

Claim

1. SRAM Architecture

2. Bitcell Optimizations

3. SRAM Model Simulations

4. Layout Optimizations

5. Results and Further Work

ECE 4332: Intro to VLSI

Layouts

Write/Sense Amps

Block DeMux

Address Decoders

256 by 64 Block

Block DeMux

Write/Sense Amps

ECE 4332: Intro to VLSI

Layouts

BL[0]

GND

VDD

GND

BLB[0]

BL[1] GND

VDD

GND BLB[1]

WL[0]

2x2 Bit Cells

WL[1]

2x Read/Write

Mux

SA[0]

SAB[0]

WA[0]

SA[1]

WAB[0]

SAB[1]

WA[1]

WAB[1]

Sense Amp

SAOB[0]

SAO[0]

Enable

SAOB[1]

SAO[1]

Enable

ECE 4332: Intro to VLSI

Claim

1. SRAM Architecture

2. Bitcell Optimizations

3. SRAM Model Simulations

4. Layout Optimizations

5. Results and Further Work

ECE 4332: Intro to VLSI

Results

• verified functionality at

• all process corners (TT, FF, FS, SF, SS)

• VDD = { 0.54, 0.60, 0.66, 1.0, 1.1, 1.2 } volts

• temp = { 0°, 27°, 54° } Celsius

• SS forced a longer clock period for a read

ECE 4332: Intro to VLSI

Metrics

Total Energy

1.46 pJ

Read Energy

1.43 pJ

Write Energy

1.57 pJ

Read Delay

2.9 ns

Write Delay

1.97 ns

Total Delay

2.9 ns

Idle Power

208 µW

Sleep Power

99.2 µW

Bitcell Area

0.819 µm2

Total Area

1.04 mm2

Final Metric

1.337x10-36 J2·s·mm2·W

ECE 4332: Intro to VLSI

Error Correcting Code

P6

P5

P4

P3

P2

P1

P0

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Input

= 4-input XOR

SEC-DED

Error Correcting Code

Delay

0.3634 ns

Energy

53.4 fJ

Input

32

32

32

Corrected

output

Single

error

Double

error

Error

detected

P6

P5

P4

P3

P2

P1

P0

Output

ECE 4332: Intro to VLSI

Sources

B. Jacob, S. W. Ng, and D. T. Wang, Memory systems: Cache, DRAM, disk, Burlington, MA: Morgan Kaufmann,

2008, p. 282.

B. S. Amrutur and M. A. Horowitz, “Fast low-power decoders for RAMs,” JSSC, vol. 36, no. 10, 2001.

J. F. Ryan and B. H. Calhoun, “Minimizing offset for latching voltage-mode sense amplifiers for sub-threshold

operation,” ISQED, 2008.

J. Rabaey, A. Chandrakasan, and B. Nikolic, Digital integrated circuits, 2nd ed., Upper Saddle River: Pearson,

2003, p. 508.

J. Yeung and H. Mahmoodi, "Robust sense amplifier design under random dopant fluctuations in nano-scale

CMOS technologies," SOC Conference, 2006 IEEE International , 2006, pp. 261-264.

L. Hamouche and B. Allard, “Low power options for 32nm always-on SRAM architecture,” Solid State

Electronics, 2011.

ECE 4332: Intro to VLSI

Acknowledgements

Benton Calhoun, PICo liason

Team XOR (2010)

• Dominic Carr

• Jae Park

• Daniel Reyno

Team 2 (2010)

• Yanran Chen

• Cary Converse

• Chenqian Gan

• David Moore

ECE 4332: Intro to VLSI

Questions?

ECE 4332: Intro to VLSI