Transistors and Layout 2

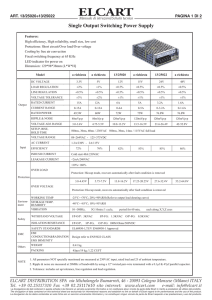

advertisement

Topics Derivation of transistor characteristics. Modern VLSI Design 3e: Chapter 2 Copyright 1998, 2002 Prentice Hall PTR MOSFET gate as capacitor Basic structure of gate is parallel-plate capacitor: (A good reference on this is www4.ncsu.edu:8030/~vmisra/MOS.ppt and physics of MOSFET is http://ece-www.colorado.edu/~bart/book/book/chapter2/ch2_6.htm) gate + + + + + + + + + + + + xox SiO2 Vg - + - - - - - - - - substrate Modern VLSI Design 3e: Chapter 2 - - - - inversion Copyright 1998, 2002 Prentice Hall PTR MOS as a parallel plate capacitance Formula for parallel plate capacitance/unit area: Cox = ox / xox, where xox is the thickness of the SO2 in cm, and ox is its permittivity: ox = 3.46 x 10-13 F/cm Gate to substrate capacitance helps determine the characteristics of a channel which forms an inversion region (region devoid of dopant carriers in the substrate) between the source and drain of a MOS transistor. In particular, it plays a critical role in the determination of the threshold voltage of a MOS transistor. Modern VLSI Design 3e: Chapter 2 Copyright 1998, 2002 Prentice Hall PTR Threshold voltage The threshold voltage, Vt0, when the source to substrate voltage is 0. Vt0 = Vfb + s + Qb/Cox + VII Components of Vt0 are: Vfb = flatband voltage between gate and substrate, i.e., the work function difference between gate and substrate. The work function is the energy required to remove an electron from the Fermi energy to the vacuum level. 2kT N a ln s is the surface potential which is equal to twice the Fermi potential q ni where ni is the intrinsic carrier (electron or hole) concentration of the substrate, kT/q is the thermal voltage, and Na is the hole concentration in the substrate. Qb/Cox is the voltage across the capacitor, whereQ 2q N , q is the charge b si a s of an electron, si is the permittivity of silicon, VII is the voltage adjustment = qDI/Cox, where DI is the ion implantation concentration (body effect) Modern VLSI Design 3e: Chapter 2 Copyright 1998, 2002 Prentice Hall PTR Threshold voltage The flat-band voltage between gate and substrate depends on the difference in the work function between gate and substrate (gs) and on fixed surface charge (Qf): Q V fb gs f Cox kT N N gs ln a 2 dp q ni assuming that the gate is doped with n-type carriers with the concentration of Ndp When the source to substrate voltage is not 0 then the threshold voltage is shifted by a differential voltage, called the body effect: Vt n( s Vsb s ) n Modern VLSI Design 3e: Chapter 2 2q si N a Cox Copyright 1998, 2002 Prentice Hall PTR Body effect Reorganize threshold voltage equation: Vt = Vt0 + Vt Threshold voltage is a function of source/substrate voltage Vsb. Body effect is the coefficient for the Vsb dependence factor. (I am skipping this slide as it is replicated in my changes) Modern VLSI Design 3e: Chapter 2 Copyright 1998, 2002 Prentice Hall PTR Example 2-3 (pp-56-57): Threshold voltage of a transistor Vt0 = Vfb + s + Qb/Cox + VII = -0.91 V + 0.58 V + (1.4E-8/1.73E-7) + 0.92 V = 0.68 V Body effect n = sqrt(2qSiNA/Cox) = 0.1 Vt = n[sqrt(s + Vsb) - sqrt(Vs)] = 0.16 V Modern VLSI Design 3e: Chapter 2 Copyright 1998, 2002 Prentice Hall PTR Example 2-3 (pp-56-57): Threshold voltage of a transistor x ox 200 A ox 3.45 1013 F /cm s 0.6v Q f 1.6 108 C /cm 2 si 1.0 1012 N a 1015 /cm 3 N ap 1019 /cm 3 DI 1.0 1012 Cox ox / x ox 3.45 1013 /2 106 1.73 107 C /cm 2 kT N a N dp 10151019 gs ln 0.026ln 0.82V 2 q (1.45 1010 ) 2 ni 1.6 108 V fb gs 0.82 0.91V Cox 1.73 107 Qf 2kT N a 1015 s ln 2 0.026 ln 0.58V q ni 1.45 1010 Qb Qb 2qsiN a s 2 1.6 1019 1012 1015 0.58 1.4 108 VII qDI /Cox 1.6 1019 1012 /1.73 107 0.92V Q Vt 0 V fb s b VII Cox 0.91 0.58 1.4 108 0.92 0.68V 1.73 107 2qsiN a 2 1.6 1019 1012 1015 n 0.1 Cox 1.73 107 Vt n ( s Vsb s ) 0.1 ( 0.58 5 0.58) 0.16 Modern VLSI Design 3e: Chapter 2 Copyright 1998, 2002 Prentice Hall PTR More device parameters Process transconductance k’ = Cox. ( denotes the mobility of channel electrons or holes) Device transconductance = k’W/L. Saturation Current: Id = 0.5k’ (W/L)(Vgs - Vt) 2 = 0.5 (Vgs - Vt) 2 Modern VLSI Design 3e: Chapter 2 Copyright 1998, 2002 Prentice Hall PTR Channel length modulation length parameter a describes small dependence of drain current on Vds in saturation. Factor is measured empirically. New drain current equation: – Id = 0.5k’ (W/L)(Vgs - Vt) 2(l - a Vds) Equation has a discontinuity between linear and saturation regions---small enough to be ignored. Note: I use a instead of lto avoid confusion with channel parameter l. Modern VLSI Design 3e: Chapter 2 Copyright 1998, 2002 Prentice Hall PTR Gate voltage and the channel gate current source drain Linear region Vds < Vgs - Vt Id Vgs > Vds + Vt Inversion layer gate current source drain Saturation region Vds = Vgs - Vt Id Vgs = Vds + Vt Inversion layer shrinks source gate current drain Id dId/dVds decreases Modern VLSI Design 3e: Chapter 2 Pinch off Channel transconductance decreases Vds > Vgs - Vt Vgs < Vds + Vt Copyright 1998, 2002 Prentice Hall PTR Leakage and subthreshold current A variety of leakage currents draw current away from the main logic path. The sub-threshold current is one particularly important type of leakage current. (When the gate voltage is just below the threshold voltage, the point of weakinversion) Modern VLSI Design 3e: Chapter 2 Copyright 1998, 2002 Prentice Hall PTR Types of leakage current. Weak inversion current (sub-threshold current). Punch-through currents. (When the drain to source voltage gets to be too high, the source and drain regions may be shorted.) Gate oxide tunneling-- Hot carriers (For short channels, electrons may accumulate into the gate oxide, leading to changes in threshold conditions.) Reverse-biased pn junctions Drain-induced barrier lowering (Shift in threshold level to increase in drain voltage-- higher current flow near cut-off when the drain voltage increases) Gate-induced drain leakage (As gate oxide layer becomes very thin, channel current may leak into the gate-- non-ideal capacitor) Modern VLSI Design 3e: Chapter 2 Copyright 1998, 2002 Prentice Hall PTR Subthreshold current Subthreshold current: www4.ncsu.edu:8030/~vmisra/MOS.ppt and physics of MOSFET IDS I ' GS T L 2q S N A 2 2 F VSB 2 t W log10 IDS log 10 L 1 1 q S n kTln(10) W q(VGS VT ) nkT I e 1 e qVDS kT L W q(V V ) nk T I e when Vds >> q/kT IDS Modern VLSI Design 3e: Chapter 2 n 1 2 2 F VSB q VGS VT I log 10 e kT n S is called the sub-threshhold swing; smaller values of S are desirable Copyright 1998, 2002 Prentice Hall PTR The modern MOSFET Features of deep submicron MOSFETs: – epitaxial layer for heavily-doped channel; – (both n and p wells over an epitaxial layer) – reduced area source/drain contacts for lower capacitance; – lightly-doped drains to reduce hot electron effects; – silicided poly, diffusion to reduce resistance. Modern VLSI Design 3e: Chapter 2 Copyright 1998, 2002 Prentice Hall PTR Circuit simulation Circuit simulators like Spice numerically solve device models and Kirchoff’s laws to determine time-domain circuit behavior. Numerical solution allows more sophisticated models, non-functional (tabledriven) models, etc. Modern VLSI Design 3e: Chapter 2 Copyright 1998, 2002 Prentice Hall PTR Spice MOSFET models Level 1: basic transistor equations of Section 2.2; not very accurate. Level 2: more accurate model (effective channel length, etc.). Level 3: empirical model. Level 4 (BSIM): efficient empirical model. New models: level 28 (BSIM2), level 47 (BSIM3). (BSIM4-July 2005- for submicron MOS simulation--Level 54) Modern VLSI Design 3e: Chapter 2 Copyright 1998, 2002 Prentice Hall PTR Some (by no means all) Spice model parameters L, W: transistor length width. KP: transconductance. GAMMA: body bias factor. AS, AD: source/drain areas. CJSW: zero-bias sidewall capacitance. CGBO: zero-bias gate/bulk overlap capacitance. Modern VLSI Design 3e: Chapter 2 Copyright 1998, 2002 Prentice Hall PTR