Document

advertisement

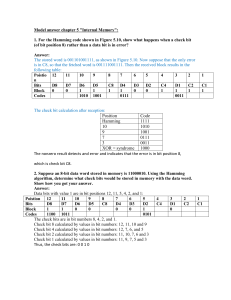

Computer Organization and Architecture SCR 1043 Semester 2, 08/09 Tutorial: Memory System 1. 2. 3. 4. 5. 6. 7. 8. 9. 10. What is the difference between internal and external memory? Differentiate primary, secondary and tertiary storage. What are the differences among sequential access, direct access and random access? Compare and contrast principle of locality Explain with diagram memory hierarchy concept. Discuss access time & memory cycle time. What is the difference between DRAM and SRAM in terms of application? What is the difference between DRAM and SRAM in terms of characteristics such as speed, size, and cost? Compare SDRAM and DDR SDRAM? Memory word size = 32 bit, block size = 4K words a. Find memory capacity if total blocks = 512 blocks Memory capacity = no of blocks * block size * word size = 512 * 4x210 *32 = 67108864 bits = 226bits =64Mbits b. Find number of blocks if main memory capacity 8Mbit No of blocks= memorycapacity 8 x 2 20 64blocks blocksize * wordsize 4 x210 x32 11. Total blocks = 16K, block size = 128 words, memory word size = 64 bit, find memory capacity. Memory capacity = no of blocks * block size * word size = 16x210 * 128 *64 = 134217728 bits = 227 bits =128Mbits 12. Consider a dynamic RAM that must be given a refresh cycle 64 times per ms. Each refresh operation requires 150 ns; a memory cycle requires 250 ns. What percentage of the memory’s total operating time must be given to refreshes? 1ms 4000times in 1ms : refresh = 64 times, memory cycle = 250ns 64 x150ns 9600ns x100% 0.96% therefore, % refresh time = 4000 x 250ns 1000000ns 13. What are the differences among direct mapping, associative mapping and setassociative mapping? A block direct mapping cache has lines/slot that contains 4 words of data. The cache size is 64Kline and the main memory capacity is 16Mbytes. a. How many bits are used for required to access all addresses of a main memory address? 16Mbyte = 24 x 220 = 24 bits b. How many bits required to access individual for words in cache? 4 bytes = 22 = 2 bits c. How many bits required to access all for lines/slots in cache? 64Kline = 26x 210 = 16bits d. Draw the format for main memory address by specifying the size of tag, line/slot and word. 14. Computer Organization and Architecture SCR 1043 Semester 2, 08/09 Tag= 24-16-2 = 6bits ,line=16bits ,word = 2bits e. Given the following main memory address 3AFF80h, find the values for tag, line/slot and word field in hexadecimal. Tag line word 0011 10 10 1111 1111 1000 00 00 Tag = 00 1110 = 0Eh, Line = 10 1111 1111 1000 000 =BFE0h, word =00 = 0h tag 3Fh 15. f. What is line size (cache word/cache block size)? = tag + (no of word per line * word size) = 6 +(4 * 8) = 38 bits for each line g. Given the following information, find the main memory address in hexadecimal. line/slot word 11 word 10 word 01 word 00 9DA3h Data Tag line word 11 1111 1001 1101 1010 0011 10 = FE768Eh A block direct mapping cache has lines/slot that contains 4 words of data. The cache size is 16Kline. Main memory contains 16K blocks of 128 byte each. a. What is the total capacity of main memory in Mbytes? 2Mbytes b. How many bits are used for main memory address? 21bits c. How many bits for words in cache? 2bits d. How many bits for lines/slots in cache? 16K = 24x210 =14bits e. Draw the format for main memory address by specifying the size of tag, line/slot and word. Tag : 5 bits Line: 14 bits Word :2 bits f. Given the following main memory address AFF80h, find the values for tag, line/slot and word field in hexadecimal. Tag line word 0 1010 1111 1111 1000 0000 -- tag =0A, line = 3FE0, word = 0 g. What is line size (cache word/cache block size)? = tag + (no of word per line * word size) = 5 +(4 * 8) = 37 bits for each line h. Given the following information, find the main memory address in hexadecimal. Tag line word 1 1111 00 1101 1010 0011 00 = 1F368Ch tag line/slot 1Fh DA3h word 11 word 10 word 01 word 00 Data 16. 17. Computer Organization and Architecture SCR 1043 Semester 2, 08/09 Consider a machine with a byte addressable main memory of 216 bytes and block size of 8 bytes. Assume that a direct mapped cache consisting of 32 lines is used with this machine. a. How is a 16-bit memory address divided into tag, line number, and byte number? Tag-8,line-5,word-3 b. Into what line would bytes with each of the following address be stored? 0001 0001 0001 1011-- 03 1100 0011 0011 0100 -- 06 1101 0000 0001 1101 -- 03 1010 1010 1010 1010 -- 15 c. Suppose the byte with address 0001 1010 0001 1010 is stored in the cache. What are the addresses of the other bytes stored along with it? 0001 1010 0001 1000 0001 1010 0001 1001 0001 1010 0001 1011 0001 1010 0001 1100 0001 1010 0001 1101 0001 1010 0001 1110 0001 1010 0001 1111 d. How many total bytes of memory can be stored in the cache? For each line, no of bits = tag + (no of word* word size) = 8 + (8 *8) = 72 bits 2304 288bytes For 32 lines , total no of bits = 32 * 72= 2304 bits = 8 e. Why the tag is also stored in the cache? A set associative cache size of 16Kline divided into 2-line sets (2-way) with block a line of of 4 words. Main memory capacity is 32Mbyte. a. How many bits are used for main memory address? 25 bits b. How many modules (sets) in cache? Set = 16K/2 = 8K c. How many bits for set numbers? 13 bits d. How many bits for block words? 2 bits e. Show the format of main memory addresses with tag, set and word bits. Tag: 25-13-2 =10bits, set- 13 bits, word 2 bits f. What is cache address (in hexadecimal) for the following main memory address 133AC0Bh? 01 0011 0011 1010 1100 0000 1011 -- 2B02h g. What is line size (cache word/cache block size)? = tag + (no of word per line * word size) = 10 +(4 * 8) = 42 bits for each line h. What is main memory address (in hexadecimal) for the following cache data? Tag Set word 11 word 10 word 01 word 00 34Ah Tag,set,word 1B5Ch Data 10bit 13 bits 2 bits = 11 1000 1010 1 1101 0101 1100 01 Computer Organization and Architecture SCR 1043 Semester 2, 08/09 – group 4bits from left : the address – 1C57571h 18. A set associative cache size of 64Kline divided into 4-line sets (4-way) with block of 4 words. Main memory capacity is 64Mbyte. a. How many bits are used for main memory address? 64M = 26x220 =26 bits lines 64 K 16 Ksets b. How many modules (set) in cache? = noofways 4 c. How many bits for set numbers? =16K = 24x210 = 14 bits d. How many bits for block words? = 4 = 22 = 2bits e. Show the format of main memory addresses with tag, set and word bits. Tag = 26-14-2=10 bits, set =14 bits,word=2 bits f. What is cache address (in hexadecimal) for the following main memory address 377AC01h? 11 0111 0111 1010 1100 0000 0001 = 2B00h g. What is line size (cache word/cache block size)? = tag + (no of word per line * word size) = 10 +(4 * 8) = 42 bits for each line h. What is main memory address (in hexadecimal) for the following cache data? Tag Set word 11 word 10 word 01 word 00 34Ah 3B5Ch Data 11 0100 1010 11 1101 0101 1100 11 = 34AF573h 19. Consider a 32-bit microprocessor that has an on-chip 16KByte four-way setassociative cache. Assume that the cache has a line size of four 32-bit words. Draw a block diagram of this cache showing its organization and how the different address fields are used to determine a cache hit/miss. Where in the cache is the word from memory location ABCDE8F8 mapped? 32 microprocessor – address bits =32bits 16 K 4 K 12bits Set = 4 Word = 4 = 2bits Tag = 32-12-2 = 18 bits, set = 12 bits,word = 2 bits Address ABCDE8F8 = 1010 1011 1100 1101 1110 1000 1111 1000 = set address A3Eh 20. An associative cache has tags that contain 4 words of data. The cache size is 16Kline. Main memory capacity is 16Mbyte. Computer Organization and Architecture SCR 1043 Semester 2, 08/09 a. How many bits are used for main memory address? 16M = 24x220 =24 bits b. How many bits for words in cache? 4 = 22 = 2bits c. How many bits for tag in cache? For associative: tag = 24-2 = 22 bits d. Draw the format for main memory address by specifying the size of tag and word. Associative has only 2 field : tag = 22 bits and word = 2 bits e. Given the following main memory address ABCDEFh, find the values for tag and word field in hexadecimal. Tag word 1010 1011 1100 1101 1110 11 11 f. What is line size (cache word/cache block size)? = tag + (no of word per line * word size) = 22 +(4 * 8) = 54 bits for each line g. Given the following main memory address 777777h, find the values for tag and word field in hexadecimal. Tag word 0111 0111 0111 0111 0111 01 11 h. Given the following information, find the main memory address in hexadecimal. tag word 11 word 10 word 01 word 00 23341Fh 10 0011 0011 0100 0001 1111 00 = 8CD07Ch Data 21. 22. Computer Organization and Architecture SCR 1043 Semester 2, 08/09 Assume that 22% of the instructions in a program are data accesses. The cache hit ratio is 95% and the hit time is 1 cycle, but the miss penalty is 10 cycles. Find AMAT. AMAT = Hit time + (Miss rate x Miss penalty) = 1+ 0.05*10 = 1.5 cycles A CPU has access to 2 levels of memory. Level 1 contains 10000 words and has access time 0.001 ms; level 2 contains 100,000 words and has access time 0.01 ms. Assume that if a word to be accessed is in level 1, then, the CPU accesses it directly. If it is in level 2, then the word is first transferred to level 1 and then accessed by the CPU. For simplicity, we ignored the time required for the CPU to determine whether the word is in level 1 or level 2. Suppose 90% of the memory access are found in the cache. Find average access time to a word? Average acces time = (0.9)(0.001 ms) + (0.1)(0.001 ms +0.01 ms) =0.002µS Computer Organization and Architecture SCR 1043 Semester 2, 08/09 Memory Interleaving Example (a). Given a memory capacity of 1Kwords and address 298h with the memory bank/module size 256 word. Draw and determine the memory bank/module address (LOI) and the address of the word in the bank/module for address 298h: Memory capacity = 1Kwords = 210 = 10 bits for main memory address Module/bank size(capacity) = 256 = 28 = 8 bits for word in bank/module Total number of bank/module = memory capacity/module(bank) size = 210 /28 = 4 module/bank There are 4 memory banks/modules, 22, thus 2 bit for the banks/modules address Memory address = 298h = 1010 0110 00 Memory bank/module address = 00 Address of the word in the bank/module = 1010 0110 = A6h 1111 1111 00b 3FCh 1020 1021 1022 1023 M0 (00) M1 (01) M2 (10) M3 (11) 0 1 2 3 1111 1111 11b 3FFh 0A6h 000h 003h 0000 0000 11b 0000 0000 00b 2. Given memory capacity 1K with the memory bank/module size 256 word. Draw the modular memory for high order interleaving (HOI). Memory capacity = 1Kwords = 210 = 10 bits for main memory address Module/bank size(capacity) = 256 = 28 = 8 bits for word in bank/module Total number of bank/module = memory capacity/module(bank) size = 210 /28 = 4 module/bank There are 4 memory banks/modules, 22, thus 2 bit for the banks/modules address Since these are high order bits, therefore its called HOI 0FFh h 0011111111 255 0111111111 511 1011111111 767 111111111 1023 3FFh 000h 000h M0 0000000001 0000000000 0 M1 0100000001 0100000000 256 M2 1000000001 1000000000 512 These bits are same in all 4 modules. M3 1100000001 1100000000 768 300h Computer Organization and Architecture SCR 1043 Semester 2, 08/09 Extra Question (Not Covered in Syllabus) 1. What is the general relationship among access time, memory cost and capacity? 2. What are the advantages of using glass substrate for a magnetic disk? 3. How are data written onto and read from a magnetic disk? 4. Define the terms track, cylinder and sector. 5. What is Virtual Memory? 6. How is paging implemented? Use diagram to aid your explanation. 7. How is segmentation implemented? Use diagram to aid your explanation. 8. Compare the advantages and disadvantages between paging and segmentation. 9. Describe TLB.