WEST VIRGINIA UNIVERSITY

advertisement

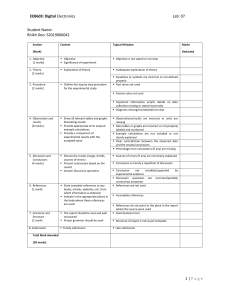

WEST VIRGINIA UNIVERSITY COLLEGE OF ENGINEERING AND MINERAL RESOURCES Lane Department of Computer Science and Electrical Engineering Fall 2001 Multiplexers and De-Multiplexers LAB 5 (Deadline: One Week) CpE 272: Digital Logic Lab http://www.csee.wvu.edu/classes/cpe72 Objectives: To understand how a multiplexer works and implement a simple logic function. To understand how a De-multiplexer works and implement a simple logic function. Part 1 -- Multiplexer: A Multiplexer is a device that connects several inputs to one single output. This output maybe selected by the user using control switches. For instance it there are 2 control switches the user may select from 2^2 = 4 inputs. If there are 4 inputs then the user may select 2^4 = 16 possible inputs. To understand how a multiplexer works, consider the following analogy. Say you want to make a cup of coffee using hot water, sugar, coffee and cream and a multiplexer you would set up your system in the following way. Hot Water Coffee output Sugar A B Function 0 0 1 1 0 1 0 1 output = Water output = Coffee output = Sugar output = Cream Cream A B Control Lines for Input Select Multiplexers used in digital circuits often consist of several data inputs, a number of select inputs and two complementary outputs. When a binary code is applied to the SELECT inputs, the corresponding data at the input will be routed to the output. In this lab experiment, you will investigate the operation of a 74LS151 IC, an 8line-to-1-line multiplexer with 8 data inputs, 3 SELECT inputs, an ENABLE input and 2 complementary outputs. Some common uses. Select One-of-Eight Data Sources Perform Parallel-to-Serial Conversion Multiplex Eight Lines to One Boolean Function Generator Part 2 – De-Multiplexer: De-multiplexers are often used as a vital component of memory decoding circuitry. In fact, until only recently, many PCs relied upon banks of these chips to select between memory banks. Some PCs today still implement them in a more limited sense. The 74LS138 is a 3 to 8 Decoder / De-multiplexer. By selecting a value of 0 through 7 on the A, B, C inputs, only one of the Y0 through Y7 outputs is selected. These outputs are typically used to drive the enable inputs on other chips. In this way, only one of the chips in a given bank is selected. Another use of decoders is the implementation of elementary logic functions similar to the use of a MUX. A De-Multiplexer (affectionately known as DMUX) works in the following manner. All the outputs in an active low De-Mux are high except for the one selected by the control switches. For instance if the Control inputs were A=0 and B = 0 then the corresponding output line will have the output of 0 and all remaining lines will remain high. 00 01 10 11 AB W X Y Z 00 01 10 11 0 1 1 1 1 0 1 1 1 1 0 1 1 1 1 0 74LS151 (8 line to 1 line Multiplexer) The logic and Schematic view of 74LS151 multiplexer IC shown below. D0 D1 D2 D3 D4 D5 D6 D7 E Y W A B C The E stands for Enable. To turn the device on this pin has to be grounded. (It’s Active Low). Task 1: Figure out the proper way to use the 74LS151 to implement the following Boolean function. Show your TA the truth table for credit and working circuit for credit. F(A,B,C) = A’B’C + AB’C’ + A’BC’ Hint: Think about the coffee analogy.. in this instance your ingredients are definitely not sugar and cream. 74LS138 (De-Multiplexer) The Schematic view of 74LS138 multiplexer IC shown below. Task 2: Figure out the proper way to use the 74LS138 to implement the following Boolean function. Show your TA the truth table for credit and working circuit for credit. F(A,B,C) = A’B’C + AB’C’ + A’BC’ Hint: You will need to use additional logic gates to complete your design Because you have 8 outputs where you need only one. LOGIC BLOCK DMUX C B A F(A,B,C) GRADING FOR LAB 5 TASK 1: Successful Implementation 20 Points. TASK 2: Successful Implementation 40 Points. LAB Report: 40 Points (please use the following template) In Light of the awful reports submitted by students we are installing a template which students must follow while writing their reports. Title Page: 5 Points. Design For Task 1: 10 Points. (Diagram, Truth table and verbal description) Design For Task 2: 15 Points. (Diagram, Truth Table and verbal description) Questions: 10 Points. (listed below) (2 Points each) Q1. Discuss one advantage of using a multiplexer over a regular logic circuit. Q2. If a hypothetical Multiplexer had 64 select lines, how many inputs can it select? Q3. You need to design an address decoder for a 64K memory block. How many select lines will you need ? (An address decoder decodes individual memory cells in a memory block). Q4. Name the two chips we learned about in today’s lab. Q5. What did you think about today’s lab. PRELAB for Next Week. (10 Points) Come up with a design for a full adder. You may use the Internet or textbook for research. You must also explain the difference between a half adder and a full adder.