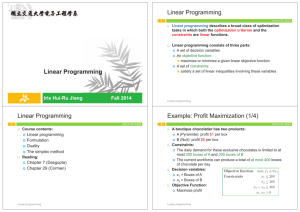

slides

advertisement

OPTIMAL WIRING TOPOLOGY FOR

ELECTROMIGRATION AVOIDANCE

CONSIDERING MULTIPLE LAYERS

AND OBSTACLES

IRIS HUI-RU JIANG

HUA-YU CHANG

CHIH-LONG CHANG

IRIS Lab National Chiao Tung University

Outline

IRIS H.-R. JIANG

2

Introduction to EM

Problem & properties

Our approach

Experimental results

Conclusion

WiT - ISPD'2010

Electromigration

IRIS H.-R. JIANG

3

Electromigration (EM)

An extremely dense electron flow (electron wind) knocks off

atoms within the wire and moves them away

This transport leaves a gap at one end and increase the stress at

the other

Possible failures: open-circuit / short-circuit

E

e-

electrical field

electron wind

FE

Cu+

FP

FE << FP

Cu+

void

open

WiT - ISPD'2010

hillock

short

SANYO Semiconductor Co., Ltd.

Electromigration Is a Reliability Issue

IRIS H.-R. JIANG

4

EM is a wear-out failure

Triggered after being used for a period of time

Measured in terms of mean time to failure (MTTF)

Black’s equation, TED-1969

Current density and working temperature

Worsened for advanced technology nodes

EM/ mixed-signal

breakdown

Signal nets / power network in analog

designs

Technology file gives the upper

bound of safe current density Jmax

under a working temperature

high current densities

WiT - ISPD'2010

J Electron Test, 2009

EM Reliability (1/2)

IRIS H.-R. JIANG

5

EM simulation/analysis

Because EM occurs only after a circuit has been used for a

period of time, the defect chips cannot be filtered out during

product testing.

It is desired to characterize the realistic current values for each

terminal/wire and to identify the wires that are potentially

threatened by EM.

Wiring topology for EM

WiT - ISPD'2010

EM Reliability (2/2)

IRIS H.-R. JIANG

6

EM analysis/estimation

Wiring topology for EM

A thin wire should be widened for EM safety.

Conventional EM fixing is applied at post-layout, which may use

many routing resources and layout changes.

If a good wiring topology considering EM is applied to a router,

we may immune EM with much fewer routing resources.

e.g.,

Adler & Barke, DATE-2000

Adler et. al, DAC-2000

Lienig & Jerke, ASPDAC-2003

Yan & Chen, APCCAS-2008

WiT - ISPD'2010

EM Routing

IRIS H.-R. JIANG

7

The routing resource is measured by the total wire area.

The wire width is determined by EM-safe current density instead

of minimum printable width.

-5

-5

+7

source

7

+3

-2

-8

5

+7

+3

sink

+3

7

-2

-8

-4

7

3

-2

2

2

4

+9

-4

+3

1

-8

1

2

5

+9

2

-5

2

+7

-2

-8

2

1

-5

3

+7

4

+9

-4

+9

-4

Assume a unit width wire can carry one-unit current (normalized to 1)

-5

-5

+7

5↑

7↓

5←

12↓

+3

2←

+7

5↑

7↓

7↓

+3

-8

7↑ 2→ -2

-8

4↓

9↑

1↑

+3

2↑

-2

-5

-5

+7

3→

+7

5↑

5↑

7↓

8↓

-8

2↑

1↑

4↑

-2

1←

+3

2→

2→

2→

-4

+9

Minimum WL = 33

Area = 182

WiT - ISPD'2010

7←

5←

-4

ASPDAC-2003

Area = 154

2→

5←

4↓

+9

-4

+9

APCCAS-2008

Area = 144

-2

3↑

-8

4←

-4

5↑

+9

Ours

Area = 142 (optimal)

Our Contribution

IRIS H.-R. JIANG

8

Prior works tended towards heuristics

State-of-the-art results

-5

5

+7

7

+7

+3

-5

3

+3

7

2

-2

-2

Claim:

-8

-8

2

1

This problem1belongs to class

P instead of NP-hard.

2

2

5

4

Proof:

+9

+9

-4

-4

The greedy-choice property.

Method:

-5

-5

A strongly

polynomial

time

algorithm.

5↑

+7

+7

7↓

7↓

+3

+3

2↑

-8

-2

3→

5↑

-8

2↑

1↑

4↑

-2

2→

1↑

7←

5←

-4

ASPDAC-2003

DT-based

Area = 154

WiT - ISPD'2010

2→

5←

4↓

+9

-4

+9

APCCAS-2008

Greedy

Area = 144

Outline

IRIS H.-R. JIANG

9

Introduction to EM

Problem & properties

Our approach

Experimental results

Conclusion

WiT - ISPD'2010

Wiring Topology for EM Avoidance (TEA)

IRIS H.-R. JIANG

10

Input

A set S = {s1, s2, …, sm} of m current sources

A set T = {t1, t2, …, tn} of n current sinks

Each current source i (sink j) is associated with its flow

The maximum tolerable current density Jmax

The minimum feasible wire width wmin for each routing layer/via

Output

A wiring topology to connect all current sources and sinks in S+T

Minimum total wire area of its detailed routing tree

Sufficient current for each wire segment: f ∝ w

Kirchhoff’s current conservation law

Remarks:

f ∝ w: The wire width offering one unit current is a layer-specific

constant.

The current values can be DC, RMS, peak, average currents

under different EM conditions and for various signal types.

Feasibility: ∑fsi + ∑ftj = 0

WiT - ISPD'2010

Wirelength: Abstraction

IRIS H.-R. JIANG

11

2D

(x1, y1) p1

(x1, y1) p1

No obstacles

abstraction

ly =|y1 - y2|

l(p1, p2)

= lx+ly

lx =|x1 - x2|

3D

With obstacles

rectilinearization

p2 (x2, y2)

(x1, y1, z1)

p1

the minimum

accumulated

area cost for

one unit current

WiT - ISPD'2010

l(p1, p2)

p2 (x2, y2)

(x1, y1, z1)

p1

abstraction

rectilinearization

p2

(x2, y2, z2)

p2

(x2, y2, z2)

Wire Area: Superposition

IRIS H.-R. JIANG

12

Same wire area

s1

s1

(xs1, ys1, fs1)

s1

fs1

fs1

fs1

fs2

t1

t1

(xt1, yt1, ft1)

(xs1, ys1, fs1)

fs1

fs1

t1

fs1+fs2

WiT - ISPD'2010

(xs2, ys2, fs2)

t1

additive

Goal:

fs2

(xs2, ys2, fs2)

Find

the

property

of

the

optimal

wiring

topology.

s2

s2

⇒

The

wire area estimated by the wiring topology =

Area may

vary

s1

that at detailed

routing

s1

s2

fs1+fs2

fs2

s2

fs1

fs1+fs2

t1

fs1+fs2-fs1

= fs2

(xt1, yt1, ft1)

s2

s1

fs1+fs2

s2

additive

t1

The Greedy-Choice Property (1/3)

IRIS H.-R. JIANG

13

The generic form: 2 sources s1, s2 and 1 sink t1.

fs1 + fs2 + ft1 = 0

We prove the greedy-choice property

t1

s1

(xs1, ys1, fs1)

t1

s2

(xt1, yt1, ft1)

(xs2, ys2, fs2)

WiT - ISPD'2010

Symmetric

s1

(xt1, yt1, ft1)

(xs1, ys1, fs1)

t2

(xt2, yt2, ft2)

The Greedy-Choice Property (2/3)

IRIS H.-R. JIANG

14

Prove by exchange argument.

s1

fs1

fs2

fs1+fs2

fs2

t1

s2

A{s2 → s1 → t1}

A{s1 → t1} + A{s2 → t1}

Axes are independent.

Consider 3 points z1, z2 and z3 on an axis: fix z1 and z3, move z2

⇒ |z1 - z2| + |z2 - z3| ≥ |z1 - z3|

z2

t1

s2

A{s1 → s2 → t1}

fs1

fs1+fs2

t1

s2

s1

s1

z1

z2

z3

z2

Z

A{s1 → s2 → t1} or A{s2 → s1 → t1} ≥ A{s1 → t1} + A{s2 → t1}

WiT - ISPD'2010

The Greedy-Choice Property (3/3)

IRIS H.-R. JIANG

15

Corollary: The greedy-choice property holds at a general multilayer space with obstacles.

The greedy-choice property

⇒

1. We can consider wire connections

only from sources to sinks.

2. The wire area keeps the same

after the slant edges of the greedychoice property are rectilinearized.

WiT - ISPD'2010

Outline

IRIS H.-R. JIANG

16

Introduction to EM

Problem & properties

Our approach

Experimental results

Conclusion

WiT - ISPD'2010

Overview of WiT (1/2)

IRIS H.-R. JIANG

17

-5

+7

Current sources

(xsi, ysi, fsi)

Current sinks

(xtj, ytj, ftj)

Layer-specific

Jmax, wmin

+3

WiT

-2

-8

1. Length calculation

+9

2. Wiring topology generation

3. Detailed routing

-4

+7

-5

+3

Current-Correct Rectilinear Steiner tree

-2

-8

+9

-4

WiT - ISPD'2010

10

Overview of WiT (2/2)

IRIS H.-R. JIANG

18

+7

Current sources

(xsi, ysi, fsi)

Current sinks

(xtj, ytj, ftj)

Layer-specific

Jmax, wmin

-5

(7,1)

(9, 7)

(10,4)

+3

WiT

1. Length calculation

(6, 2)

(16,1)

2. Wiring topology generation

(10,4) +9

-8

3. Detailed routing

Current-Correct Rectilinear Steiner tree

-4

+7

→

-5

(5, 5) ↑

(8, 7)

(1, 8)

-8 ←

+3

(2, 3) (4, 2)

→

↓

-2

(4, 5) ↑

(5, 1) ↑

-4

WiT - ISPD'2010

-2

+9

← (10, 5)

Flow Network

IRIS H.-R. JIANG

19

Triple: (wirelength, flow, capacity)

Feasible flow: 0 ≤ fi,j ≤ ci,j = min(|fsi|, |ftj|)

(l1,1, f1,1, c1,1)

t1

s1

|ft1|

|fs1|

t2

s2

ss

|fsi|

.

.

.

si

|fsm|

.

.

.

sm

(l,i,j, fi,j, ci,j)

.

.

.

.

.

.

(lm,n, fm,n, cm,n)

tj

.

.

.

tn

(0, fss, fss)

WiT - ISPD'2010

.

.

.

|ftj|

|ftn|

tt

Residual Graph

IRIS H.-R. JIANG

20

Forward edge: push flow

Backward edge: return flow

Flow network:

|fsi|

0 ≤ fi,j ≤ ci,j = min(|fsi|, |ftj|)

si

Residual graph:

c’i,j = ci,j - fi,j, l’i,j = +li,j

tj

si

c’i,j = -fi,j, l’i,j = -li,j

WiT - ISPD'2010

tj

|ftj|

Wire Area Optimization

IRIS H.-R. JIANG

21

Triple: (wirelength, flow, capacity)

Flow network:

Residual graph:

t1

1

(7,0,1)

flow

(7,-,1)

t1

1

-: undetermined

s1

(12,1,1)

s1

(-12,-,-1)

3

3

(7,3,3)

3

s2

(10,2,3)

Area

= 7*0 + 7*3 + 12*1 +10*2

= 53

WiT - ISPD'2010

5

3

t2

s2

(-7,-,-3)

(10,-,1)

(-10,-,-2)

5

t2

Negative Cycle Detection (1/2)

IRIS H.-R. JIANG

22

Theorem: Negative-Cycle Removal: If the flow assignment of a

flow network is optimal, there exists no negative cycles in its

residual graph.

Residual graph:

(7,-,1)

s1

3

t1

1

Push a flow along the

negative cycle

⇒

1. Reduce the area cost

2. Flow = min residual cap

Negative

(-12,-,-1)

cycle!

3

s2

(-7,-,-3)

(10,-,1)

(-10,-,-2)

7 + (-12) + 10 + (-7) = -2

WiT - ISPD'2010

5

t2

Negative Cycle Detection (2/2)

IRIS H.-R. JIANG

23

Theorem: Negative-Cycle Removal: If the flow assignment of a

flow network is optimal, there exists no negative cycles in its

residual graph.

Residual graph:

Negative

cycle!

Flow network:

1

(7,1,1)

s1

t1

3

(12,0,1)

3

(7,2,3)

(-7,-1,-3)

3

s2

1

(7,1,1)

s1

(-12,-1,-1)

t1

(10,1,1)

5

t2

3

s2

(10,3,3)

5

t2

Area

= 7*1 + 7*2 + 12*0 +10*3

= 51

WiT - ISPD'2010

The WiT Algorithm

IRIS H.-R. JIANG

24

WiT(S, T)

1. construct the flow network and calculate paths and lengths

2. if the given flow at sources/sinks is legal then

3.

find an initial flow assignment

4. while there exists a negative cycle in the residual graph do

5.

remove the negative cycle

6.

update the flow network

7.

update the residual graph

8. rectilinearize the wiring topology by stored paths

Initial solution:

For efficiency, we select the greedy method.

For effectiveness, we choose the minimum wirelength as the

greedy rule.

WiT - ISPD'2010

Outline

IRIS H.-R. JIANG

25

Introduction to EM

Problem & properties

Our approach

Experimental results

Conclusion

WiT - ISPD'2010

Results

IRIS H.-R. JIANG

26

Implementation:

C++ language with LEDA package

NB with an Intel® Core™2 CPU T9400 of 2.53 GHz frequency and 4

GB memory under Windows Vista™ Business 64 bit Service Pack 1

OS.

Testcase

INP1 INP2 INP3 INP4 IND1 IND2 IND3 IND4 IND5 RT01

RT02

RT03

RT04

RT05

#Terminals

7

16

10

16

10

10

10

25

33

75

180

303

475

850

Area

154 122 210

32 6,661 79,400 FAIL 23,112 31,466 FAIL

FAIL

FAIL

FAIL

FAIL

ASPDAC-2003

Runtime (s)

0.001 0.002 0.001 0.002 0.038 0.016

0.016 0.040

Area

144

98

128

40 5,319 79,000 6,181 16,000 20,814 189,437 10,638,884 3,360,716 6,475,941 59,207,240

Runtime (s)

0.001 0.002 0.001 0.002 0.001 0.001 0.001 0.003 0.005 0.120

4.958

45.553 297.806 8,573.453

Refined area

142

90

116

32 5,301 74,200 5,513 13,728 17,044 144,071 7,151,286 2,325,806 4,205,757 37,318,054

APCCAS-2008

Gain

2

8

12

8

18 4,800 668 2,272 3,770 45,366 3,487,598 1,034,910 2,270,184 21,889,186

#Iterations

1

2

1

1

1

3

15

20

29

147

622

1,938

4,288

9,238

Refine runtime (s) 0.000 0.000 0.001 0.000 0.000 0.001 0.001 0.002 0.003 0.028

4.741

0.496

28.883 440.429

Initial area

142

94

116

32 5,301 78,200 5,629 15,092 19,624 156,489 8,139,250 2,840,420 4,831,845 45,677,120

Initial runtime (s) <0.001 <0.001 <0.001 <0.001 <0.001 <0.001 <0.001 <0.001 <0.001 <0.001 0.015

0.042

0.109

0.425

Final area

142

90

116

32 5,301 74,200 5,513 13,728 17,044 144,071 7,151,286 2,325,806 4,205,757 37,318,054

WiT

Gain

0

4

0

0

0

4,000 116 1,364 2,580 12,418 987,964 514,614 626,088 8,359,066

#Iterations

0

1

0

0

0

3

2

17

37

78

415

949

1,197

3,487

Total runtime (s) <0.001 <0.001 <0.001 <0.001 <0.001 <0.001 <0.001 <0.001 <0.001 0.016

0.297

1.794

6.489

89.497

Efficient initial solution.

We can refine any initial solution to the optimal.

WiT - ISPD'2010

RT05: 850 Terminals

IRIS H.-R. JIANG

27

ASPDAC-2003

FAILED

WiT - ISPD'2010

APCCAS-2008

Area = 59,207,240

Ours

Area = 37,318,054

Conclusion

IRIS H.-R. JIANG

28

In this paper, we focus on wiring topology generation for

avoiding electromigration for power networks or signal nets in

analog and mixed-signal designs.

The major contribution is that we claim this problem belongs to

class P instead of class NP-hard.

Based on the proof of the greedy-choice property, we

successfully model this problem on a multi-source multi-sink

flow network and then can solve it in a strongly polynomial

time.

Experimental results prove the efficiency and effectiveness of

our algorithm.

WiT - ISPD'2010

29

Thank You!

Iris Hui-Ru Jiang

huiru.jiang@gmail.com

WiT - ISPD'2010

30

Backup slides

WiT - ISPD'2010

Multi-Source Multi-Sink Circuits?

IRIS H.-R. JIANG

31

Q: What kind of design has multiple sources and sinks?

A: Usual in analog or mixed signal designs, power network, etc.

WiT - ISPD'2010

Non-uniform Temperature Distribution

IRIS H.-R. JIANG

32

Q: What if non-uniform temperature distribution within a chip?

A: This abstraction still works with given temperature

distribution map.

WiT - ISPD'2010