Shi_umd_0117E_14446 - DRUM

advertisement

ABSTRACT

Title of dissertation:

ELECTRO-THERMAL CODESIGN IN LIQUID

COOLED 3D ICS: PUSHING THE POWERPERFORMANCE LIMITS

Bing Shi, Doctor of Philosophy, 2013

Dissertation directed by: Professor Ankur Srivastava

Department of Electrical and Computer Engineering

The performance improvement of today’s computer systems is usually accompanied by increased chip power consumption and system temperature. Modern

CPUs dissipate an average of 70 − 100W power while spatial and temporal power

variations result in hotspots with even higher power density (up to 300W/cm2 ).

The coming years will continue to witness a significant increase in CPU power dissipation due to advanced multi-core architectures and 3D integration technologies.

Nowadays the problems of increased chip power density, leakage power and system temperatures have become major obstacles for further improvement in chip

performance. The conventional air cooling based heat sink has been proved to be

insufficient for three dimensional integrated circuits (3D-ICs). Hence better cooling

solutions are necessary. Micro-fluidic cooling, which integrates micro-channel heat

sinks into silicon substrates of the chip and uses liquid flow to remove heat inside

the chip, is an effective active cooling scheme for 3D-ICs. While the micro-fluidic

cooling provides excellent cooling to 3D-ICs, the associated overhead (cooling power

consumed by the pump to inject the coolant through micro-channels) is significant.

Moreover, the 3D-IC structure also imposes constraints on micro-channel locations

(basically resource conflict with through-silicon-vias TSVs or other structures).

In this work, we investigate optimized micro-channel configurations that address the aforementioned considerations. We develop three micro-channel structures

(hotspot optimized cooling configuration, bended micro-channel and hybrid cooling

network) that can provide sufficient cooling to 3D-IC with minimum cooling power

overhead, while at the same time, compatible with the existing electrical structure

such as TSVs. These configurations can achieve up to 70% cooling power savings

compared with the configuration without any optimization. Based on these configurations, we then develop a micro-fluidic cooling based dynamic thermal management

approach that maintains the chip temperature through controlling the fluid flow rate

(pressure drop) through micro-channels. These cooling configurations are designed

after the electrical parts, and therefore, compatible with the current standard IC

design flow.

Furthermore, the electrical, thermal, cooling and mechanical aspects of 3D-IC

are interdependent. Hence the conventional design flow that designs the cooling configuration after electrical aspect is finished will result in inefficiencies. In order to

overcome this problem, we then investigate electrical-thermal co-design methodology for 3D-ICs. Two co-design problems are explored: TSV assignment and

micro-channel placement co-design, and gate sizing and fluidic cooling co-design.

The experimental results show that the co-design enables a fundamental powerperformance improvement over the conventional design flow which separates the

electrical and cooling design. For example, the gate sizing and fluidic cooling codesign achieves 12% power savings under the same circuit timing constraint and

16% circuit speedup under the same power budget.

ELECTRO-THERMAL CODESIGN IN LIQUID COOLED 3D ICS:

PUSHING THE POWER-PERFORMANCE LIMITS

by

Bing Shi

Dissertation submitted to the Faculty of the Graduate School of the

University of Maryland, College Park in partial fulfillment

of the requirements for the degree of

Doctor of Philosophy

2013

Advisory Committee:

Professor Ankur Srivastava, Chair/Advisor

Professor Joseph JaJa

Professor Shuvra Bhattacharyya

Professor Donald Yeung

Professor Doron Levy

© Copyright by

Bing Shi

2013

ACKNOWLEDGEMENT

I would like to thank my advisor, Professor Ankur Srivastava for the support

and guidance he has provided throughout my time in the Ph.D. program. Thank

you for introducing me to the world of Electronic Design Automation, for giving me

so many opportunities, for helping me every step of the way, for encouraging me in

those hard times.

In addition, I would like to thank Professor Joseph JaJa who helped me a lot in

my Ph.D. oral qualify exam, research proposal and also Ph.D. dissertation. I would

like to thank Professor Shuvra Bhattacharyya for his support on my competition

for ECE dissertation fellowship.

I would also like to thank my committee members, Professor Joseph JaJa, Professor Shuvra Bhattacharyya, Professor Donald Yeung and Professor Doron Levy,

for their time, comments and feedback.

I also thank all past and present members of our lab: Domenic Forte, Yufu

Zhang, Caleb Serafy, Tiantao Lu and Chongxi Bao, for their help, friendship, and

support. I am grateful for all the fun times we have shared throughout the years.

Finally, I would like to thank my parents and my family for their ongoing

support and encouragement. Thank you for all of their love and support over the

course of my long journey as an academic.

ii

Table of Contents

List of Figures

vii

List of Tables

ix

1 Introduction

1.1 Thermal Issues in 3D-ICs . . . . . . . . . . . . . . . . . . . . . . . . .

1.2 Conventional Dynamic Thermal Management . . . . . . . . . . . . .

1.3 Interlayer Micro-fluidic Cooling . . . . . . . . . . . . . . . . . . . . .

1.4 Interdependency between Electrical, Thermal, Reliability and Cooling

1.5 Advantage of Electrical and Cooling System Co-Design . . . . . . . .

1.6 Thesis Outline . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1

2

4

6

7

8

9

2 Background

2.1 Basics of Three Dimensional Integrated Circuit . . . . . . .

2.2 Fundamental Characteristics of Fluids in Micro-channels . .

2.2.1 Conservation Law of Fluid Dynamics . . . . . . . . .

2.2.2 Dimensionless Numbers in Fluid Mechanics . . . . .

2.2.3 Single and Two Phase Flow . . . . . . . . . . . . . .

2.2.4 Laminar and Turbulent Flow . . . . . . . . . . . . .

2.3 Thermal Modeling of 3D-IC with Micro-fluidic Cooling . . .

2.3.1 Distributed RC Thermal Model . . . . . . . . . . . .

2.3.2 Cooling Performance of Micro-channels . . . . . . . .

2.3.3 Overall Thermal Model of 3D-IC with Micro-channels

2.3.4 Thermal Impact of TSVs . . . . . . . . . . . . . . . .

2.4 Modeling of Power Consumption . . . . . . . . . . . . . . .

2.4.1 Dynamic Power Consumption . . . . . . . . . . . . .

2.4.2 Leakage Power Consumption . . . . . . . . . . . . . .

2.4.3 Micro-channel Cooling Power . . . . . . . . . . . . .

2.4.3.1 Straight Micro-channels . . . . . . . . . . .

2.4.3.2 Micro-channels with Bends . . . . . . . . .

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

11

11

12

12

13

15

17

19

19

20

22

23

24

25

26

27

27

29

3 Design of Micro-fluidic Cooling Configurations for 3D-ICs

3.1 Motivation of Micro-Fluidic Cooling . . . . . . . . . . . . . .

3.2 Micro-channel Design Considerations/Constraints . . . . . .

3.2.1 Cooling Power Consumption . . . . . . . . . . . . . .

3.2.2 Non-uniform Power Profile . . . . . . . . . . . . . . .

3.2.3 TSV Constraint . . . . . . . . . . . . . . . . . . . . .

3.2.4 Thermal stress . . . . . . . . . . . . . . . . . . . . .

3.3 Hotspot Optimized Non-Uniform Micro-channel . . . . . . .

3.3.1 Problem Formulation . . . . . . . . . . . . . . . . . .

3.3.2 Heuristic for Micro-channel Placement . . . . . . . .

3.3.3 Workload-balanced Initial Micro-channel Distribution

3.3.4 Micro-channel Cost Assignment . . . . . . . . . . . .

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

33

33

34

35

35

36

37

39

40

41

43

49

iv

3.4

3.5

3.6

3.7

3.8

3.9

TSV Constrained Bended Micro-channel . . . . . . . . . . . . . . .

3.4.1 Motivation of Using Bended Micro-channel . . . . . . . . . .

3.4.2 Problem Formulation . . . . . . . . . . . . . . . . . . . . . .

3.4.3 Overall Micro-channel Design Flow . . . . . . . . . . . . . .

3.4.4 Mincost Flow Based Micro-channel Design . . . . . . . . . .

3.4.4.1 Initialization of Minimum Cost Flow Network . . .

3.4.4.2 Cost Assignment . . . . . . . . . . . . . . . . . . .

3.4.5 Micro-channel Refinement . . . . . . . . . . . . . . . . . . .

3.4.5.1 Temperature and Pumping Power Analysis . . . . .

3.4.5.2 Iterative Micro-channel Optimization . . . . . . . .

Hybrid Cooling Network . . . . . . . . . . . . . . . . . . . . . . . .

3.5.1 Motivation of Hybrid Cooling Network . . . . . . . . . . . .

3.5.2 Algorithm for Hybrid Cooling Network Design . . . . . . . .

3.5.3 Micro-channel Priority Assignment/Update . . . . . . . . .

3.5.4 Thermal TSV Allocation and Sizing . . . . . . . . . . . . . .

3.5.4.1 Basic Thermal TSV Placement Approach . . . . .

3.5.4.2 Modified Thermal TSV Allocation and Sizing Approach . . . . . . . . . . . . . . . . . . . . . . . . .

3.5.4.3 Finding Maximum Independent Set E . . . . . . .

Considering Thermal Variations . . . . . . . . . . . . . . . . . . . .

Cooling Performance of Micro-channel Designs . . . . . . . . . . . .

Runtime Thermal Management Using Micro-channels . . . . . . . .

3.8.1 Algorithm for Micro-fluidic Based DTM . . . . . . . . . . .

3.8.2 Performance of Micro-channel Based DTM . . . . . . . . . .

Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4 Co-design of Electrical and Fluidic Cooling Systems

4.1 Motivation for Co-Design . . . . . . . . . . . . . . . . . . . . . . . .

4.2 Co-optimization of TSV Assignment and Micro-Channel Placement

4.2.1 Problem Formulation . . . . . . . . . . . . . . . . . . . . . .

4.2.2 Algorithm for TSV Assignment and Micro-channel Placement

Co-optimization . . . . . . . . . . . . . . . . . . . . . . . . .

4.2.2.1 Overall Design Flow . . . . . . . . . . . . . . . . .

4.2.2.2 Multi-commodity Minimum Cost Flow Formulation

4.2.2.3 Iterative Optimization . . . . . . . . . . . . . . . .

4.2.3 Computational Simplifications . . . . . . . . . . . . . . . . .

4.2.3.1 Multi Layer Case . . . . . . . . . . . . . . . . . . .

4.2.3.2 Two Layer Case . . . . . . . . . . . . . . . . . . .

4.2.4 Performance of TSV Assignment and Micro-channel Placement Co-design . . . . . . . . . . . . . . . . . . . . . . . . .

4.2.4.1 Comparison of Wirelength and Pumping Power . .

4.2.4.2 Tradeoff Between Wirelength and Pumping Power .

4.3 Co-optimization of Gate Sizing and Micro-Fluidic Cooling . . . . .

4.3.1 Motivation of Simultaneous Gate Sizing and Micro-channel

Distribution . . . . . . . . . . . . . . . . . . . . . . . . . . .

v

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

53

53

54

57

57

58

59

62

62

63

68

68

70

71

72

72

.

.

.

.

.

.

.

.

74

75

80

82

83

84

87

88

91

. 91

. 93

. 95

.

.

.

.

.

.

.

95

95

97

102

103

103

105

.

.

.

.

107

107

110

111

. 111

4.3.2

4.3.3

4.3.4

Modeling of Gate Delay . . . . . . . . . . . . . . . . . . . . . 113

Problem Formulation . . . . . . . . . . . . . . . . . . . . . . . 115

Algorithm for Gate Sizing and Micro-channel Placement Cooptimization . . . . . . . . . . . . . . . . . . . . . . . . . . . 117

4.3.4.1 Step 1: Ideal Heat Sink and Gate Size Co-optimization120

4.3.4.2 Step 2: Micro-channel Distribution for Ideal Case . . 121

4.3.4.3 Step 3: Gate Size and Grid Temperature Refinement 123

4.3.4.4 Step 4: Micro-channel Distribution Refinement . . . 129

4.3.4.5 Step 5: Re-iteration and Stopping Criteria . . . . . . 130

4.3.5 Performance of Gate Sizing and Micro-channel Placement Codesign . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 130

4.3.5.1 Comparison of Power Consumption . . . . . . . . . . 131

4.3.5.2 Comparison of Circuit Delay . . . . . . . . . . . . . 132

4.3.6 Power-Performance Tradeoff . . . . . . . . . . . . . . . . . . . 132

4.4 Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 134

5 Conclusion and Discussion

136

5.1 Conclusion . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 136

5.2 Future Work . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 137

Bibliography

140

vi

List of Figures

1.1

Interdependency between Electrical, Thermal, Reliability and Cooling . . . . . .

2.1

2.2

2.3

2.4

2.5

2.6

2.7

2.8

2.9

2.10

2.11

Stacked 3D-IC with micro-channel cooling system . . . . . . . . .

Control volume of fluid . . . . . . . . . . . . . . . . . . . . . .

(a)-(f) Two phase flow patterns, (g) Evaporation process in a channel

Comparison of single and two phase flow . . . . . . . . . . . . .

(a) Laminar flow pattern, (b) Turbulent flow pattern, (c) Transitional

Fluid in micro-channel with bends . . . . . . . . . . . . . . . .

RC network for 3D-IC thermal modeling . . . . . . . . . . . . .

Micro-channel thermal model . . . . . . . . . . . . . . . . . . .

Thermal resistive network of one 3D-IC layer with micro-channels . .

A 3D-IC grid with thermal TSV . . . . . . . . . . . . . . . . .

Exponential leakage model versus quadratic leakage model . . . . .

3.1

3.2

3.3

Micro-channel and TSV configuration . . . . . . . . . . . . . . . . . . . .

Pumping power versus chip power consumption . . . . . . . . . . . . . . .

Thermal stress inside and surrounding TSV (a) when chip temperature is 100℃,

(b) when chip temperature is 50℃(assuming stress free temperature is 250℃) .

Potential locations of micro-channels: (a) uniform spreading of micro-channels,

(b) workload-balanced micro-channel spreading . . . . . . . . . . . . . . .

Example of formulating mincost flow network, (a) 3D-IC structure, (b) abstract

grid graph, (c) minimum cost flow network . . . . . . . . . . . . . . . . .

(a) Cost initialization, (b) Cost update . . . . . . . . . . . . . . . . . . .

Example of silicon layer thermal profile with TSV and (a) straight, (b) bended

micro-channels . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Example of micro-channel infrastructure design using minimum cost flow . . .

Micro-channel infrastructure design flow . . . . . . . . . . . . . . . . . . .

Cost assignment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Examples of (a) unbalanced cooling demand, (b) different number of bends . .

Example of pairwise cooling workload balance . . . . . . . . . . . . . . . .

Examples of bend elimination . . . . . . . . . . . . . . . . . . . . . . . .

Overall design flow of micro-channel and thermal TSV co-optimization . . . .

Change in interdependence region of a grid (a) after allocating or enlarging a

thermal TSV, (b) after shrinking a thermal TSV . . . . . . . . . . . . . . .

Flow chart of micro-channel placement . . . . . . . . . . . . . . . . . . .

Comparison of Pumping Power . . . . . . . . . . . . . . . . . . . . . . .

Runtime pressure drop control versus fixed pressure drop for (a) group L, (b)

group M, (c) group H . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.4

3.5

3.6

3.7

3.8

3.9

3.10

3.11

3.12

3.13

3.14

3.15

3.16

3.17

3.18

4.1

4.2

4.3

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

flow pattern

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

12

13

16

17

18

18

20

21

23

24

27

. 34

. 35

. 38

. 42

. 47

. 52

.

.

.

.

.

.

.

.

54

55

57

61

64

66

68

71

. 79

. 81

. 83

. 89

Conventional chip design flow . . . . . . . . . . . . . . . . . . . . . . . . .

Thermal profile of one 3D-IC layer, and an example of TSV and micro-channel

allocation where TSVs constraint us from allocating micro-channels at hotspots .

Overall design flow of MCMCF based algorithm . . . . . . . . . . . . . . . .

vii

8

92

94

98

4.4

4.5

4.6

4.7

4.8

4.9

4.10

3D-IC with potential TSV and micro-channel locations . . . . .

Multi-commodity min-cost flow formulation . . . . . . . . . .

Computationally simplifying transformation for multi-layer case

Computationally simplifying transformation for two-layer case .

Tradeoff between wirelength and pumping power . . . . . . . .

Overall design flow . . . . . . . . . . . . . . . . . . . . . .

Delay versus power tradeoff for benchmark 1 . . . . . . . . .

viii

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

100

101

105

106

111

119

133

List of Tables

3.1

Comparison of pumping power . . . . . . . . . . . . . . . . . . . . . . . 84

4.1

4.2

4.3

Problem formulation . . . . . . . . . . . . . . . . . . . . . .

Benchmark Information . . . . . . . . . . . . . . . . . . . .

Comparison between our approach, TSV first and channel first

(Ppump : W , W L : m, temperature: o C) . . . . . . . . . . . .

Comparison of total power consumption (power: W, tcons : ns)

Comparison of circuit performance (power: W, tcons : ns) . . .

4.4

4.5

ix

. . . . . . 96

. . . . . . 108

approach

. . . . . . 108

. . . . . . 132

. . . . . . 133

Chapter 1

Introduction

Moore’s law has predicted a spectacular exponential growth in chip performance. However, in recent years, such performance improvements are slowing down,

leading the research community to investigate alternative technologies that can restore the expected Moore’s law rhythm in the functionality and cost of electronic

products.

The three dimensional integrated circuit (3D-IC), which contains two or more

layers of active electronic components that are stacked vertically, has become a significant technology for achieving continued performance improvements. The 3D-IC

allows a significant increase in device densities, as well as faster on-chip communications compared with equivalent 2D circuits due to the shortening of interconnection

length and increased bandwidth [30][88]. Besides the performance improvement,

3D-IC can also result in overall system energy savings and co-integration of heterogeneous components [22][49].

Despite these advantages, the 3D-IC also brings forth new challenges to chip

thermal management due to the stacked structure.

1

1.1 Thermal Issues in 3D-ICs

Modern CPUs dissipate an average of 70 − 100W power while spatial and

temporal power variations result in hotspots with even higher power density (up

to 300W/cm2 ). The coming years will continue to witness a significant increase in

CPU power dissipation due to advanced multi-core architectures and 3D integration technologies. Increase in CPU power density is usually accompanied by drastic

increase in chip temperature. Nowadays the problems of increased chip power density, leakage power and system temperature have become major obstacles for further

improvements in chip performance. The advent of 3D integration technology, exacerbates the thermal problems on chip since the power density increases dramatically

due to several stacks of microprocessor chips, and also due to constraints imposed

on heat flow paths (by several intermediate layers).

Recent data shows that more than 50% of all IC failures are related to thermal issues [58]. For instance, excessive temperature reduces the electron and hole

mobilities which leads to increase in circuit propagation delay [44][83]; thermal variations and hotspots on chip cause reliability problems such as circuit mismatch and

reduced chip lifetime (due to the cumulative damage caused by excessive temperature) [29][10][50]. Hence, loss of performance and reliability due to unpredictable

thermal hotspots has become a major issue and limiting factor for further performance improvement in modern computer systems.

Furthermore, with continued scaling, the impact of leakage power is growing

as well. Today, up to 50% (or even more) of the total power consumption is leakage

2

power [38]. It has been shown that leakage and temperature are highly interdependent: higher temperature increases the leakage power which in-turn further increases the temperature [47][80][27]. This interdependency increases the importance

and difficulty of chip thermal management. The interdependence between temperature and leakage has been known for years and several attempts have been made

during design time to better estimate/control the leakage and temperature through

various design decisions [66][81]. For example [66] estimates the chip thermal and

leakage profile while accounting for their interdependence, and [81] estimates the

chip leakage profile while accounting for thermal variability.

In convectional computer systems, the thermal issues within the chip are handled at the package level by attaching a large heatsink on the top of the chip which

dissipates heat into surrounding air, together with air cooling based cooling devices

such as fans and air conditioners. Such “remote cooling” approaches have limitations

in the following ways:

1. Fail to account for temporal variations: the processor operation exhibits great

variations during runtime due to the nature of different applications and data.

The demand for resources by different applications also varies. The processor

operation and demand for resources influence the power and thermal states

on-chip, hence the chip power and thermal profiles change during runtime.

Therefore the convectional air cooling that ignores the real time chip operation

and cooling demand is inefficient.

2. Fail to account for spatial variations: the chip power and thermal profiles also

3

exhibit variations spatially since different parts of the chip exhibit different

switching activities. Such variations result in thermal hotspots which are

important issues in electronic systems. The convectional heat sinks usually

provide uniform cooling, which is very inefficient when there are hotspots.

3. Insufficient cooling capability: convectional heat sinks are usually attached at

the top of the chip, which makes it ineffective in removing the heat inside the

chip. Especially for 3D-ICs, the air based cooling has already been proved

to be insufficient. As illustrated in [8], if two 100W/cm2 microprocessors are

stacked on top of each other, the power density becomes 200W/cm2 , which is

beyond the heat removal limits of air cooled heat sinks.

Many efforts have been made to further mitigate the thermal issues in CPU

chips. These efforts can be classified into three categories: CPU thermal management schemes [11][16][20][21][53][64][63], materials with better thermal property

[67][79] and advanced cooling schemes [43][84][46][9]. In this work, we focus on the

new cooling technology and dynamic thermal management for 3D-ICs.

1.2 Conventional Dynamic Thermal Management

Usually, the chip performance and temperature are closely related. In order

to improve the performance delivered by the microprocessor, we could increase the

transistor integration density of the chip, or increase the supply voltage and clock

frequency, which leads to increased chip power consumption and temperature. Dynamic thermal management (DTM), where the chip operation is controlled during

4

runtime for curtailing thermal emergencies, can better address the temporal and

spatial variations of the power and thermal profiles on-chip (in addition to the convectional package level cooling scheme). In conventional DTM schemes, thermal

management can be achieved by controlling processor knobs such as core frequency

and supply voltage [64][25][13][41], scheduling of tasks etc [93], which in effect, control the power dissipation in different parts of the chip. These schemes basically

manage the chip temperature through controlling the heat dissipation rate/pattern.

For example, in dynamic voltage and frequency scaling (DVFS), the supply voltage

and operating frequency of micro-processors are dynamically controlled to reduce

the chip power consumption, thereby reducing the temperature as well. However

decreasing the supply voltage or operating frequency causes a potential performance

reduction. Hence in the conventional DTM schemes, constraining the chip temperature is usually accompanied by reductions in performance.

With the continued application of conventional thermal management techniques, many of today’s electronic systems underperform their inherent physical

limits while operate at the highest power dissipation allowed by the available thermal management technology. CMOS, telecommunications, active sensing and imaging have undergone tremendous technological innovation over the last 40 years.

However, despite the need and the potential for enhanced thermal management,

electronic cooling technologies have changed very little in the past two or three

decades, continuing instead to implement a “remote cooling” paradigm with only

incremental improvements in performance.

5

1.3 Interlayer Micro-fluidic Cooling

Relying on the conventional air-cooled heat sink for the thermal management

of 3D-ICs could have catastrophic consequences. On one hand, due to the strong

thermal-performance interdependency, in order to limit on-chip temperatures, designers will resort to aggressive shutdown or slowdown resulting in significant underutilization of the available devices, hurting overall performance and leading 3D-ICs

to experience greater fractions of dark silicon than that experienced by 2D-ICs. On

the other hand, the heat removal challenge could limit the number of 3D layers or

physical design optimization space. Consequently, if the performance and energy

efficiency promised by 3D integration are to be realized, the thermal challenge needs

to be actively addressed.

Micro-fluidic cooling, which integrates micro-channel heat sinks into silicon

substrates of the chip and uses liquid flow to remove the heat from inside of the

chip, can overcome this limitation. It has been reported to support heat dissipation

higher than 700W/cm2 [84]. Despite the excellent cooling capability, an overhead

associated with micro-channel based heat removal technology is that the cooling

system needs to consume extra energy for pumping the coolant through the channels. This has motivated a body of work that attempts to improve the micro-channel

cooling effectiveness (thereby reducing the cooling energy consumption) by: a) controlling their dimensional parameters such as channel width, height and aspect ratio

[42][84], b) investigating more sophisticated micro-channel infrastructures such as

cross-linked micro-channels [32], micro-pin-fins [52][59], tree- or serpentine-shaped

6

micro-channels [68][23], and c) using hotspot optimized micro-channel structures

[12][76], etc. Recently, micro-channel cooling has also been adopted in dynamic

thermal management to control the runtime CPU performance and chip temperature by tuning the fluid flow rate through channels [19][18].

1.4 Interdependency between Electrical, Thermal, Reliability and

Cooling

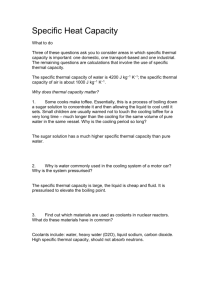

The electrical, thermal, reliability and cooling aspects of 3D-ICs are all interdependent. As the plot in Figure 1.1 shows, higher performance usually leads to

greater chip power consumption and generates heat. Increase in chip temperature

has a lot of detrimental effects.

1. It will result in higher circuit delay or delay uncertainties, which in turn limits

the performance improvement.

2. Due to the interdependency between temperature and leakage power, increase

in chip temperature will further increase the power consumption.

3. High chip temperature also exacerbate the electro-migration which will cause

reliability loss.

On the other hand, the heat level inside the chip also decides the micro-fluidic

cooling system configuration, which in turn changes the temperature/power distribution (due to thermal power interdependence), thereby changing the circuit delay

and chip lifetime. Furthermore, the existence of micro-fluidic cooling also causes

7

greater thermal gradients. Such thermal gradients and reduced chip temperature

will cause greater thermal stress, which on one hand, might result in mechanical

reliability issues such as crack formation, and on the other hand will change the

transistor delay.

Figure 1.1: Interdependency between Electrical, Thermal, Reliability and Cooling

1.5 Advantage of Electrical and Cooling System Co-Design

In the conventional IC design flow, the electrical parts of the chip is designed

first. The cooling system is then designed based on the current electrical system in

place. However, due to the aforementioned interdependency, such design methodology (that separates electrical and cooling system design) is inefficient. Co-design of

electrical and fluidic cooling system is necessary. It has the following advantages:

1. Higher cooling in timing critical areas results in better performing designs

since transistor delay is proportional to temperature.

2. Higher cooling in timing critical areas enables us to aggressively pursue high

power dissipating performance enhancements such as increasing supply volt-

8

age. This results in higher performance without impacting temperature since

the extra heat can be managed by micro-fluidics.

3. The design optimization could be more aggressive since temperature issue can

be addressed by aggressive cooling (placement, floorplanning etc).

4. Increasing the cooling levels in high leakage areas helps reduce the overall

power since leakage is a highly non-linear function of temperature. Reduction in leakage may be significant enough to make increase in pumping power

irrelevant.

5. Micro-fluidics may impact silicon thickness causing TSV performance degradation. By smart electrical design, this degradation could potentially be removed. For example, degradation in TSV performance could be overcome by

stronger drivers.

1.6 Thesis Outline

In this work, we investigate optimization of micro-fluidic cooling system that

can provide sufficient cooling to the 3D-IC with minimum overhead, while at the

same time, addressing the design constraints imposed by the 3D-IC structure. Three

micro-fluidic cooling configurations are proposed: hotspot-optimized non-uniform

micro-channel, bended micro-channel and hybrid cooling network.

In order to fully explore the interdependency among electrical, thermal, reliability and cooling aspects of 3D-ICs, we also investigate electrical and micro-fluidic

9

co-design methodologies. With the co-design, fundamental power-performance improvements can be achieved.

This dissertation is organized in five chapters. Following this introduction is

the background about 3D-IC and micro-fluidic cooling. In that chapter, we briefly

introduce the fundamentals of micro-fluidic cooling, as well as thermal and power

modeling of 3D-IC with micro-fluidic cooling. Chapter 3 discusses the design considerations of micro-fluidic cooling in 3D-ICs and presents three micro-channel heat sink

configurations that addresses these considerations. A micro-fluidic cooling based

dynamic thermal management (DTM) scheme is proposed. In Chapter 4, we investigate the electrical and cooling system co-design methodology. In that chapter,

we focus on two aspects of the co-design: a) TSV assignment and micro-channel

placement co-optimization, and b) gate sizing and micro-channel co-optimization.

Finally, we conclude in Chapter 5 with a summary of the main findings of this work,

and consider further prospects of this research field.

10

Chapter 2

Background

2.1 Basics of Three Dimensional Integrated Circuit

The 3D-IC contains two or more layers of active electronic components which

are stacked vertically. Figure 2.1 shows a three-tiered stacked 3D-IC. In the 3DIC, each active layer contains the functional units such as cores and caches, etc.

The metal layer contains wires that enable communication among different components. There is also a metal-oxide layer above each metal layer. Through-silicon-vias

(TSVs) are inserted in 3D-IC to deliver signal/power/ground among different tiers.

In 3D-IC, since several layers of electronic components that dissipates power

are stacked vertically, its power density is usually higher than 2D-ICs, leading to

potential thermal issues. Moreover, the thermal conductivity of oxide layer is low

and hence would reduce the heat transfer towards the ambient. This exacerbates the

thermal problems in 3D-ICs. Hence an important issue with 3D-IC is the removal

of high density heat resulting from several stacks of microprocessor chips. Although

current 3D-IC designs are limited to partitioning of memory and datapath across

layers, future 3D-IC designs are expected to have significantly complex architectures

and integration levels that would be associated with very high power dissipation and

heat density.

In order to alleviate the thermal issues, micro-channel based liquid cooling and

11

thermal TSVs have been adopted. As shown in Figure 2.1, micro-channel heat sinks

are embedded below the active layers. Liquid is pumped through each channel, and

takes away the heat generated in the active layers [39][43]. The heated coolant is

then cooled down in the heat exchanger, and recirculates into the fluid pump again

for the cooling in the next circulation. On the other hand, TSVs, which are usually

made of copper and have better thermal conductivity than silicon or metal-oxide,

can help improve conduction of heat between different layers. When the number of

signal TSVs is not enough, dummy thermal TSVs are inserted to further mitigate

the thermal issues.

Figure 2.1: Stacked 3D-IC with micro-channel cooling system

2.2 Fundamental Characteristics of Fluids in Micro-channels

2.2.1 Conservation Law of Fluid Dynamics

The characteristic of fluid inside the micro-channels is governed by conservation law of fluid. Considering the control volume of fluid U and its surface S

12

Figure 2.2: Control volume of fluid

(as shown in Figure 2.2). The fluid flow in the control volume is governed by the

following mass, momentum and energy conservation equations [87][62][85][37][78]:

∂ρ

+ ∇ · (ρ⃗v ) = 0

∂t

∂⃗v

Momentum conservation : ρ(

+ ⃗v · ∇⃗v ) = −∇p + µ∇2⃗v

∂t

dT

+ ∇ · (−kf ∇T ) + Cv⃗v · ∇T = Ṗ

Energy conservation : Cv

dt

Mass conservation :

(2.1)

Here ⃗v is the flow velocity vector, T is the fluid temperature, Ṗ is the volumetric

heat generation rate, and p is the pressure inside fluid. Also, ρ, µ, Cv and kf are

the density, viscosity, volumetric specific heat and thermal conductivity of the fluid,

respectively.

2.2.2 Dimensionless Numbers in Fluid Mechanics

The governing equations above are complex partial differential equations (PDE).

Researchers in fluid mechanics introduced a set of dimensionless numbers which

could help simplify the complex problem and also better understand the relative

importance of forces, energies, or time scales [87][55]. Some of these dimensionless

numbers are Reynolds number (Re), Prandtl number (Pr) and Nusselt number (Nu),

etc.

13

Reynolds number Re: The Reynolds number gives a measure of the ratio between

inertial forces to viscous forces, and is defined as:

Re =

ρvLc

µ

(2.2)

where v is the mean fluid velocity and Lc is the characteristic length. In straight

micro-channels, the characteristic length is usually given by the hydraulic diameter Dh .

When the cross section of the channel is circular, Dh is the diame-

ter of the cross section, while in rectangular channels, Dh is defined as Dh =

4 · cross sectional area/perimeter = 4∆x∆z/(2∆x + 2∆z), where ∆x and ∆z

are the width and height of the micro-channel. Usually, the Reynolds number is

used to distinguish between laminar and turbulent flow, which will be explained

later.

Prandtl number Pr: The Prandtl number is the ratio of momentum diffusivity

(kinematic viscosity) to thermal diffusivity.

Pr =

kinematic viscosity

µ/ρ

Cv µ

=

=

thermal diffusivity

kf /(ρCv )

kf

(2.3)

Nusselt number Nu: The Nusselt number is the ratio of convective to conductive

heat transfer across the boundary between the fluid and solid. The Nusselt number

is defined as:

Nu =

hLc

kf

(2.4)

where h, Lc and kf are the convective heat transfer coefficient, channel characteristic

14

length and fluid thermal conductivity. Usually, Nu is used to calculate the convective

heat transfer coefficient h. Many works have been done to characterize the Nusselt

number in micro-channels, and express it as a function of the Reynolds number and

Prandtl number [15][5][89][94].

2.2.3 Single and Two Phase Flow

The working fluid in the micro-channel can be either single phase or two phase.

The single phase flow consists of exclusively liquid coolant as the working fluid, while

two phase flow consists of both liquid and vapor.

When the power density is too high so that the liquid absorbs too much heat

and its temperature increases dramatically, part of the liquid will become vapor and

two phase flow is formed. The two phase flow exhibits different patterns. Figure

2.3(a)-(f) shows the two phase flow patterns in horizontal channels. When the flow

rate is low, the flow usually exhibits bubbly (Figure 2.3(a)) or plug pattern (Figure

2.3(b)), as the flow rate increases, the pattern becomes stratified (Figure 2.3(c)) and

wavy (Figure 2.3(d)), and finally slug (Figure 2.3(e)) and annular (Figure 2.3(f))

[82][51].

The evaporation process in a channel is as Figure 2.3(g) shows. As the single

phase liquid absorbs heat so that the temperature increases to the evaporation point,

small bubbles appear. When the fluid continues to absorb heat along the channel,

plug and slug flows appear. The flow becomes waved and annular in the end.

Figure 2.4 compares the cooling effectiveness of single and two phase flows.

15

(a) bubbly

(b) plug

(c) stratified

(d) wave

(e) slug

(f) annular

(g)

Figure 2.3: (a)-(f) Two phase flow patterns, (g) Evaporation process in a channel

It plots the solid temperature at the micro-channel outlet location Tw versus the

footprint power density Pa for both single and two phase flows at same pumping

power [6]. It shows that two phase flow achieves lower solid temperature than single

phase flow, which indicates that two phase flow has higher cooling effectiveness than

single phase flow.

16

60

Single phase

Two phase

Tw(oC)

50

40

30

20

0

100

200

300

400

Pa(W/cm2)

Figure 2.4: Comparison of single and two phase flow

2.2.4 Laminar and Turbulent Flow

The flow inside micro-channels can be laminar, turbulent, or transitional [55].

Figures 2.5(a), 2.5(b), 2.5(c) show these three types of patterns. Laminar flow

(Figure 2.5(a)) occurs when fluid flows in parallel layers, with no disruption between

the layers. That is, the pathlines of different particles are parallel. It generally

happens in small channels and low flow velocities. In turbulent flow (as shown

in Figure 2.5(b)), vortices and eddies appear, and make the flow unpredictable.

Turbulent flow generally happens at high flow rates and larger channels. Transitional

flow (Figure 2.5(c)) is a mixture of laminar and turbulent flow, with turbulence in

the center of the channel, and laminar flow near the edges.

Usually, Reynolds number is used to predict the type of flow (whether laminar,

turbulent or transitional) in straight channels. For example, as [55] shows:

When Re < 2100, it is laminar flow; when 2100 < Re < 4000, it is transitional

flow; when Re > 4000, it is turbulent flow.

When the channel involves more complex structure, the fluid exhibits more

17

(a) Laminar

(b) Turbulent

(c) Transitional

Figure 2.5: (a) Laminar flow pattern, (b) Turbulent flow pattern, (c) Transitional flow pattern

complicated behavior. Figure 2.6 shows an example of otherwise laminar flow in

straight channels in a micro-channel with bends. When fluid enters a channel, it

firstly subjects to a flow development process and after traveling some distance

downstream, it becomes fully developed laminar flow. Then, when the flow comes

across a bend, it becomes turbulent/developing around the corner and settles down

after traveling some distance downstream into laminar fully developed flow again

[68].

Figure 2.6: Fluid in micro-channel with bends

18

2.3 Thermal Modeling of 3D-IC with Micro-fluidic Cooling

2.3.1 Distributed RC Thermal Model

The chip thermal behavior can be modeled by a distributed RC network by

partitioning it into fine grids. In this network, each grid is represented by a node.

The voltage at each node represents the temperature at that grid. The current

source in each grid represents the power dissipated at that location, so the chip

power profile decides the current injected at each grid. Each resistance represents a

heat transfer path between grids, while capacitors indicate the ability to store heat

[77].

Figure 2.7 shows an example of the RC network for one 3D-IC layer. In this

network, Ri,j (i, j = 1...6) indicates the heat path (thermal resistance) between grids

i and j, Ci represents the thermal capacitance of grid i. According to the thermal

model, the thermal dynamics of each grid i is governed by the following equation:

∑ Ti − Tj

dTi

Pi

=−

+ ,

dt

Ri,j Ci

Ci

∀grids i

(2.5)

∀j∈N (i)

Here Ti is the temperature of grid i, and Pi is the power consumption at this grid,

N (i) represents the set of grids adjacent to grid i.

In some works, people are more interested in the steady state thermal behavior.

In this case, the thermal model can be simplified as a resistive network that represent

steady state chip thermal behavior. Hence the governing equation in Equation 2.5

can be simplified as a set of linear equations of temperature and power as Equation

19

Figure 2.7: RC network for 3D-IC thermal modeling

2.6 shows. Given a chip thermal resistive network and power profile, the temperature

profile can be estimated by solving the following system of linear equations.

G · T⃗ = P⃗

(2.6)

Here G is the thermal conductance matrix decided by the thermal resistance network, P⃗ = {Pi , ∀grid i}, T⃗ = {Ti , ∀grid i} represent the power and temperature

profiles.

2.3.2 Cooling Performance of Micro-channels

The heat removal through micro-channels comprises of an intricate combination of heat conduction, convection and coolant flow. Consider the micro-channel in

Figure 2.8, heat dissipated in surrounding regions (basically active layers) first conducts to the micro-channel sidewalls. The heat is then absorbed by the fluid through

convection. The heated fluid is then carried away by the moving flow. These three

aspects can be captured by expressing them as three types of thermal resistances:

Rcond for conduction, Rconv for convection and Rheat captures fluid flow (as shown

20

in Figure 2.8).

Figure 2.8: Micro-channel thermal model

Conductive resistance Rcond : It is decided by thermal characteristics of the silicon that conducts heat dissipated in surrounding region to micro-channel sidewalls.

It can be calculated using the model in [77].

Convective resistance Rconv : It results from the convection of fluid, which moves

the heat from micro-channel sidewalls to into the coolant fluid. The convective

resistance depends on the fluid property and area for heat transfer between the

micro-channel sidewalls and fluid. Assuming the micro-channel has been discretized

into grids along the fluid direction z. The size of each grid is ∆x×∆y ×∆z as Figure

2.8 shows. Let Rconv be the convective resistance between the micro-channel and

sidewalls in each grid. As shown in [84], Rconv = 1/hAh , where Ah is the surface

area for heat transfer in each grid. If we assume that heat can be transferred

from all four sidewalls, the surface area of each grid is Ah = 2∆z(∆x + ∆y). The

parameter h is the coefficient of convective heat transfer explained in Section 2.2.2.

Given the Nusselt number Nu and the micro-channel dimension, it is calculated by

h = Nu kf /Dh , kf is fluid thermal conductivity and Dh is the hydraulic diameter.

So the convective resistance could be expressed as:

21

Rconv =

1

Dh

=

hAh

2Nu kf ∆z(∆x + ∆y)

(2.7)

Convective resistance Rheat : The heat resistance basically represents the heat

flowing downstream caused by the moving fluid:

Rheat =

1

Cv ρf

(2.8)

Here f is the volumetric flow rate in each channel. It depends on the fluid velocity

v and micro-channel cross sectional area: f = velocity ∗ cross sectional area =

v∆x∆y. Cv is the fluid specific heat, and ρ is fluid density.

2.3.3 Overall Thermal Model of 3D-IC with Micro-channels

As indicated earlier, the thermal behavior of micro-channels can also be modeled by a thermal resistance network (Figure 2.8). The parameters of this resistive network could be computed using the equations described above or experiment

based approaches [54]. The 3D-IC resistive network and micro-channel network can

be combined to generate a unified model that captures the steady state thermal

behavior of 3D-ICs with liquid cooling (Figure 2.9). Other aspects of 3D-ICs such

as the thermal impact of TSVs and thermal wake effect [54] can also be incorporated

in this resistive network.

22

Figure 2.9: Thermal resistive network of one 3D-IC layer with micro-channels

2.3.4 Thermal Impact of TSVs

Besides of micro-fluidic cooling, some works have also proposed usage of dummy

thermal TSVs for 3D-IC temperature reduction [24][17][90]. Due to the existence of

oxide layer which separates different tiers of 3D-IC thermally, the heat cannot be

effectively dissipated between tiers. The dummy thermal TSVs are firstly proposed

by [14] as additional heat dissipation paths to alleviate the temperature issues on

chip. Now it is adopted in 3D-ICs [24][17][90]. Since the TSV fill materials such

as copper usually have much higher thermal conductivity than silicon and oxide,

thermal TSVs could enhance the vertical heat transfer between different 3D-IC tiers

and to the heat sinks by reducing the effective thermal resistances.

To quantify the thermal effect of TSV on 3D-IC, assuming there is a thermal

TSV inserted in a 3D-IC grid as Figure 2.10 shows. The dimension of the grid is

∆x × ∆y × ∆z, and its original vertical thermal conductivity is kyold . Assuming the

cross sectional area of thermal TSV is Atsv , the vertical thermal conductivity of this

grid after inserting the thermal TSV becomes:

23

Atsv

Atsv

+ kyold (1 −

)

∆x∆z

∆x∆z

Atsv

= kyold + (ktsv − kyold )

∆x∆z

kynew = ktsv

(2.9)

Since the thermal conductivity of TSV fill material ktsv is usually larger than the

original thermal conductivity kyold (which is generally the thermal conductivity of

silicon and metal-oxide), the thermal conductivity of this grid will increase after inserting the thermal TSV, which could result in better heat transfer between different

tiers, and thus more uniform thermal profile.

Figure 2.10: A 3D-IC grid with thermal TSV

2.4 Modeling of Power Consumption

The chip power consumption has two major components: dynamic power and

leakage power [86]. Dynamic power results from charging of transistor load capacitances when they are switched, while leakage power is the power consumed by

transistors when they are in idle state.

At the system level, there are generally three power states. A) Active mode,

where the system is performing some operation. In this mode, the chip dissipates

both dynamic power and leakage power. B) Standby mode, where the system is

idle but ready to execute an operation. In this mode, the circuit dissipates only

24

leakage power. C) Inactive mode, where the power supply to circuits are shut down

by power gating or other leakage reduction techniques. Very small amount of power

is dissipated in this mode.

In addition to the chip power consumption, the micro-fluidic heat sink also

consumes extra power for performing chip cooling. This power basically comes from

the pump to inject the coolant through micro-channels. This extra cooling power

consumption is called “pumping power”.

2.4.1 Dynamic Power Consumption

The dynamic power depends on the transistor load capacitances being charged,

the rate of switching, supply voltage, etc [86]. For each gate gi , its dynamic power

2

can be calculated by Pd,i = αi Cd,i Vdd

F , where Cd,i is the load capacitance of gate gi ,

αi is its average switching activity in each cycle and F is the clock frequency. The

output capacitance Cd,i is proportional to gate width si , hence the dynamic power

can also be represented as a function of gate size and clock frequency as Equation

2.10 shows. In the equation, βd,i depends on the switching activity αi and supply

voltage Vdd , etc.

2

Pd,i = αi Cd,i (s)Vdd

F = βd,i si F

25

(2.10)

2.4.2 Leakage Power Consumption

Current leaks through transistors even when they are turned off, resulting in

leakage power consumption. There are three main components of leakage power: reverse biased junction leakage, sub-threshold leakage and gate oxide tunneling leakage

[86].

The junction leakage and sub-threshold leakage increases with temperature

while the gate leakage is rather insensitive to temperature. [47] models the leakagetemperature dependency as:

−

Pl,i = βl,1 Ti2 e

− T1

As shown in [91], the variation of e

i

βl,2

Ti

+ βl,3

(2.11)

is very small in the normal range of chip

operating temperature. Hence, some works also approximate the leakage model as

a quadratic function of temperature as Equation 2.12 shows [91]. The quadratic

fitting parameters ε1,2,3 are obtained from the underlying model in [47]. We tested

the accuracy of this quadratic model. Figure 2.11 shows that the quadratic model

is very close to the exponential model given in [47].

Pl,i = ε1 Ti2 + ε2 Ti + ε3

(2.12)

The leakage power is also a linear function of gate width si [86]. Hence the overall

26

Transistor leakage power (W)

−8

x 10

6.5

exponential model

quadratic model

6

5.5

5

4.5

4

3.5

0

50

100

150

Temperature (oC)

Figure 2.11: Exponential leakage model versus quadratic leakage model

leakage power can be modeled as (here φ is a constant):

Pl,i = φ · si · (βl,1 Ti2 e

−

βl,2

Ti

+ βl,3 ) ≈ φ · si · (ε1 Ti2 + ε2 Ti + ε3 )

(2.13)

From the power models, large gate size will result in higher dynamic and leakage

power, which leads to temperature increase. Temperature increase in turn will lead

to further increase in leakage power.

2.4.3 Micro-channel Cooling Power

2.4.3.1 Straight Micro-channels

The power used by micro-channels for performing chip cooling comes from the

work done by the fluid pump to push the coolant fluid into micro-channels. It is a

strong function of the level of heat removal desired. Basically, to maintain acceptable

thermal levels, increase of chip power dissipation would result in increased pumping

power Ppump , which is decided by the pressure drop and coolant fluid flow rate.

27

N

∑

Ppump =

fn ∆pn

(2.14)

n=1

Assuming there are N micro-channels, ∆pn and fn are the pressure drop and fluid

flow rate of the n-th micro-channel.

Here we assume the flow is fully developed laminar flow. The pressure drop in

a micro-channel is decided by:

∆p =

2γµLv

Dh2

(2.15)

where L is channel length, Dh is hydraulic diameter, v is fluid velocity, µ is the

∆y

viscosity of fluid and γ is a function of micro-channel aspect ratio ( ∆x

) [42][39].

In this work, we assume that all straight micro-channels have the same width

and height. Usually fluid pumps are designed to work such that all the microchannels experience the same pressure drop ∆p. For a given pressure drop that

the pump delivers across all channels, fluid velocity v could be estimated using

Equation 2.15. So the fluid flow rate f = v∆x∆y is also a function of pressure drop

∆p, and could be estimated. Since the pressure drop is the same across all channels,

so are the velocity and fluid flow rate since we assume all channels have the same

dimension. Given this, the pumping power can be rewritten as:

Ppump = N f ∆p =

28

N ∆x∆yDh2 ∆p2

2γµL

(2.16)

2.4.3.2 Micro-channels with Bends

Consider the micro-channel structure shown in Figure 2.6. The existence of a

bend causes a change in the flow properties which impact the cooling effectiveness

and pressure drop. An otherwise fully developed laminar flow in the straight part of

the channel, when comes across a 90◦ bend becomes turbulent/developing around

the corner and settles down after traveling some distance downstream into laminar

fully developed again (see Figure 2.6). So a channel with bends has three distinct

regions, 1) fully developed laminar flow region, 2) the bend corner, and 3) the

developing/turbulent region after the bend [33][68]. The length of flow developing

region is [69]:

Ld = (0.06 + 0.07

∆y

∆y 2

− 0.04 2 )ReDh

∆x

∆x

(2.17)

where Re is the Raynolds number, and ∆x, ∆y and Dh are the micro-channel

width, height and hydraulic diameter.

The rectangular bend impacts the pressure drop. Due to the presence of bends,

the pressure drop in the channel is greater than an equivalent straight channel with

exactly the same dimensions. The total pressure drop in a channel with bends is

the sum of the pressure drop in the three regions described above (which finally

depend on how many bends the channel has). Assume L is the total channel length,

and m is the bend count. Therefore m · Ld is the total length that has developing/turbulent flow and m · ∆x is the total length attributed to corners (see Figure

2.6). Hence the effective channel length attributed to fully developed laminar flow

is L − m · Ld − m · ∆x. The pressure drop in the channel is the sum of the pressure

29

drop in each of these regions.

Pressure drop in fully developed laminar region: The total pressure drop in

fully developed laminar region is [42]:

∆pf =

2γµ(L − m · Ld − m · ∆x)v

2γµLf v

=

2

Dh

Dh2

(2.18)

Here Lf = L − m · Ld − m · ∆x is the total length of the fully developed laminar

region which is explained above, the other parameters are the same as in Equation

2.15.

Pressure drop in flow developing region: The pressure drop in each flow

developing region is: δpd =

3.44

√

2µv

2

Dh

∫ Ld

0

ψ(z)dz [56]. Here ψ(z) is given by ψ(z) =

(ReDh )/z, where z is the distance from the entrance of developing region

in the flow direction. Assuming there are a total of m corners in a given microchannel, so there are m developing regions with the same length Ld in this channel.

By putting the expression of ψ(z) and Ld into the equation of δpd and solving

the integration, we can get the total pressure drop of the developing region in this

micro-channel:

∆pd = m · δpd = mKd ρv 2

2

1

(2.19)

∆y

∆y 2

is a constant associated with the

where Kd = 13.76(0.06 + 0.07 ∆x

− 0.04 ∆x

2)

aspect ratio

∆y

.

∆x

Please refer to [33][56] for details.

30

Pressure drop in corner region: The total pressure drop at all the 90◦ bends in

a micro-channel is decided by:

ρ

∆p90◦ = m · δp90◦ = m K90 v 2

2

(2.20)

where m is the number of corners in the channel, δp90◦ is the pressure drop at each

bend corner and K90 is the pressure loss coefficient for 90◦ bend whose value can be

found in [33].

Total pumping power: The total pressure drop in a micro-channel with bends is

the sum of the pressure drop in the three regions discussed above:

∆p = ∆pd + ∆pf + ∆p90◦ =

2γµLf

K90

v + m(Kd +

)ρv 2

2

Dh

2

(2.21)

From Equations 2.21, the total pressure drop of a micro-channel is a quadratic

function of the fluid velocity v. For a given pressure difference applied on a microchannel, we can calculate the associated fluid velocity by solving Equation 2.21.

With the fluid velocity, we can then estimate the fluid flow rate f , and thus estimate

the thermal resistance and pumping power for this channel. Hence the pumping

power as well as cooling effectiveness of micro-channels with bends is a function of

1) number of bends, 2) location of channels, and 3) pressure drop across the channel.

Comparing Equations 2.15 and 2.21, due to the presence of bends, if the same

31

pressure drop is applied on a straight and a bended micro-channel of the same

length, the bended channel will have lower fluid velocity, which leads to a lower

cooling capability. Therefore, to provide the same amount of cooling, we will need

to increase the overall pressure drop that the pump delivers, which results in increase

of pumping power. But bends allow for better coverage in the presence of TSVs.

32

Chapter 3

Design of Micro-fluidic Cooling Configurations for 3D-ICs

3.1 Motivation of Micro-Fluidic Cooling

The coming years will witness a significant increase in CPU power dissipation

due to advanced multi-core architectures and 3D integration technologies. The

thermal problem in 3D-IC is even more severe compared with 2D circuits, because

the power density is usually higher due to the stacked architecture. Moreover,

the thermal conductivity of oxide layer is low and hence would reduce the heat

conduction towards the ambient. The conventional air cooling has been proved

to be insufficient for future high performance 3D-ICs even with sophisticated DTM

schemes [8]. As a result, more effective active cooling schemes are being investigated

for high performance 3D-ICs [39][43]. Micro-channel cooling, which integrates microchannel heat sinks into each tier of the 3D-IC and uses liquid flow to remove heat

from within the 3D chip, is an effective active cooling scheme for 3D-IC. It has

been reported to support heat dissipation higher than 700W/cm2 with single phase

flow[84]. When the working fluid is two phase flow, the heat removal rate is even

higher.

33

Figure 3.1: Micro-channel and TSV configuration

3.2 Micro-channel Design Considerations/Constraints

As shown in Figure 2.1, each tier of 3D-IC contains an active silicon layer

and silicon substrate. The micro-channels are placed horizontally in the silicon

substrate. TSVs such as power/ground TSV, signal TSV, etc, are incorporated

for communications between layers and delivery of power and ground. Figure 3.1

shows a possible configuration of micro-channels and TSVs in the silicon substrate

of 3D-IC [40][45]. In each 3D-IC tier, micro-channels are etched in the inter-layer

region (silicon substrate). Fluidic channels (fluidic TSVs) go through all the tiers

and delivers coolant to micro-channels. TSVs also go through the silicon substrate

vertically to deliver signal, power and ground.

Though the micro-channel heat sink is capable of achieving good cooling performance, many problems need to be addressed when designing the micro-channel

infrastructure for cooling 3D-IC so as to ensure the reliability of the chip and also

improve the effectiveness of the micro-channel [72].

34

10

Ppump(W)

8

6

4

2

0

250

300

350

400

450

500

550

Total 3D−IC chip power (W)

Figure 3.2: Pumping power versus chip power consumption

3.2.1 Cooling Power Consumption

The micro-fluidic cooling is active by nature. That is, the fluid pump consumes extra energy for pushing the coolant through the micro-channels (we call this

pumping power consumption). The pumping power can be quite significant. Figure

3.2 shows the pumping power required to maintain the 3D chip below temperature

constraints (85℃) for different chip power profiles using the conventional approach

of spreading straight micro-channels all over each tier. For each power profile, we

find the minimum pressure drop required to maintain the chip temperature within

constraints and then estimate the pumping power under this pressure drop using

Equation 2.16. As we can see, to maintain the chip temperature within acceptable levels, pumping power increases very fast as the total chip power increases.

Therefore controlling the micro-channel pumping power is very important.

3.2.2 Non-uniform Power Profile

The underlying heat dissipated in each active silicon layer exhibits great nonuniformity [39][60]. Such non-uniformity in power profile results in hotspots in

35

thermal profiles. Therefore, when designing micro-channel heat sink infrastructure,

one should account for this non-uniformity in thermal and power profiles. Simply

minimizing the total equivalent thermal resistance of the micro-channels while failing

to consider the non-uniformity of the power profile will lead to suboptimal design.

For example, conventional approaches for micro-channel designs spread the entire

surface to be cooled with channels, and find the width and height of micro-channels

that minimize the overall thermal resistance [84][42]. This approach, though helps

reducing the peak temperature around the hotspot region, over cools areas that are

already sufficiently cool. This is wasteful from the point of view of pumping power.

3.2.3 TSV Constraint

3D-ICs impose significant constraints on how and where the micro-channels

could be located due to the presence of TSVs, which allow different layers to communicate. As illustrated in Figure 3.1, micro-channels are allocated in the interlayer

bulk silicon regions. TSVs also exist in this region, causing a resource conflict. A

3D-IC usually contains thousands of TSVs which are incorporated with clustered

or distributed topologies [26][57]. These TSVs form obstacles to the micro-channels

since the micro-channels cannot be placed at the locations of TSVs. Therefore the

presence of TSVs limits the available spaces for micro-channels, and designing the

micro-channel infrastructure should take this fact into consideration.

36

3.2.4 Thermal stress

The TSV fill materials are usually different from silicon. For example, copper

has low resistivity and is therefore widely used as the material for TSV fill. Because

the annealing temperature is usually much higher than the operating temperature,

thermal stress will appear in silicon substrate and TSV after cooling down to room

temperature due to the thermal expansion mismatch between copper and silicon

[92][7]. This thermal stress might result in reliability problems such as cracking.

Moreover, as shown in [92][28], thermal stress also influences electron/hole

mobilities significantly, hence changing the gate delay. Therefore, if the gates on

critical paths are allocated near TSVs (basically regions with high thermal stress),

timing violation might occur.

The existence of micro-channels which influences the temperature around

TSVs will influence the thermal stress, thereby changing the mechanical reliability analysis and timing analysis in the 3D-IC with TSVs. For example, Figure 3.3

shows the thermal stress inside and surrounding a TSV at different thermal conditions. Figure 3.3(a) depicts the thermal stress when chip temperature is 100℃ and

annealing temperature (which is basically the stress free reference temperature) is

250℃. The figure shows that large thermal stress (up to 490MPa) appears surrounding the TSV. Figure 3.3(b) depicts the thermal stress when the chip temperature

is 50℃. In this case (where chip temperature is 50℃), the overall thermal stress is

increased (compared with the previous case where chip temperature is 100℃), and

the maximum thermal stress reaches up to 670MPa. Such phenomenon indicates

37

that reduction in chip temperature results in an increase in thermal stress. Hence

the existence of micro-channels, which generally reduces chip temperature, may increase the TSV-induced thermal stress. Such phenomenon should be considered

when designing the micro-channel infrastructure.

(a)

(b)

Figure 3.3: Thermal stress inside and surrounding TSV (a) when chip temperature is 100℃, (b)

when chip temperature is 50℃(assuming stress free temperature is 250℃)

Moreover, if micro-channels are placed too close to the TSVs, the silicon walls

between the TSVs and micro-channels will be more likely to crack because the walls

are thin. These facts further limits the locations of micro-channels.

In this chapter, we propose three micro-channel structures (cooling configura38

tions) to improve the cooling effectiveness while still satisfying the design constraints

imposed on micro-channels. These three structures are: non-uniform (hotspot optimized) micro-channels [76], bended (TSV-constrained) micro-channels [73] and

hybrid cooling network [75]. We also investigate a micro-channel based dynamic

thermal management scheme that controls the runtime chip temperature by tuning

the pressure drop (fluid flow rate) through micro-channels [71].

3.3 Hotspot Optimized Non-Uniform Micro-channel

The first configuration is hotspot-optimized non-uniformly distributed microchannels [76]. In this work, we start from the regular straight micro-channels. According to the micro-channel thermal model in Section 2.3.2, the cooling effectiveness

of micro-channels depends on the dimension and distribution of micro-channels, as

well as the fluid flow rate through micro-channels. The pumping power required by

micro-channels also depends on these parameters as Equation 2.16 shows. Here we

assume the micro-channel width and height are fixed. The optimal micro-channel

width and height were investigated in [84][42], etc. In this case, designing the

optimal micro-channel structure is basically deciding the count and distribution of

micro-channels. For a given pressure drop, increase in the number of micro-channels

helps increasing the coverage of cooling system thereby improving the heat removal

rate. But this will also lead to linear increase in total pumping power.

39

3.3.1 Problem Formulation

Given a 3D-IC design, its power distribution is a function of the architecture and application. Assuming the power profile is given (this assumption will be

generalized later), and we know a set of locations as potential target locations for

micro-channels (see Figure 3.4) (all locations containing TSVs have been removed

from this set for the sake of illustration). We want to find the number and locations

of channels such that the temperature all over the chip is within acceptable limits

while minimizing the number of channels (assuming pressure drop ∆p is fixed). The

problem is formulated as follows:

unknowns :

B

min

N = sum(B)

s.t.

T⃗ (B) ≤ Tmax

(3.1)

Here, B = {B1 , B2 , ..., BN } is a vector representing the locations of all microchannels. Assuming we know the set of potential micro-channel locations, each

element Bn (n = 1...N ) in B corresponds to one of these locations and it’s value is

assigned as:

1, micro-channel exists in this location

Bn =

(3.2)

0, otherwise

N is the total number of micro-channels placed. When pressure drop ∆p is given,

pumping power only depends on the total number of micro-channels N , so the

objective in Equation 3.1 basically minimizes the pumping power. For a given

40

allocation of micro-channels, the thermal resistive network can be used to estimate

temperature profile by dividing the 3D-IC into grids (using the approach illustrated

in Section 2.3.3). Finding the optimal locations of micro-channels is a complex

discrete problem. Now we describe an iterative heuristic that finds a good solution.

3.3.2 Heuristic for Micro-channel Placement

Algorithm 1 gives the basic framework of our heuristic. The heuristic is based

on iterative improvement. We start by finding a set of potential locations for microchannels as Figure 3.4 shows. Note that all the locations containing TSVs and

other structures are removed from this set for the sake of illustration. In reality the

potential location would be limited by TSV locations, etc. The detailed approach for

finding the potential micro-channel locations is given in Section 3.3.3. In the initial

micro-channel design, micro-channels are placed at all the potential locations. We

assign each micro-channel a cost which represents the impact of removing the microchannel on thermal profile. Given the initial design and micro-channel cost, the

algorithm iteratively removes micro-channels until further removal results in thermal

violation. In each iteration, the micro-channel with the smallest cost is removed.

After each micro-channel removal, the costs of the remaining micro-channels need

to be updated. This is because the impact of removing a micro-channel on the

thermal profile is a function of both the power profile and also which micro-channels

have been removed so far. A micro-channel that had little impact on the thermal

profile if many micro-channels were present in its neighborhood might have a much

41

(a)

(b)

Figure 3.4: Potential locations of micro-channels: (a) uniform spreading of micro-channels, (b)

workload-balanced micro-channel spreading

Algorithm 1 Heuristic for micro-channel placement

Starting from micro-channels placed at all potential locations:

1. Initialize the cost (defined below) for each micro-channel;

2. Set viscosity µ = µ(Tin ), where Tin is coolant inlet temperature;

3. Repeat:

4. Remove micro-channel with the lowest cost;

5. Generate the new resistive thermal model;

6. Estimate the temperature profile T⃗

7.

If T⃗ ≤ Tmax , update cost and viscosity, and go to step 2;

8.

Else stop.

higher impact when its neighboring micro-channels have been removed. Since the

fluid viscosity µ is a function of fluid temperature, we also update the value of fluid

viscosity after each iteration. To estimate the new viscosity, we calculate the average

fluid temperature among all channels and lookup the associated viscosity from the

table in [34].

The complexity in this optimization problem comes from the fact that as we

change the location of channels, the underlying thermal resistive network changes.

42

In order to estimate the thermal impact, we need to solve Equation 2.6 every time

we have a new resistive network, which, even though exhibits linear complexity for

estimation of the thermal profile, can have high complexity due to the granularity

of the grid. The success (both performance and runtime) of this algorithm critically

depends on how potential micro-channel locations are distributed (which basically

decides the initial micro-channel distribution) and how micro-channel cost is assigned and updated. In the next three subsections, we will discuss these aspects

and investigate ways to improve the efficiency of the algorithm (basically reducing

the required number of iterations in the algorithm).

3.3.3 Workload-balanced Initial Micro-channel Distribution

The heuristic of micro-channel placement starts with an initial distribution

where micro-channels are placed at all the potential locations and iteratively removes

micro-channels. The complexity of the algorithm mostly comes from the thermal

estimation in each iteration. Hence we should reduce the number of iterations