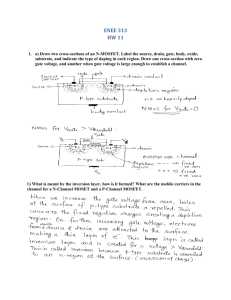

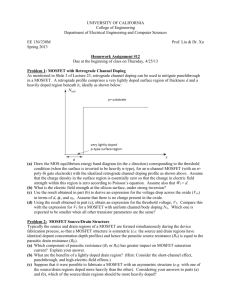

Introduction to MOSFETs

advertisement