Field-Effect Transistor - Philadelphia University

advertisement

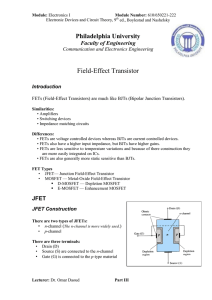

Module: Electronics I Module Number: 610/650221-222 Electronic Devices and Circuit Theory, 9th ed., Boylestad and Nashelsky Philadelphia University Faculty of Engineering Communication and Electronics Engineering Field-Effect Transistor Introduction FETs (Field-Effect Transistors) are much like BJTs (Bipolar Junction Transistors). Similarities: • Amplifiers • Switching devices • Impedance matching circuits Differences: FETs are voltage controlled devices whereas BJTs are current controlled devices. FETs also have higher input impedance, but BJTs have higher gains. FETs are less sensitive to temperature variations and because of there construction they are more easily integrated on ICs. FETs are also generally more static sensitive than BJTs. In the BJT-the prefix bi-revealing that the conduction level is a function of two charge carriers, electrons and holes. The FET is unipolar device depending on either electrons or holes conduction. FET Types • JFET–– Junction Field-Effect Transistor • MOSFET –– Metal-Oxide Field-Effect Transistor D-MOSFET –– Depletion MOSFET E-MOSFET –– Enhancement MOSFET JFET JFET Construction There are two types of JFETs: • n-channel (The n-channel is more widely used.) • p-channel There are three terminals: • Drain (D) • Source (S) are connected to the n-channel Lecturer: Dr. Omar Daoud ١ Module: Electronics I Module Number: 610/650221-222 Electronic Devices and Circuit Theory, 9th ed., Boylestad and Nashelsky • Gate (G) is connected to the p-type material Basic Operation of a JFET JFET operation can be compared to a water spigot. The source of water pressure is the accumulation of electrons at the negative pole of the drain-source voltage. The drain of water is the electron deficiency (or holes) at the positive pole of the applied voltage. The control (gate) of flow of water is the gate voltage that controls the width of the n-channel and, therefore, the flow of charges from source to drain. JFET Operating Characteristics Three things happen when VGS = 0 and VDS is increased from 0 to a more positive voltage • The depletion region between p-gate and nchannel increases as electrons from nchannel combine with holes from p-gate. • Increasing the depletion region, decreases the size of the n-channel which increases the resistance of the n-channel. • Even though the n-channel resistance is increasing, the current (ID) from source to drain through the n-channel is increasing. This is because VDS is increasing. If VGS = 0 and VDS is further increased to a more positive voltage, then the depletion zone gets so large that it pinches off the n-channel. This suggests that the current in the n-channel (ID) would drop to 0A, but it does just the opposite–as VDS increases, so does ID. Lecturer: Dr. Omar Daoud ٢ Module: Electronics I Module Number: 610/650221-222 Electronic Devices and Circuit Theory, 9th ed., Boylestad and Nashelsky At the pinch-off point: • • • Any further increase in VGS does not produce any increase in ID. VGS at pinchoff is denoted as Vp. ID is at saturation or maximum. It is referred to as IDSS. The ohmic value of the channel is maximum. As VGS becomes more negative, the depletion region increases. • • • The JFET experiences pinch-off at a lower voltage (Vp). ID decreases (ID < IDSS) even though VDS is increased. Eventually ID reaches 0A. VGS at this point is called Vp or VGS(off).. Also note that at high levels of VDS the JFET reaches a breakdown situation. ID increases uncontrollably if VDS > VDSmax. The region to the left of the pinch-off point is called the ohmic region. The JFET can be used as a variable resistor, where VGS controls the drain-source resistance (rd). As VGS becomes more negative, the resistance (rd) increases. rd ro VGS 1 V P 2 Where ro is the resistance with VGS=0 and rd the resistance at a particular level of VGS. Lecturer: Dr. Omar Daoud ٣ Module: Electronics I Module Number: 610/650221-222 Electronic Devices and Circuit Theory, 9th ed., Boylestad and Nashelsky The transfer characteristic of input-to-output is not as straightforward in a JFET as it is in a BJT. In a BJT, indicates the relationship between IB (input) and IC (output). In a JFET, the relationship of VGS (input) and ID (output) is a little more complicated: ID I VGS DSS 1 V P 2 Summary: Lecturer: Dr. Omar Daoud ٤ Module: Electronics I Module Number: 610/650221-222 Electronic Devices and Circuit Theory, 9th ed., Boylestad and Nashelsky JFET Transfer (Characteristics) Curve This graph shows the value of ID for a given value of VGS. Using IDSS and Vp (VGS(off)) values found in a specification sheet, the transfer curve can be plotted according to these three steps: Step 1 Solving for VGS = 0V, 2 V I D I DSS 1 GS I D I DSS VP Step 2 Solving for VGS = Vp (VGS(off)) ID = 0A Step 3 Solving for VGS = 0V to Vp Fig. 6.18 Transfer curve for Example 6.1. Lecturer: Dr. Omar Daoud Fig. 7.17 Example 7.3. ٥ Module: Electronics I Module Number: 610/650221-222 Electronic Devices and Circuit Theory, 9th ed., Boylestad and Nashelsky Exmple 6.1: MOSFET MOSFETs have characteristics similar to JFETs and additional characteristics that make then very useful. There are two types of MOSFETs: • Depletion-Type • Enhancement-Type The drain (D) and source (S) connect to the to ndoped regions. These n-doped regions are connected via an n-channel. This n-channel is connected to the gate (G) via a thin insulating layer of SiO2. The n-doped material lies on a p-doped substrate that may have an additional terminal connection called substrate (SS). A depletion-type MOSFET can operate in two modes: • Depletion mode • Enhancement mode Depletion Mode: The characteristics are similar to a JFET. • When VGS = 0V, ID = IDSS • When VGS < 0V, ID < IDSS Lecturer: Dr. Omar Daoud Fig. 5.25 Drain and transfer characteristics for an n-channel depletion-type MOSFET. ٦ Module: Electronics I Module Number: 610/650221-222 Electronic Devices and Circuit Theory, 9th ed., Boylestad and Nashelsky • The formula used to plot the transfer curve still applies: V I D I DSS 1 GS VP 2 Fig. 5.24 n-Channel depletion-type MOSFET with VGS = 0 V and applied voltage VDD. Enhancement Mode: • VGS > 0V ID increases above IDSS • • The formula used to plot the transfer curve still applies: V I D I DSS 1 GS VP 2 Enhancement-Type MOSFET Construction • The drain (D) and source (S) connect to the ndoped regions. These n-doped regions are connected via an n-channel • The gate (G) connects to the p-doped substrate via a thin insulating layer of SiO2 Lecturer: Dr. Omar Daoud ٧ Module: Electronics I Module Number: 610/650221-222 Electronic Devices and Circuit Theory, 9th ed., Boylestad and Nashelsky • There is no channel • The n-doped material lies on a p-doped substrate that may have an additional terminal connection called the substrate (SS) The enhancement-type MOSFET only operates in the enhancement mode. • • • VGS is always positive As VGS increases, ID increases As VGS is kept constant and VDS is increased, then ID saturates (IDSS) and the saturation level, VDSsat is reached Lecturer: Dr. Omar Daoud ٨ Module: Electronics I Module Number: 610/650221-222 Electronic Devices and Circuit Theory, 9th ed., Boylestad and Nashelsky Field-Effect Transistor Amplifiers Transconductance The relationship of VGS(input) to ID(output) is called transconductance. Transconductance is denoted gm and given by: gm 2I ΔI D DSS ΔV GS VP VGS 1 VP Where VGS =0V 2I g m0 DSS VP Where 1 VGS VP V g m g m0 1 GS VP V ID ID g m g m0 1 GS g m0 I DSS VP I DSS The prefix trans- in the terminology applied to gm reveals that it establishes a relationship between an output and input quantity. The root word conductance was chosen because it is determined by a voltage-to-current ratio similar to the ratio that defines the conductance of a resistor. FET Impedance Z o rd 1 y os where: VDS rd V constant I D GS yos= admittance equivalent circuit parameter listed on FET specification sheets. FET AC Equivalent Circuit FET Biasing Lecturer: Dr. Omar Daoud ٩ Module: Electronics I Module Number: 610/650221-222 Electronic Devices and Circuit Theory, 9th ed., Boylestad and Nashelsky JFET Common-Source (CS) Fixed-Bias Configuration The input is on the gate and the output is on the drain. There is a 180 phase shift between input and output Zi R G Z o R D || rd Zo R D rd 10R D Vo g m (rd || R D ) Vi V A v o g m R D rd 10R D Vi Av Lecturer: Dr. Omar Daoud ١٠ Module: Electronics I Module Number: 610/650221-222 Electronic Devices and Circuit Theory, 9th ed., Boylestad and Nashelsky Example 7.1: Lecturer: Dr. Omar Daoud ١١ Module: Electronics I Module Number: 610/650221-222 Electronic Devices and Circuit Theory, 9th ed., Boylestad and Nashelsky Solution: Lecturer: Dr. Omar Daoud ١٢ Module: Electronics I Module Number: 610/650221-222 Electronic Devices and Circuit Theory, 9th ed., Boylestad and Nashelsky Cont. Example 7.1: Solution: JFET Common-Source (CS) Self-Bias Configuration It eliminates the need for two dc supplies. The controlling VGS is now determined by the voltage across a resistor Rs. Lecturer: Dr. Omar Daoud ١٣ Module: Electronics I Module Number: 610/650221-222 Electronic Devices and Circuit Theory, 9th ed., Boylestad and Nashelsky Bypassed RS: Unbypassed RS: Fig. 8.18 Self-bias JFET configuration including the effects of RS with rd = ∞ Ω. Lecturer: Dr. Omar Daoud ١٤ Module: Electronics I Module Number: 610/650221-222 Electronic Devices and Circuit Theory, 9th ed., Boylestad and Nashelsky Example 7.2: Lecturer: Dr. Omar Daoud ١٥ Module: Electronics I Module Number: 610/650221-222 Electronic Devices and Circuit Theory, 9th ed., Boylestad and Nashelsky Solution: Cont. Example 7.2.: Lecturer: Dr. Omar Daoud ١٦ Module: Electronics I Module Number: 610/650221-222 Electronic Devices and Circuit Theory, 9th ed., Boylestad and Nashelsky Solution: Common Source Voltage Divider Bias Configuration Lecturer: Dr. Omar Daoud ١٧ Module: Electronics I Module Number: 610/650221-222 Electronic Devices and Circuit Theory, 9th ed., Boylestad and Nashelsky Lecturer: Dr. Omar Daoud ١٨ Module: Electronics I Module Number: 610/650221-222 Electronic Devices and Circuit Theory, 9th ed., Boylestad and Nashelsky Example 7.5: Solution: Fig. 7.25 Fig. 7.26 Lecturer: Dr. Omar Daoud Example 7.5. Determining the Q-point for the network of Fig. 7.25. ١٩ Module: Electronics I Module Number: 610/650221-222 Electronic Devices and Circuit Theory, 9th ed., Boylestad and Nashelsky Example 7.6: Lecturer: Dr. Omar Daoud ٢٠ Module: Electronics I Module Number: 610/650221-222 Electronic Devices and Circuit Theory, 9th ed., Boylestad and Nashelsky Solution: ` Lecturer: Dr. Omar Daoud ٢١ Module: Electronics I Module Number: 610/650221-222 Electronic Devices and Circuit Theory, 9th ed., Boylestad and Nashelsky Source Follower (Common-Drain) Configuration In a common-drain amplifier configuration, the input is on the gate, but the output is from the source. There is no phase shift between input and output. Zi R G Z o rd || R S || Z o R S || 1 gm 1 gm rd 10R S Vo g m (rd || R S ) Vi 1 g m (rd || R S ) V gmRS Av o r 10 Vi 1 g m R S d Av Fig. 8.29 Lecturer: Dr. Omar Daoud Network to be analyzed in Example 8.9. ٢٢ Module: Electronics I Module Number: 610/650221-222 Electronic Devices and Circuit Theory, 9th ed., Boylestad and Nashelsky Lecturer: Dr. Omar Daoud ٢٣ Module: Electronics I Module Number: 610/650221-222 Electronic Devices and Circuit Theory, 9th ed., Boylestad and Nashelsky Example 8.9: Solution: Lecturer: Dr. Omar Daoud ٢٤ Module: Electronics I Module Number: 610/650221-222 Electronic Devices and Circuit Theory, 9th ed., Boylestad and Nashelsky JFET Common-Gate Configuration The input is on the source and the output is on the drain. There is no phase shift between input and output. r RD Z i R S || d 1 g m rd 1 Z i R S || r 10R gm d D Z o R D || rd Zo R D rd 10 RD g m R D rd Vo Av Vi RD 1 rd Av gmR D rd 10R D Lecturer: Dr. Omar Daoud ٢٥ Module: Electronics I Module Number: 610/650221-222 Electronic Devices and Circuit Theory, 9th ed., Boylestad and Nashelsky Example 8.10: Solution: Lecturer: Dr. Omar Daoud ٢٦ Module: Electronics I Module Number: 610/650221-222 Electronic Devices and Circuit Theory, 9th ed., Boylestad and Nashelsky Fig. 8.33 Network for Example 8.10. Lecturer: Dr. Omar Daoud ٢٧ Module: Electronics I Module Number: 610/650221-222 Electronic Devices and Circuit Theory, 9th ed., Boylestad and Nashelsky Design Example 1: Lecturer: Dr. Omar Daoud ٢٨ Module: Electronics I Module Number: 610/650221-222 Electronic Devices and Circuit Theory, 9th ed., Boylestad and Nashelsky Design Example 2: Lecturer: Dr. Omar Daoud ٢٩ Module: Electronics I Module Number: 610/650221-222 Electronic Devices and Circuit Theory, 9th ed., Boylestad and Nashelsky Design Example 3: Lecturer: Dr. Omar Daoud ٣٠