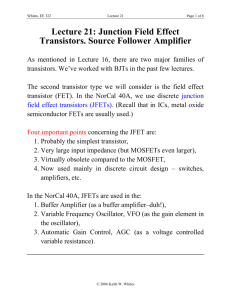

1.5 - JUNCTION FIELD-EFFECT TRANSISTORS (JFETS)

advertisement

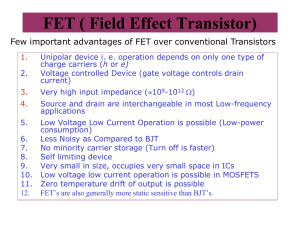

JFETs (5/11/00) Page 1 1.5 - JUNCTION FIELD-EFFECT TRANSISTORS (JFETS) INTRODUCTION Objective The objective of this presentation is: 1.) Characterize the behavior of the junction field-effect transistor (JFET) 2.) Develop the large and small signal models of the JFET Outline • Operation of the JFET • Large signal model of the JFET • Small signal model of the JFET ECE 4430 - Analog Integrated Circuits and Systems P.E. Allen, 2000 JFETs (5/11/00) Page 2 OPERATION OF THE JFET General Introduction The junction field-effect transistor uses a reverse biased pn junction to vary the cross-section of a channel through which current flows. The control (input) voltage is the reverse bias voltage which determines the amount of current flowing from the drain to source. Schematic: D D iD + iG G + vGS vDS - - S p-channel ECE 4430 - Analog Integrated Circuits and Systems iD + iG G + vGS vDS - - S n-channel Fig.1.5-1 P.E. Allen, 2000 JFETs (5/11/00) Page 3 Physical Aspects of the JFET using BJT Technology p-channel JFET: ,,,,,, ,,, ,,,,,, ,,, ,,,,,, BE Depletion Source Region Drain Gate p+ n+ p- isolation n+ emitter BC Depletion Region p+ p- isolation p base n collector n+ buried layer p- substrate p+ p p- ni n- n n+ Metal Fig.1.5-2 Comments: • Both the base-emitter and base-collector junctions are reverse biased. • The channel is pinched off when the BE and BC depletion regions touch. ECE 4430 - Analog Integrated Circuits and Systems P.E. Allen, 2000 JFETs (5/11/00) Page 4 LARGE SIGNAL JFET MODEL Idealized p -channel JFET Structure ,,,,,, ,,,,,, ,,,,,, v(L)=V'DS n+ emitter X(y) v(y) 2a iD p base b(y) X(y) vGS VDS n collector L y Fig. 1.5-3 0 L At a distance, y, down the channel from the source end, we can write: The reverse bias voltage at y : V R (y) = v GS - v(y) Depletion width at y: X(y) = NA 2ε 1+ qN A ND ψ o+V R (y) = K 1 ψ o+V R(y) = K 1 ψ o + v G S - v(y) The channel width at y : b(y) = 2a - 2X(y) = 2a - 2K 1 ψ o + v G S - v(y) ECE 4430 - Analog Integrated Circuits and Systems P.E. Allen, 2000 JFETs (5/11/00) Page 5 Derivation of the JFET Large Signal Model Based on the previous slide. 1.) Ohm’s law for conduction in the channel: -iD dV(y) Jy = σΕy ⇒ = σ Wb(y) dy where W = width of the channel perpendicular to the plane of the previous view. 2.) Since iD is constant in the channel, integration of the above gives, v(L) L iD ⌠ ⌡b(y)dv ⌡dy = σ W ⌠ 0 0 where v(L) is the voltage at a distance of L from the source designated also as v’DS. 3.) Substituting b(y) into the above and performing the integration gives, 2 K1 2 K1 3/2 3 / 2 iD = Go v’ DS + ( ψ + v v’ ) ( ψ + v ) GS DS o GS 3 a o 3 a where 2aσW Go = L 4.) The quantity a can be determined by noting that the depletion layer width, X(y), equals half the channel depth when vR(y) = Vp where Vp is the pinch-off voltage. ∴ a = X(y) = K1 ψo+Vp 5.) Substituting into the above gives, 3/2 - ( ψ + v 3 / 2 2 ( ψ o + v G S - v’ D S ) o GS ) iD = Go v’ DS + 3 (ψ o + V p )1 / 2 ECE 4430 - Analog Integrated Circuits and Systems P.E. Allen, 2000 JFETs (5/11/00) Page 6 Output Characteristics of the p -channel JFET Channel not yet pinched off: iD 3 -Vp - 4 Vp -(Vp-Vx) v'DS VGS=Vx VGS= 41 Vp VGS=0 IDSS Fig.1.5-4 Pinch-off occurs when v GS - v’DS = V p (It is found by differentiating iD with respect to v’DS and setting it equal to zero.) If IDSS is defined as the value of iD when vGS = 0, (v’DS = Vp) we may write the previous expression as, 3/2 - ( ψ ) 3/2 2 ( ψ o - v’ DS ) o IDSS = G o V p + 1 / 2 3 (ψ o + V p ) ECE 4430 - Analog Integrated Circuits and Systems P.E. Allen, 2000 JFETs (5/11/00) Page 7 JFET in Pinch-Off ,,,,,, ,,,,,, ,,,,,, Channel Pinched-off n+ emitter X(y) v(y) 2a A b(y) iD X(y) Vp VDS n collector L y Fig. 1.5-5 0 L Note: The current does not stop flowing when the channel is pinched off. It does however stop increasing with increasing vDS and becomes flat as shown below. -(Vp-Vx) 3 -Vp - 4 Vp iD v'DS VGS=Vx VGS= 41 Vp VGS=0 ECE 4430 - Analog Integrated Circuits and Systems IDSS Fig.1.5-6 P.E. Allen, 2000 JFETs (5/11/00) Page 8 Transconductance Characteristics of the JFET In the pinch-off region, the drain current can be closely approximated by v G S2 iD = IDSS 1 - V p The transconductance characteristic plotted from this equation looks like the following. iD/IDSS 1.0 0.8 0.6 0.4 0.2 0 0 0.2 0.4 0.6 0.8 vGS 1.0 Vp Fig. 1.5-7 The value of pinch-off voltage can be expressed as, NA qNA1+ N D Vp = a2 - ψo 2ε Typical values are 2-4V. ECE 4430 - Analog Integrated Circuits and Systems P.E. Allen, 2000 JFETs (5/11/00) Page 9 Channel Modulation in JFETs As the drain-source voltage increases beyond v GS -V p , the depletion region formed between the drain and the source becomes slightly wider and the effective channel length (point A on a previous slide) below becomes smaller, causing the drain current to increase slightly with increasing vDS. This is called channel modulation and is characterized by the parameter λ (V-1). -(Vp-Vx) 3 -Vp - 4 Vp iD − 1λ v'DS VGS=Vx VGS= 41 Vp VGS=0 Fig.1.5-8 The modified model in pinch-off is: v G S2 iD = IDSS 1 - V (1+λvDS), p v DS ≥ v GS -V p and v’DS ≈ vDS λ ≈ 0.01V-1 and is analogous to the reciprocal of the Early voltage, VA. ECE 4430 - Analog Integrated Circuits and Systems P.E. Allen, 2000 JFETs (5/11/00) Page 10 Summary of the JFET Large Signal Model Large signal model: G + vGS S D 2 IDSS(1 -vGS ) Vp S Fig. 1.5-9 Signs for the JFET variables: Type of JFET Vp IDSS vG S p-channel Positive Negative Normally positive n-channel Negative Positive Normally negative ECE 4430 - Analog Integrated Circuits and Systems P.E. Allen, 2000 JFETs (5/11/00) Page 11 JFET Breakdown Voltage Output characteristics: iD -7 -6 BVDGO -5 -4 -3 -2 -1 vDS VGS = 1.0V VGS = 0.5V VGS = 0V -1mA -2mA Fig.1.5-10 Note that, BV DG = BV DGO - V GS ECE 4430 - Analog Integrated Circuits and Systems P.E. Allen, 2000 JFETs (5/11/00) Page 12 JFET SMALL SIGNAL MODEL Frequency Independent Small Signal Model Schematic: D id + vgs gmvgs - G ro S D + vds - G Fig.1.5-11 S Parameters: diD 2IDSS V GS V GS gm = dv Q| = - V 1+ V = gm01+ V GS p p p where 2IDSS gm0 = - V p diD | V GS 2 1 ro = = λ I 1+ ≈ DSS dvDS Q Vp λID Typical values of IDSS and Vp for a p-channel JFET are -1mA and 2V, respectively. With λ = 0.02V-1 and ID = 1mA we get gm = 1mA/V or 1mS and ro = 50kΩ. ECE 4430 - Analog Integrated Circuits and Systems P.E. Allen, 2000 JFETs (5/11/00) Page 13 Frequency Dependent Small Signal Model Complete small signal model: D Cgss G Cgd G + vgs Cgs id D D + gmvgs ro S vds G S Fig.1.5-112 S All capacitors are reverse biased depletion capacitors given as, Capacitance from the source side of the channel to the top and bottom gates: Capacitance from the drain side of the channel to the top and bottom gates: Capacitance from the gate (p-base) to substrate: Cgs0 Cgs = V G S1/3 1+ ψo Cgd0 Cgd = V G D1/3 1+ ψo Cgss0 Cgss = V G S S1/2 1+ ψo It can be show than gm 1 f T = 2π C + C + C = 30MHz if gm = 1mA/V and Cgs + Cgd + Cgss = 5pF gs gd gss ECE 4430 - Analog Integrated Circuits and Systems P.E. Allen, 2000