Fundamentals of the Electronic Counters

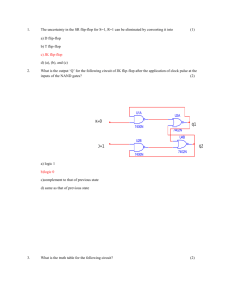

advertisement