PHYS 432 – Lab 2: Decoding, Multiplexing, and Sequencing

advertisement

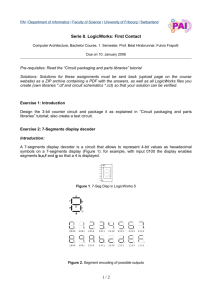

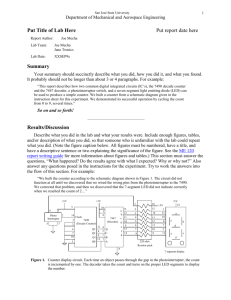

PHYS 432 – Lab 2: Decoding, Multiplexing, and Sequencing Parts List • ICs: 7404, 7493, 74138, 74151, 7-seg display Note: Each section of this lab largely builds upon the section before it. If you plan a little carefully, you can minimize the amount of rewiring you will have to do. 2.1 Decoder A decoder uses an input address to select one of many possible outputs. Multiplexers use a decoder to select which input line gets sent to the output. The 74138 IC is a 3-bit decoder. That is, it decodes a 3-bit binary number (the 3 address inputs) to select one of 23 = 8 possible outputs. Part of the 74138 data sheet is attached for reference. Note that there is also a 4-bit decoder version, the 74154. Construct the circuit shown in Fig. 1. The 7493 is a 4-bit binary counter that we first saw in lab 1. We will learn more about counters later, but its basic function is simple: it counts the number of pulses input on pin 14. The 4 binary digits representing this count are output on pins 12, 9, 8, and 11, as shown in Fig. 1. We need 3 bits of counter output to set up different addresses for the decoder. Since we only need 3 bits of information, we are only going to use the lowest 3 bits of output into our decoder. It won’t matter what the highest bit is doing, the lower 3 bits will still count from 0-7 as we would expect. Use a debounced switch on your prototype board to generate the counter input pulses. Check that the counting is proceeding correctly using the 7-segment display, as shown. Make sure to tie the highest bit low or you may get funny results. Toggle through all address inputs to the 74138 and measure the state of the 8 outputs. The outputs can be measured using a scope, logic probe, DVM, or the LEDs on your prototype board, although I would encourage you to use a logic probe. Hence, determine and record the truth table for the 74138. Does it use “positive true” or “negative true” logic ? binary (BCD) input 4 bits a0 a1 a2 a3 7 outputs (a!g) 7447 7!segment display circuit board +5 V 5 7 2 7493 8 a2 3 9 a1 2 a0 1 12 7 10 74138 1 16 +5 V LED logic 12 indicators 14 15 6 4 10 11 13 14 pulse in output 7 9 5 output 0 8 gnd Figure 1: Decoder circuit schematic. Note that pin 8 of the 74138 is not an output. 1 2.2 Sequencer A sequencer is a decoder for which the input is incremented sequentially by a counter. The sequence can continuously repeated by resetting the counter. Hence, this is functionally the same as the previous circuit, except now we will include a “programmable” reset function. This is shown in Fig. 2. Any one of the decoder outputs can be inverted and sent to the counter reset (pin 2), as shown. If, for example, output channel n = 5 (of the channels 0–7) is connected to the counter reset, what will be the highest count that you see on the 7-segment display? Why is the 7404 inverter needed? binary (BCD) input 4 bits a0 a1 a2 a3 7 outputs (a!g) 7447 7!segment display circuit board +5 V 5 7 7493 8 a2 3 9 a1 2 12 a0 1 7 10 74138 1 16 15 6 10 2 12 14 14 gnd 11 13 +5 V pulse in output 7 9 4 5 output 0 8 7404 Figure 2: Sequencer circuit schematic. Note that pin 8 of the 7442 is not an output. Be sure to connect the reset of the 7490 (pin 2) via a 7404 inverter, as shown. 2.2.1 Now connect up the circuit of Fig. 2. Does it work as expected? Vary the position of the connection to the reset and determine the maximum and minimum number of channels which can be sequenced. 2.3 Demultiplexer Consider Fig. 3. While a decoder is often used as part of a multiplexer, in this configuration the 74138 decoder becomes a 1 → 8 demultiplexer. Recall that a demultiplexer (“DEMUX”) routes data on a single input to one of several possible output locations, as selected by an input address. In this case, the three address bit inputs are used to select the output location, while one of the enable lines becomes the data input. To see how this works, look at the 74138 truth table. For a given selected output, what do the outputs look like when pin 4 (G2) is HIGH compared to LOW? Construct the circuit shown in Fig. 3. Use a slow (∼ 1 Hz) TTL square wave as the data input. Select an output channel using either logic switches, or just use the 7493 you had used in the previous section. Make sure you know what channel is selected, however, by looking at the 7-segment display. Connect the outputs 0–7 to the 8 logic LEDs on your prototype board. Does the input data appear at the selected output? What appears at the other channels? Repeat with a different channel. Show that the input data gets properly routed to output lines 0 to 7 based on the address. Here we used pin 4 for the data input, which is the 2 data in logic switches 4 7 a2 3 9 a1 2 a0 1 +5 V gnd output 7 10 11 74138 12 LED logic 13 indicators 6, 16 14 5, 8 15 output 0 Figure 3: Demultiplexer circuit schematic. “negative true” enable line. Does this also work if the data is input to the pin 6 “positive true” enable line? Is there a difference in the output compared to the input? 2.4 Multiplexer-demultiplexer Here we will construct the circuit of Fig. 4, which consists of a multiplexer (74151) which sends data to a demultiplexer (74138) over a single line. Hence the two devices communicate via a serial data link. Sending data over such a serial link clearly saves making many connections, which is of practical importance. The MUX and DEMUX use the 3-bit address bus shown in Fig. 4 to communicate which data channel is active. In your circuit, the address code will be selected using a counter (7493), as was done earlier. Again, the 7-segment display is used to display this address. +5 V 10 7 binary (BCD) input 4 bits 5 7 outputs (a!g) 8 2 9 7493 a0 a1 a2 a3 12 7447 1 7!segment display address select in circuit board 14 +5 V 6, 16 data in 7 12 13 14 15 74151 9 a2 3 10 a1 2 11 a0 1 7 10 74138 1 data in address bus 2 3 data in 0 5 11 LED logic 12 indicators 13 4 14 4 15 16 +5 V 7 8 data link output 7 9 5 output 0 8 Figure 4: Schematic for serial data transmission via MUX/DEMUX. Connect the circuit shown in Fig. 4. The data to be transmitted (“data in”) can again be a slow TTL pulse train. And a debounced button input to the 7493 counter can again be used to select the address. Increment the counter to select output channel 5. Which data pin(s) on the 74151 (data in) and 74138 (data out) have been selected? Verify this with a logic probe or LED. Now input data to this active 74151 pin. Does the input data get faithfully transmitted to the correct output? Move the data input to a different MUX pin. Now select this channel. Does data now appear at the 74138? At which channel? 3