Lab 4

Lab 4: Introduction to Top-Down Design

Check Off by Thursday Feb26. , 2009

Summary

This lab introduces students to top-down design by constructing a multiplexer and an 8-bit adder using the syntheses and place-and-route (layout) tools from Synopsys and Cadence.

Learning Objectives

1. How to perform synthesis with Synopsys’ Design Vision

2. How to perform place and route with Cadence’s Silicon Ensemble

3. How to import GDSII files into Virtuoso for simulation

Estimated Time to Complete Assignment: ~6 hours plus report preparation

Resources

Tutorial PnR and files located at /egr/courses/personal/ece410/resources/

Procedure

NOTE : YOU NEED TO LOG INTO mulder.egr.msu.edu OR madras.msu.edu INSTEAD

OF deus.egr.msu.edu USING PUTTY

1. Complete the Place and Route tutorial, Tutorial PnR , on the class website. Save/print a copy of the final layout and simulation results for your report.

2. While doing Tutorial PnR you copied the Verilog file for an 8-bit adder to the /synopsys folder in your class directory. The file is called adder8.v. Confirm you have this file. If not, you can copy it from /egr/courses/personal/ece410/resources/adder8.v

.

3. Synthesize the adder8.v with Synopsis Design Vision using the methodology in Tutorial PnR .

Note that this is a Verilog file, not a VHDL file, so you should skip step 4 under Synthesis with

Synopsys Design Vision.

4. Place and route the 8-bit adder with Cadence Silicon Ensemble . Follow the procedure in the tutorial, but in Step 11 use "adder8" as the "Top Verilog Module". To make your class directory well organized, you may want to create a folder, say adder8 , and run Cadence’s Silicon Ensemble in that folder, e.g., /egr/courses/personal/ece410/<username>/se/adder8. When renaming multi-bit pins, use the format A<1> rather than the form A[1] produced by default from the compiled layout.

5. Explore the floorplan settings within Silicon Ensemble , such as Die Size Constrain, and Core

Area Parameters by filling out the following table. This step only needs to be performed within

Silicon Ensemble by repeating steps 16-29 in the Place & Route with Cadence Silicon Ensemble section of the Tutorial PnR . Include this data within the appropriate Discussion Topic of your report. Be sure you can respond to Discussion Topic 2 before continuing.

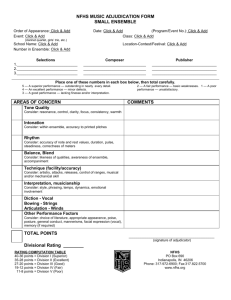

IO To core distance Die size

Aspect

Left/right Top/Bottom

Ratio

Row utilization

Row

Spacing

Block

Halo per

Side

Die Dimensions

Width height Area

6. Using what you have learned about the floor plan parameters, place and route the 8-bit adder with a die area less than 15,000μm

2

. Include within the appropriate Discussion Topic of your report the height, width, and area obtained for an area-optimized layout.

7. Import the adder8 GDSII file into Virtuoso, and perform a functional simulation of the adder.

Create a stimulus file (or three separate files, if you prefer) that will test the three 8-bit additions below. Stimulus file pin names should be consistent with the layout pin names. Verify the outputs produce accurate binary addition. Note, this is a case where you might want to write information on your simulation plot.

A) 11111111+00000000

B) 00000001+11111111

C) 10101010+01010101

8. Print the Lab 4 Grading Sheet and meet briefly (~5 min.) with a TA to check off your lab by

5pm on Wednesday.

9. Construct a Brief Report of this assignment using the Guide to Writing Lab Reports . Be sure to include responses to the Discussion Topics below. Reports are due by the beginning of class on

Monday but can be turned in to a TA earlier.

Deliverables

Description Check off Lab report

Layout of the multiplexer and 8-bit adder

Functional simulation of the multiplexer and 8-bit adder

Width, height, and area of your 8-bit adder

X

X

X

X

X

Discussion of pros/cons of top-down design X

Discussion Topics:

Include type-written responses to the following discussion topics in your brief report.

1. Briefly discuss the advantages and disadvantages of top-down design (synthesis and placeand-route) verses the full custom (bottom-up) design flow.

2. In step 5 you were able to observe the effect of several floor planning parameters on the overall size of the adder8 layout. Include the completed table from step 5 here. Briefly comment on the following: a. What is the effect of the Die Size constraints and the I/O to Core Distance? b. What does Row Utilization % represent and how does it effect the area?

3. What height, width, and area did you obtain for an area-optimized adder8 layout in step 6?

4. List the binary and decimal adder8 output values obtained for the three input cases in step 7.

5. Briefly describe why both Design Vision and Silicon Ensemble are used in this lab. Include information like, what is created or modified by each tool, and what is the output of each tool.

6. Briefly explain why cells must be imported from Silicon Ensemble to Virtuoso.

7. In using Silicon Ensemble, what is the main design factor (i.e., what role does the designer – you in this case- play)?