DSP MEMORY MAP

advertisement

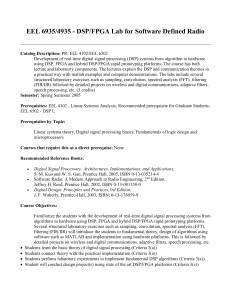

The ATLAS Liquid Argon Calorimeters Read Out Driver (ROD) The TMS320C6414 DSP Mezzanine board Abstract : In this document, a detailed description of the ATLAS Liquid Argon Calorimeters Read Out Drivers prototype mezzanine designed around the TMS320C6414 from Texas Instrument, is given. The document is organized as follows : after an overall presentation of the board, the functionality of the main components are described. The document ends with miscellaneous points as power supply, JTAG, board technical considerations and planned cost. Author : Julie PRAST Web page : http://wwwlapp.in2p3.fr/Electronique/Experiences/ATLAS-ELEC/Rod/index.html File name : pu6414final.doc Created : June 2002. Last updated : 04/09/2002 Version : 1.2 The TMS320C6414 Processing Unit 08/03/2016 1/23 1 Table of contents 1 TABLE OF CONTENTS .............................................................................................................................. 2 2 OVERALL PRESENTATION..................................................................................................................... 3 2.1 2.2 3 INTRODUCTION ........................................................................................................................................ 3 THE TMS320C6414 MEZZANINE FINAL ARCHITECTURE .......................................................................... 3 MAIN COMPONENTS ................................................................................................................................ 4 3.1 THE INPUT FPGA ..................................................................................................................................... 4 3.1.1 Parallelisation and control ............................................................................................................. 4 3.1.2 Data organization in the internal dual port memory ...................................................................... 5 3.1.3 DSP interface .................................................................................................................................. 5 3.2 THE DSP .................................................................................................................................................. 6 3.2.1 EMIFA ............................................................................................................................................. 6 3.2.2 EMIFB ............................................................................................................................................. 6 3.2.3 Host Port Interface (HPI)................................................................................................................ 6 3.2.4 McBSP ............................................................................................................................................. 6 3.2.5 Interrupts and general purposes Pins ............................................................................................. 7 3.3 THE OUTPUT FPGA ................................................................................................................................. 7 3.3.1 The TTC interface............................................................................................................................ 7 3.3.2 The VME interface .......................................................................................................................... 8 3.4 THE OUTPUT FIFO ................................................................................................................................... 9 4 POWER SUPPLY AND JTAG .................................................................................................................. 10 4.1 4.2 5 POWER-SUPPLY ...................................................................................................................................... 10 JTAG CHAIN .......................................................................................................................................... 10 MISC ............................................................................................................................................................ 10 5.1 5.2 5.3 5.4 BOARD TECHNICAL CONSIDERATIONS ................................................................................................... 10 ESTIMATED COST ................................................................................................................................... 10 AVAILABILITY OF COMPONENTS AND TOOLS.......................................................................................... 11 COMING MILESTONES ............................................................................................................................. 11 6 REFERENCES ............................................................................................................................................ 11 7 ABBREVIATION ....................................................................................................................................... 12 8 ANNEXES.................................................................................................................................................... 13 8.1 8.2 ANNEXE 1 : ADC READ OUT INPUT EVENT FORMAT .............................................................................. 13 ANNEXE 2 : SCHEMATICS, ROUTING AND PLACEMENT........................................................................... 14 The TMS320C6414 Processing Unit 08/03/2016 2/23 2 Overall presentation 2.1 Introduction To assess the feasibility of the project, the ATLAS LAr collaboration has decided in 1999 to make a ROD (Read Out Drivers) demonstrator. The project consisted in the construction of a motherboard (developed by the University of Geneva, Switzerland), into which could be plugged up to 4 daughterboard processing units (PU), each PU treating 64 calorimeter channels (an half FEB). The architecture of the PU was based around a Digital Signal Processor (DSP). Three PU were designed, two based on an integer DSP the TMS320C6202 from Texas Instrument (developed by the CPPM-Marseille-France and Nevis-USA) and the other based on a floating point processor the ADSP21160 from Analog Devices (developed by the LAPP- Annecy- France). The techniques evolution and the arrival of a new powerful DSP opens the possibility to double the system density by handling 128 channels instead of 64 in a single DSP. That’s why in the second half of 2001, an evaluation board based around the TMS320C6414 from Texas Instrument were developed, conjointly by Nevis and LAPP teams. This DSP was finally adopted by the ROD community for the final board last June. The final design consists of 4 daughterboards per ROD module, each daughterboard equipped with two DSP, increasing the ROD density to 8 FEB per DSP, instead of two in the demonstrator. Further more, for financial reasons, the ROD system should provide staging capabilities. In the staging scenario, a daughterboard among two, will be populated on the motherboard at the beginning of the experiment, bringing to 256 the number of channels treated by a single DSP, at the expense of potential loss in performance (reduced trigger rate). This document aims to describe the final daughter board architecture. 2.2 The TMS320C6414 mezzanine final architecture Figure 1 shows the TMS320C6414 mezzanine final architecture : InFPGA config TMS320C6414 FEB1 16 EMIF B Input FPGA 64 FEB3 Apex 20k160 16 FEB4 Input FPGA 16 Apex 20k160 64 FIFO 4k*16 EMIFA McBSP2 EXT_INT HPI 16 McBSP0 16 FEB2 16 Output FPGA Acex 1k30 McBSP1 TTC interface TMS320C6414 VME interface EMIFA HPI McBSP0 McBSP1 TTC VME BCID TType FIFO EXT_INT McBSP2 EMIF B 16 16 16 4k*16 16 JTAG InFPGA config Figure 1 : TMS320C6414Mezzanine block diagram The mezzanine is a 120*85 mm board, composed of two 64 pins and one 84 pins connectors that can be plugged on the motherboard. The mezzanine is composed of two processing units (PU), able to treat each up to 128 calorimeter channels (1 FEB) in normal mode and 256 channels (2 FEB) in staging mode. Each PU is composed of an input FPGA (InFPGA), a TMS320C6414 DSP from Texas Instrument and an output FIFO. The mezzanine contains also an output FPGA (OutFPGA) used for the VME and TTC interface. Input FEB data enters the InFPGA where they are formatted and checked as needed for the DSP algorithm. When an event is ready, an interrupt is sent to the DSP which launches a DMA to read the data on the 64-bits The TMS320C6414 Processing Unit 08/03/2016 3/23 EMIFA bus. Once the DSP has finished processing an event, it writes the results in the output FIFO through the 16 bits EMIFB bus. The TTC data are received in the OutFPGA and sent to each DSP via 2 serial ports (McBSP). A serial port is for the Trigger type and the other is for the BCID and EventID. The OutFPGA allows the control of the board by VME, in particular : - DSP boot written and histograms read through the 16-bits Host Port Interface (HPI) of the DSP. - Full duplex serial port (McBSP2) with each DSP (run number written, DSP commands, status read) - InFPGA configuration written (number of samples, number of gains, mode…) and status read through a serial line. - InFPGA boot. 3 MAIN COMPONENTS 3.1 The input FPGA The InFPGA parallelizes incoming FEB data, verifies their consistency (in particular potential corruption coming from radiation effects, like SEU), and formats the data as needed for the DSP algorithm. The InFPGA is an APEX20k160EBC208-1 from Altera. The choice of this component is described in references [3]. The InFPGA has three main parts : 1. Parallelization and control of the incoming data. 2. Data organization in the dual port memory. 3. DSP interface. Figure 2 shows the InFPGA architecture in staging mode, ie when treating 2 FEBs: 16 ADC1 // 16 bits @ 80 Generation of timing signals + data and synchro check MHz M U X 16 Data organization in double port RAM (64 bits wide) INT4 64 DSP Interface CS1 ADC16 // Parallelization of 2 HFEB 64 ADC1 // 16 bits @ 80 16 Generation of timing signals + data and synchro check MHz M U X 16 Data organization in double port RAM (64 bits wide) 64 ADC16 // DSP Interface INT5 CS2 Parallelization of 2 HFEB Figure 2 : Input FPGA architecture (staging mode) 3.1.1 Parallelisation and control The InFPGA receives input data from the mother board through two 80 MHz 16-bits bus. Each 16-bits bus corresponds to one FEB (128 channels = 16 ADC). In normal mode, the InFPGA treats one FEB, whereas in staging mode, the InFPGA treats two FEBs. The format of the incoming data is described in annexe 1. The TMS320C6414 Processing Unit 08/03/2016 4/23 For each FEB, timing signals are generated internally (indication of the data type : header, RADD, data, …) For each ADC, the InFPGA detects the start of event and does the serial to parallel conversion (2 bits -> 16 bits). For each word, except the start and end of event, the parity is checked. For each data word, the gain is isolated and compared to the other gains of the same channel. Gains from 8 channels are grouped in 16 bits data words. Several checks are performed : Parity check. Start of data alignment to check half-FEB (HFEB) desynchronization. Identical gain for all samples of a given channel. Identical control words and RADD within an HFEB. Identical control words and RADD between two HFEB. When en error is detected, the InFPGA fills the event status word. This word is interpreted by the DSP in the synchronization task. If the status is different to zero, the DSP will take the appropriate decision, as asking for a FEB reset. The synchronization task is described in more details in reference [10]. The content of the event status word is described below: 31 26 25 0 Radds 24 23 bcids gain or BOF parity ctrl3 gain Table 1 : Content of the event status word. 8 7 6 5 4 3 2 1 0 radd ctrl2 ctrl1 ones bit 0 ones : The beginning of event is missing in one of the 16 groups of channels. bit 1 ctrl1 : Ctrl1 mismatch bit 2 ctrl2 : Ctrl2 mismatch bit 3 radd : RADD mismatch bit 4 gain : Gain mismatch (the gain bits are not preserved across the time samples, for some channels) bit 5 ctrl3 : CTRL3 mismatch [7..6] parity: Parity errors counts (0 = no error, 1 = 1 error, 2 = 2 errors, 3 = 3 or more errors) [23..8] gain or BOF In case of error in the gain or BOF, precise which group of channels is concerned (bit 8 = ch0) bit 24 bcids comparison between BCID of channels 0-63 versus channels 64-128 bit 25 radds comparison between RADD of channels 0-63 versus channels 64-128 3.1.2 Data organization in the internal dual port memory Data is then organized in a dual port memory as needed to optimize the DSP algorithm. The data format is presented below : 0 bits [63..48] Event status bits[47..32] Event status bits [31..16] EventID bits[15..0] BCID 1 ctrl1 ctrl2 ctrl3 Radd1 2 Radd2 Radd3 Radd4 Radd5 3 C0 Gain C0 S1 C0 S2 C0 S3 4 C0 S4 C0 S5 C1 gain C1 S1 5 C1 S2 C1 S3 C1 S4 C1 S5 6 C2 Gain C2 S1 C2 S2 C2 S3 194 C127 S2 C127 S3 C127 S4 Table 2 : Dual port memory organization C127 S5 The dual port memory of the InFPGA is configured as a dual bank memory. While the DSP is reading a complete event from one bank, a new event can be written into the other bank. Therefore, the minimal size of the InFPGA dual port memory is two events. Please refer to note [3] for more details about the dual port memory organization. 3.1.3 DSP interface When a complete FEB event is stored in the memory, the InFPGA sends an interrupt to the DSP. The DSP then launches a DMA to read the event. The reading is cadenced by the DSP clock. The frequency is configurable, The TMS320C6414 Processing Unit 08/03/2016 5/23 but it is today foreseen at 100 MHz (CPU/6). From the reading side, the internal dual port memory of the input FPGA is seen by the DSP as a FIFO, implying that the data is read in consecutive addresses. There is one interrupt and DSP chip select per FEB. 3.2 The DSP The DSP is the 600 MHz TMS320C6414GLZ, which is among the latest generation of the Texas Instrument DSP. The DSP receives FEB data on its EMIFA memory bus, TTC information on serial ports McBSP0 and McBSP1 and transmits the output data through its EMIFB memory bus. The Host Port Interface (HPI) is used to boot the DSP and read histograms. Details about the DSP code are given in the following references : Input /output management and code structure: see reference [5] Real time operating system : see reference [11] Physics code : see reference [12] Paragraphs bellow summarizes the DSP communications. 3.2.1 EMIFA The External Memory Interface A (EMIFA) is directly connected to the InFPGA. The EMIFA is a 64 bits wide bus. The EMIFA clock AECLKOUT2 is generated internally and is configured to run at CPU/6 = 100 MHz. This EMIFA is used to read input FEB data in the InFPGA. As a dual port RAM is foreseen in the InFPGA for each FEB, one interrupt and one Chip Enable (CE) are foreseen per FEB. CE R/W Connected to Purpose Mode CE0 DSP memory address 8000 0000 R InFPGA FEB 1 DP-RAM synchronous read interface. CE1 9000 0000 R InFPGA FEB 2 DP-RAM (staging) synchronous read interface. CE2 A000 0000 InFPGA Connected but not defined CE3 B000 0000 InFPGA Connected but not defined Table 3 : EMIFA memory map 3.2.2 EMIFB The External Memory Interface B (EMIFB) is directly connected to the output FIFO. The EMIFB is a 16 bits wide bus. The EMIFB clock BECLKOUT2 is generated internally and is configured to run at CPU/6 = 100 MHz. This EMIF is used to send output events to the FIFO. CE DSP memory address R/W Connected to Purpose Mode CE0 6000 0000 W Output FIFO Output FIFO write synchronous write interface CE1 6400 0000 W Output FPGA end of output DMA synchronous write interface / Connected but not defined CE2 6800 0000 CE3 6C00 0000 3.2.3 / Connected but not defined Table 4 : EMIFB memory map Host Port Interface (HPI) The HPI is a parallel port through which the VME (host processor) can directly access the CPU’s memory space. The VME has ease of access because it is the master of the interface. The host and CPU can exchange information via internal memory. For more details about the HPI, have a look on reference [6], chapter 7. On the mezzanine board, the HPI is configured as a 16-bits wide bus connected to the output FPGA. The HPI is mainly used for the DSP boot, histograms reading and debugging purposes. VMER/W connected to Purpose Mode W output fpga Boot No particular configuration R Output fpga Histograms, debug variables Table 5 : HPI description. No particular configuration Note : During DSP reset, the OutFPGA pulls down the HD5 signal to configure the HPI as a 16 bits words interface. 3.2.4 McBSP The TMS320C6414 Processing Unit 08/03/2016 6/23 The Multi channel Buffered Serial ports are Full duplex communication DSP serial ports, with independent framing and clocking for receive and transmit. The TMS320C6414 has 3 McBSP connected to the output FPGA. McBSP0 and McBSP1 are used for TTC data (DSP receives only), while McBSP2 is bi-directional and used to send commands to the DSP or to read the DSP status. R/W Connected to Purpose McBSP0 McBSP R output FPGA BCID + Event ID McBSP1 R output FPGA Trigger type transmission McBSP2 R/W outputFPGA DSP Commands write DSP status read, … Table 6 : McBSP description 3.2.5 Interrupts and general purposes Pins Table 7 summarizes the DSP General Purposes (GP) configuration pins. GP function Connected to Purpose GP0 Output GP InFPGA Input FPGA led1 blanking GP1/CLKOUT4 NC GP2/CLKOUT6 NC GP3 Output GP InFPGA Input FPGA led1 blanking GP4/EXT_INT4 interrupt InFPGA Interrupt dedicated to FEB1 DMA GP5/EXT_INT5 interrupt InFPGA Interrupt dedicated to FEB2 DMA GP6/EXT_INT6 interrupt InFPGA Not defined GP7/EXT_INT7 interrupt InFPGA Not defined GP8/CLKS2 NC GP9 Output GP Connector B PU_IRQ GP10 Output GP Connector B BUSY GP11 Input GP OutFPGA FIFO almost full GP12 OutFPGA Not defined GP13 OutFPGA Not defined GP14 OutFPGA Not defined GP15 3.3 NC Table 7 : interrupts and general purposes pins The Output FPGA The OutFPGA is an ACEX EP1k30FC256-2 from Altera. This FPGA has 2 main purposes: the TTC and VME interface. It boots from an EPC2 (eeprom) at power up. 3.3.1 The TTC interface The OutFPGA drives the TTC data coming from the motherboard TTC FPGA and going to both DSP through 2 serial ports also called McBSPs. McBSP0 is reserved for the BCID and event ID, whereas the McBSP1 is reserved for the Trigger type. The communication protocol is described in the figure bellow : 40 MHZ Clock TTCx_BCID_Frame MSB BCID 12 bits MSB TTCx_BCID_Data EVTID 32 bits TTCx_TType_Frame TType 8 bits 08/03/2016 MSB The TMS320C6414 Processing Unit MSB TTCx_TType_Data TType 8 bits 7/23 Figure 3 : TTC communication protocol The protocol for BCID corresponds to a frame having 2 phases of different length one for the BCID and the other for the EVTID each having one element. There must be at least 2 clock cycles between each frame. For the TType there is one frame with only one phase and one element. There must be at least 2 clock cycles between each frame. You can get a detailed description of the Ti6414 McBSP in the manual TMS320C6000 Peripherals reference Guide chapter 12.2 and a detailed description of the TTC FPGA in reference [8]. 3.3.2 The VME interface The OutFPGA includes the VME interface of the mezzanine board. It decodes data coming from the motherboard and generates data according to the motherboard protocol. The communication protocol between the mezzanine and the mother board is described in reference [4]. Table 8 summarizes all the OutFPGA registers that can be accessed by VME (32 bits wide). PU_add[4..0] 0 1 2 3 4 5 6 7 8 9 VMEadd +0 +4 +8 +C +10 +14 +18 +1C +20 +24 R/W R/W R R/W W W R W W R R Function control 1 register Status 1 register HPI register (DSP1) Broadcast HPI register (both DSP) serial data to McBSP2 (DSP1) Serial data from McBSP2 (DSP1) InFPGA configuration data (8 MSB) both InFPGA InFPGA configuration register (15 LSB) both InFPGA InFPGA1 status register (15 LSB) Test register 16 17 18 19 20 21 22 23 24 28 +40 +44 +48 +4C +40 +54 +58 +5C +60 +64 R/W R R/W W W R W W R R control 2 register Status 2 register HPI register (DSP2) Broadcast HPI register (both DSP) serial data to McBSP2 (DSP2) Serial data from McBSP2 (DSP2) InFPGA configuration data (8 MSB) both InFPGA InFPGA configuration register (15 LSB) both InFPGA InFPGA2 status register (15 LSB) Test register Table 8 : VME Memory Map The paragraphs bellow detail the purpose of each register. 3.3.2.1 Control register The control register is described in table 9: Bit number R/W Bit wise operator Functionality 0 R/W 0000 0001 DSP reset 1 R/W 0000 0002 FIFO reset 2 R/W 0000 0004 Input FPGA reset 3 R/W 0000 0008 HPI reset 4 R/W 0000 0010 HPI burst 5 R/W 0000 0020 6 R/W 0000 0040 Table 9 : Control Register DSP launch /Input fpga nconfig 3.3.2.2 Status register The status register is described in table 10: The TMS320C6414 Processing Unit 08/03/2016 8/23 Bit number [7:0] 8 9 10 11 12 14 15 R/W R R R R R R R R 24 25 26 27 28 29 30 31 R R R R R R R R Bit wise operator 0000 00FF 0000 0100 0000 0200 0000 0400 0000 0800 0000 1000 0000 4000 0000 8000 Functionality Number of events in the output FIFO. output FIFO empty flag output FIFO almost full flag output FIFO half full flag output FIFO Almost full flag output FIFO full flag Data from McBSP2 available Serial port buffer overwritten by new data from McBSP2. 0100 0000 0200 0000 0400 0000 0800 0000 1000 0000 2000 0000 4000 0000 8000 0000 Table 10 : Status register GP11 GP12 GP13 GP14 HPI INT HPI Ready InFPGA nstatus InFPGA confdone Note : the counter of the number of events currently in the output FIFO is increased by the DSP (dedicated Chip Select) and decreased with the output controller fifo_evt_end signal. 3.3.2.3 HPI interface The OutFPGA includes also the HPI interface, used for the boot of the DSP and for the read out of the histograms. Both DSP can be accessed in broadcast or independently through the specific registers. The way the HPI protocol is implemented in the output FPGA is described in [7]. 3.3.2.4 McBSP2 interface The OutFPGA has the possibility to exchange data with both DSP through the McBSP2 serial port. This serial port can be used to send commands to the DSP, to read the DSP status, …. 3.3.2.5 Input FPGA programming The OutFPGA allows the programming of the InFPGA from VME. The ability to re-program the InFPGA in situ without use of the byte blaster is important since there can be different versions of the InFPGA configuration code (eg. calibration code, the 32 samples code or the normal 5 samples code). The OutFPGA programs the InFPGA through the dedicated signals provided by Altera for FPGA configuration (data0, dclk, nconfig, …). The configuration is done at 5 MHz. Both InFPGA are configured at the same time. 3.3.2.6 Input FPGA configuration and status register The OutFPGA has also the possibility to dialog with each InFPGA through a home made serial protocol. This allows the configuration of the InFPGA and the access of the InFPGA status. Table 11 and 12 describe the content of these registers : 15 10 9 0 8 15 8 0xBE 3.4 7 5 Number of gains 0 Table 11 : InFPGA configuration register 7 6 0 Number of gains Table 12 : InFPGA status register 4 0 Number of samples 5 4 0 Number of samples The output FIFO The Output FIFO is an IDT72V253L7-5BC 3.3V high density super synchronous 18-bits bus FIFO. The FIFO is organized in 4 kilo words of 18 bits. The size of the FIFO is done assuming the following philosophy : We expect, in most of cases, that an entire event can be sent by the DSP. It allows the DSP to launch only one DMA and so not loose time. In seldom cases, when the event is big (raw data, ..), we accept loosing time and then slicing up the output event. Assuming 5 samples per event (most of cases), the output event size is about half of the input ie about 400*16 bits words per FEB. To store 2 events in the FIFO in staging mode, we need at least 1600 words. Due to the very small price difference between 2k and 4k depth FIFO and that they are pin compatible, the 4k FIFO is chosen for the prototype. The TMS320C6414 Processing Unit 08/03/2016 9/23 The FIFO has empty, full and programmable almost empty and almost full flags. These flags can be spied by VME through the status register . The offset value of the almost flag has been programmed to 1024 words, so that when this flag is not active, the DSP knows that there is enough place to write another event. On the final prototype, the use of the FIFO flags will allow to optimize the FIFO size for the production. The DSP can write the output events at full speed (100 MHz). 4 Power supply and JTAG 4.1 Power-supply The mezzanine board is supplied with an 3.3V unique voltage coming from the mother board and made from the VME 48V through a DC-DC regulator. The estimated power consumption is about 2.5A for the whole mezzanine. This estimation is based on previous studies performed with the TMS320C6414 evaluation board (5A measured for 4 evaluation PU based on a single TMS320C6414 running at 600MHz). The following voltages are derived from this 3.3V supply : - the 2.5 V for the input FPGA core with the regulator TPS76825Q from Texas Instrument. - the 1.8 V for the output FPGA core with the regulator TPS76818Q from Texas Instrument. - the 1.4 V for the DSP core with an adjustable regulator, the TPS54610 from Texas Instrument. - The 3.3V for the DSP input/output, which must be set up after the DSP core voltage and with specific setup requirements. 4.2 JTAG chain The JTAG chain includes in this order : DSP1, DSP2, InFPGA1, InFPGA2, EPC2, OutFPGA, FIFO1, FIFO2. The JTAG chain has 3 purposes on the board : 1. Boundary scan analyses: to verify interconnections (stuck at, short and open circuits) and identify defaults. Boundary scan is the main test foreseen to validate the electrical functionality of the mezzanine and more generally the ROD module. More details about these tools and the ROD test bench can be found in reference [9]. 2. Altera components programming : FPGAs and EPC2 configuration. 3. DSP emulation for debug purposes. For this, the chain can be shorten and only includes both DSP (the JTAG port of the DSP does not work properly if non-C64x devices are in the scan chain) The JTAG chain can be controlled either from the mother board or from the mezzanine. The JTAG connector on the mezzanine board is a 2*7 plug connector compatible with the emulator pad. This connector is foreseen on the board because it contains some pins specific for the DSP emulation that are not on the mother board interface. As it is for debug purposes, this connector should not be populated on the production version. 5 MISC 5.1 Board Technical Considerations The mezzanine is a 120*85*1.4 mm board. It is made of 10 layers, 6 signal layers and 4 power planes. The signal layers present almost the same impedance (around 50 ohm for a 0.120 mm wide net) to preserve signal integrity. The whole board is routed with through hole vias : - 0.5 mm diameter and 0.25 drill size under the DSP (0.8 mm BGA). - 0.6 mm diameter and 0.3 drill size elsewhere. Annexe 2 shows the electrical schemes, the placement description and the routing of each layer. 5.2 Estimated cost Table 13 gives the foreseen cost for the prototype board so for small quantities and today cost. It does not include manufacturer equipment ie about 800 € for the printed circuit and 1200 € for the assembler (to be paid once only). The TMS320C6414 Processing Unit 08/03/2016 10/23 Description Manufacturer Part number Quant/ board Unit cost (€) Total cost Printed circuit board production PCB assembly Total without components and without manufacturer equipment Techci Ardelec 1 1 250 150 250 150 400 Input FPGA Output FPGA DSP Altera Altera Texas Instrument EP20k160eqc208-1 EP1k30FC256-2 TMS320C6414GLZ532 2 1 2 180 35 200 360 35 400 Output FIFO EEPROM oscillator 50 MHz Zero delay buffer 64 pins connector 84 pins connector DSP voltage regulator InFPGA voltage regulator OutFPGA voltage regulator DSP PLL filter drivers passive components (resistors, capa, inductance, leds, small connectors) IDT Altera Mextal Cypress Tyco Electronics Tyco Electronics Texas instrument Texas instrument Texas instrument Texas instrument IDT72V253BC100 EPC2TC32 SWO3 CY2305SC-1 AMP120525-1 AMP120525-2 TPS54610PWP TPS76825QPWP TPS76818QPWP ACF321825 SN74LVTH125DGV 2 1 1 2 2 1 1 1 1 2 3 230 25 29 10 2,5 3,5 3,5 10 1 1 0,3 0,5 0,1 50 29 10 5 7 3,5 10 1 1 0,6 1,5 23 Vishay Fairschild SI4465DY MMBT3904 1 1 0,8 0,5 0,8 0,5 937,9 Mosfet canal P 1,8V Bipolair transistor NPN channel Total for components Table 13 : prototype Mezzanine estimated cost The estimated cost for the prototype mezzanine is about 1400 € (1000 € for components and 400 € for PCB and cabling) plus the cost of the manufacturer equipment (1200 €) divided by the number of mezzanine produced. 5.3 Availability of components and tools The components foreseen for the ROD mezzanine are recent and commercial chips. The FPGA (Altera products) should be maintained 5 years and the TMS320C6414 products, including tools, are guaranteed by Texas Instrument to be maintained and available during at least 5 years. 5.4 Coming milestones September 16-17 th : End of October : End of December : Beginning of 2003: March 2003 : Preliminary review Prototype production launch. Prototype ready to be tested. Prototype tests. Mother board tested with 4 PU. 6 REFERENCES [1] LAPP ROD web page : http://wwwlapp.in2p3.fr/Electronique/Experiences/ATLAS-ELEC/Rod/index.html [2] Daniel La Marra « Mezzanine board connectors.pdf » http://dpnc.unige.ch/LArgROD/Mezzanine Board Connectors.pdf [3] Julie PRAST : « Input FPGA in ROD PU. » July 2002. http://wwwlapp.in2p3.fr/Electronique/Experiences/ATLAS-ELEC/Rod/Document/finalS2P.pdf [4] Annie Leger “VME protocol” http://dpnc.unige.ch/LArgROD/VMEBusyFPGA.pdf [5] Nicolas Chevillot « ATLAS ROD TMS320C6414 DSP based processing Unit. TestDemo1.2. DSP Hardware and code structure. » August 2002 The TMS320C6414 Processing Unit 08/03/2016 11/23 [6] Texas Instrument “TMS320C6000 Peripherals Reference Guide” 2001 [7] Nicolas Chevillot “TMS320C6414 HPI interface” December 2001 http://wwwlapp.in2p3.fr/Electronique/Experiences/ATLAS-ELEC/Rod/Document/HPI.pdf [8] Guy Perrot “TTC FPGA” July 2002 http://wwwlapp.in2p3.fr/Electronique/Experiences/ATLAS-ELEC/Rod_ttc_fpga/TTC_FPGA.pdf [9] Guy Perrot “ROD Test Bench and integration tests” March 2002 http://wwwlapp.in2p3.fr/Electronique/Experiences/ATLAS-ELEC/Testbench/ROD_Testbench.pdf Gelu Ionescu “Busy generation, event verification, event synchronization ” September 2002 http://wwwlapp.in2p3.fr/informatique/Atlas_online/Documents/Dsp/ATL-ROD-RTX/AOS_ATLSYNC-ANA.pdf [10] Gelu Ionescu “RTX ” September 2002 http://wwwlapp.in2p3.fr/informatique/Atlas_online/Documents/Dsp/ATL-ROD-RTX/AOS_RTX-TISRS1.pdf [11] Remi Lafaye “The physics ROD 64x PU algorithm ” September 2002 http://wwwlapp.in2p3.fr/informatique/Atlas_online/Documents/Dsp/ATL-ROD-RTX/AOS_ATL-DSPPHYS.pdf [12] 7 ABBREVIATION BCID DMA DSP EMIF FEB FIFO HFEB HPI InFPGA McBSP OutFPGA RADD SEU Bunch Crossing Identifier Direct memory access Digital Signal Processor External Memory InterFace of the DSP. Front End Board First In First Out Half FEB Host port Interface of the DSP Input FPGA Multi channels Buffered Serial Port of the DSP Output FPGA Read address in the SCA (Switch Capacitors Table) Single Event Upset The TMS320C6414 Processing Unit 08/03/2016 12/23 8 ANNEXES 8.1 W1 W2 W3 W4 W5 W6 W7 W8 W9 W10 W11 W12 ... ... WEVT-10 WEVT-9 ... WEVT-2 WEVT-1 WEVT B15 1 0 0 0 0 0 0 0 0 0 0 0 Annexe 1 : ADC Read out input event format B14 1 P P P P P P P P P P P B13 B12 1 1 0 0 0 0 0 0 Gain Gain Gain Gain Gain Gain Gain Gain B11 1 F B10 B9 1 1 ADCID L B B8 1 B7 1 A B6 B5 1 1 PHASE BCID B4 1 B3 1 B2 B1 1 1 EVENTN B0 1 CELLN ADC channel 1 sample 1 ADC channel 2 sample 1 ADC channel 3 sample 1 ADC channel 4 sample 1 ADC channel 5 sample 1 ADC channel 6 sample 1 ADC channel 7 sample 1 ADC channel 8 sample 1 ... ... 0 0 P P 0 0 0 P P 0 0 0 F L B A 0 0 1 0 S 0 E 0 0 Gain Gain 0 0 CELLN ADC channel 1 last sample ... ADC channel 8 last sample SCAC status 0 0 0 0 0 0 0 W1 : frame start tag W2 & W3 : event header ADCID : The ADC IDentifier. PHASE : Bits encoding the phase of the 5MHz rclk at the time of the trigger. EVENTN : Event number. BCID : Bunch Counter IDentifier. W4 WEVT-2 : Sample data W4 : first sample header also called RADD F : First sample of event, send event header, and perform gain selection algorithm (if in auto gain mode). L : Last sample of an event, send event status, and delay further samples to make room for the event header of next event. B : Backporch bit. Do not raise the gain for any channel in auto-gain mode. A : Test mode bit. CELLN : The SCA cell (capacitor) number. From W5 to W12 : first sample data Gain : - 00 test data. - 01 low gain. - 10 medium gain. - 11 high gain. ADC : ADC data WEVT-10 : last sample header From WEVT-9 to WEVT-2 : last sample data The TMS320C6414 Processing Unit 08/03/2016 13/23 1 0 WEVT-1 : event trailer B11 & B0 : forced high. S : Single bit errors in EDC (Error Detection & Correction) unit. E : Double bit errors in EDC unit. SCA Controller status : B8 : SEU in the latency’s redundant MSB’s. B7 : done_fifo overflow. B6 : free_fifo Underrun The SCA run out of free cells. Invalid cell numbers were inserted into the sequence. B5 : Sequence error : The free_fifo emitted the same cell number twice in a row. B4 : Single bit error : a cell address was found with a single bit error. This error was corrected. B3 : Double bit error. A cell address was found with two bits in error. This bit will reoccur repeatedly, since the error will not be corrected. B2 : BCID reset. The BCID counter was reset. B1 : Init. Bit set in the first event after initialisation. WEVT : frame end tag For all words except the frame start/end tag B14 : odd parity on bit 0-13, 15. Note : the parity bit is set to 0 or 1 in order to always have an odd number of ones in the 16 bits word ; that way it is impossible to have a “frame end tag” in an event. 8.2 Annexe 2 : Schematics, routing and placement The TMS320C6414 Processing Unit 08/03/2016 14/23 The TMS320C6414 Processing Unit 08/03/2016 15/23 The TMS320C6414 Processing Unit 08/03/2016 16/23 The TMS320C6414 Processing Unit 08/03/2016 17/23 The TMS320C6414 Processing Unit 08/03/2016 18/23 The TMS320C6414 Processing Unit 08/03/2016 19/23 The TMS320C6414 Processing Unit 08/03/2016 20/23 The TMS320C6414 Processing Unit 08/03/2016 21/23 The TMS320C6414 Processing Unit 08/03/2016 22/23 The TMS320C6414 Processing Unit 08/03/2016 23/23