Accelerated DSP algorithm computation using FPGAs

advertisement

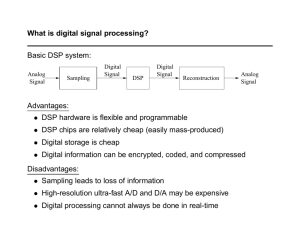

Accelerated Digital Signal Processing Algorithms for FPGA Design Sean Gallagher, Xilinx, Inc. Summary Ever-faster Analog-to-Digital Converters (ADCs) are pushing signal processing activities closer to the antenna, allowing designers to apply digital techniques to problems that were once handled purely in the Radio Frequency (RF) domain. As increasingly complex algorithms and sampling rates overwhelm the processing capabilities of the ubiquitous Digital Signal Processor (DSP), designers are forced to find ways of parallelizing their algorithms. Typically this means that algorithms must be partitioned across multiple DSPs, working in parallel. Free from the algorithmic constraints of inherently serial DSP Processors, Field Programmable Gate Arrays (FPGAs) are gaining wider use as DSP compute engines because they are better suited for the high-throughput demands of modern signal processing. In many cases an algorithm that would require many DSP processors can be implemented in a single FPGA, decreasing the overall system cost and power consumption. Commercially available FPGAs with as many as three hundred embedded multipliers, large re-configurable fabric, and on-chip RAM are well suited for a wide range of algorithmic functions. While it is possible to base DSP algorithms for FPGAs on DSP processor software, this approach typically fails to fully exploit FPGA architectural features and opportunities to parallellize algorithmic components. This paper explores the optimal implementation of a range of DSP functions such as quadrature down conversion, polyphase filtering, beam forming, and pulse compression radar using windowed FFTs. Novel approaches for decreasing implementation size, such as data formatting and clocking techniques, will be explored along with tools and methods for implementing DSP algorithms in FPGAs. Author Contact Information: Sean Gallagher, Xilinx Inc. and adjunct professor of DSP at Temple University, Philadelphia, PA. 215-990-4616 sean.gallagher@xilinx.com