Final_Project_report_ZLu_RFAddo

advertisement

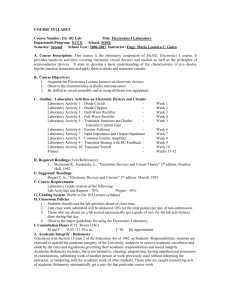

Sub-threshold leakage reduction in domino logic Zhiwen Lu and Robert F. Addo ECE 6332 – Fall 2010 University of Virginia <zl2a and rfa3ff>@virginia.edu ABSTRACT Reduction of leakage power consumption is one of the primary design considerations in contemporary CMOS design due to two reasons. One is the trend of process scaling of the modern technology has made sub-threshold leakage an increasingly large component of the total power dissipation. The other is that power and heating dissipation concern caused by the growing device density on a single chip. For example, the dynamic switching power in domino logic circuit is the currently dominant component of power consumption. However, due to the scaling trends in both dimension and supply voltage, the sub-threshold leakage is becoming a more and more important component in the overall power consumption. The purpose of this paper is to investigate ways of suppressing the sub-threshold leakage in domino logic. On the other hand, among the various dynamic logic circuits, domino logic stands out for its high performance in microprocessor due to its high speed and area characteristics. The application of lower threshold voltage enables the high speed operation of the domino circuit. However low V T degrades the noise immunity and increases the sub-threshold leakage power. On-chip noise becomes more and more severe when the scale of the technology goes down and the operation frequency goes up. This is also when the leakage current becomes more important due to the reasons listed in above. 1. INTRODUCTION In modern digital CMOS integrated circuit, the power consumption can be divided into three categories: short circuit, leakage, and dynamic switching power. Short circuit power refers to the power dissipated when both PMOS and NMOS devices are ‘on’ simultaneously and can be largely reduced by sophisticated chip design. Traditionally the dynamic switching power is the dominant component of power consumption and arises from the transient switching behavior of the nodes. The changing signal is realized by the charging and discharging of parasitic capacitance in the circuit and the switching power can be shown as below [1] Pd fCLK Ceff VDD 2 (1) where f CLK is the operating frequency, capacitance, C eff is the total effective VDD is the supply voltage. However, the current scaling trends have made the sub-threshold leakage power a major contributor of the total power consumption. The sub-threshold leakage current is given by: W I leakage I 0 e L VGS VT nVth (1 e VDS Vth ) (2) As the scales of the circuit descend; the heating issues and reduction of dynamic power requires lower supply voltage so to maintain a moderate speed of the circuit, lower threshold voltage transistors are used. As we can see in equation (2), the leakage current exponentially increases with the lowered threshold voltage. So the leakage current is a potential dominant power consumption component in the technology of the near future. Fig. 1 shows an ITRS roadmap for power consumption in the past decade and predicts the future trends. If the sub-threshold leakage is not suppressed by any techniques, it will overtake the dynamic power and becomes the most significant component in the total power consumption. As for the techniques to reduce leakage current, they range from the circuit level to architecture level. Available techniques include dual threshold voltage, sleep transistor, varying supply voltage; forward and reverse body bias combined with high and low V t and so on. [1] uses MTCMOS to reduce leakage by introducing a high Vt sleep transistor in series with the low Vt ones to create a virtual ground or Vdd. This however introduces more delay as the additional transistor is on the critical path. [2] Uses Leakage Proof Domino Logic where 2 NMOS and 1 PMOS transistors are added to reduce the leakage and Modified Leakage Proof Domino Logic which is similar to the former except an additional clock signal is needed. This will however introduce more energy and area overhead. This paper will focus on the circuit level. In this paper, we will explore the combination of the dual threshold voltage with 1 sleep transistor (off the critical) with varying supply voltage and temperature to lower leakage current. The purpose is to look for optimized modified dual threshold voltage domino logic by applying these techniques. 2. CIRCUIT IMPLEMENTATION To show some initial result of the techniques mentioned above, a 2 input AND domino logic gate was implemented (figure 2.). The shaded transistors are low Vt transistors. To compare the results, three other different circuits are also implemented. They are standard single Vt AND gate with sleep transistor (replace all the circled transistors with low Vt transistors), standard single Vt AND gate without sleep transistor (delete the sleep transistor in the previous version) and standard dual V t AND gate (delete the sleep transistor in the figure 2). According to re [1], the dual Vt can largely reduce the leakage current. However, during idle mode, when input AB=00, there exist a leakage path from dynamic node to ground through the AB transistor which are low Vt devices. So an additional sleep transistor which is a high Vt device capable of pulling the dynamic node down to ground is very necessary. Later specific simulation result will show the affect of sleep transistor in combination with the dual Vt logic gate. Fig4: Schematic diagram of dual Vt with sleep transistor domino implementation of the propagate signal of the 16 CLA Fig2: Schematic diagram of dual Vt with sleep transistor domino implementation of a 2 input AND gate. After the initial stage of the test bench, the circuit was updated to a 16 bit Kogge-Stone carry lookahead adder. Figures 3 to 7 show the basic diagram of the adder. We implemented the implemented the dot operator (the gray dot) and the creation of the P and G signal (the square). Fig5: Schematic diagram of dual Vt with sleep transistor domino implementation of the generate signal of the 16 CLA S0 S1 S2 S3 S4 S5 S6 S7 S8 S9 S10 S11S12 S13 S14S15 ….....……. ….....…. A0 A1 A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 A12 A13 A14 A15 B0 B1 B2 B3 B4 B5 B6 B7 B8 B9 B10B11B12 B13B14 B15 Figure 3. Schematic of diagram for Krogge-Stone 16-bit lookahead logarithmic adder . Fig6: Schematic diagram of dual Vt with sleep transistor domino implementation of the dot operator generate signal of the 16 CLA By introducing sleep transistors, the area overhead can also degrade the speed property of a circuit. To include the delay information of a circuit, current/power – delay – product is simulated. As shown in figure 9. the overall performance still gets improved by 4 times as compared to a standard low V t logic gate. 90 3 Current delay product in Idle Mode Delay (ps) 70 tPLH 60 tPHL 50 tP 2 10 40 1 30 10 20 Fig7: Schematic diagram of dual Vt with sleep transistor domino implementation of the dot operator propagate signal of the 16 CLA 10 0.8 1.1 2.5 STANDARD SINGLE VT STANDARD DUAL VT SINGLE VT (VTL) WITH DUAL VT WITH SLEEP (VTL) SLEEP TRANSISTOR TRANSISTOR Fig 8: leakage current for a 2 input domino AND logic for input signals AB = 00 while varying the VDD VT TR AN SI ST O R DU AL DU AL VT W IT H SL EE P ST AN DA RD (V TL ) VT VDD SL EE P W IT H SI NG LE (V TL ) VT SI NG LE 3.2 16 Bit Carry Lookahead Adder . Similarly the power consumption in a carry generation circuit of a 16 bit adder is also simulated. This time, both active and idle mode are considered, however, the energy needed to enter/exit a sleep mode is still not included. The power saved in dual Vt is 4 times compared to the low Vt circuit (figure 10.), which is much more significant than that in active mode. The simulation is done with a supply voltage of 1.1V. 10000 1000 100 Active Mode Idle Mode 10 1 Current (nA) 1000000 100000 10000 1000 100 10 1 0.1 10 Figure 9. Delay and current – delay – product of various circuits Power (µW) To evaluate the power reduction in the dual V t with sleep transistor, leakage current in the four circuits is compared in figure 8. As expected, the dual Vt with a sleep transistor cut off the most leakage path and yields the least amount of leakage current. One detail is that the technology applied here is 45nm technology, which only applies to low supply voltage. So the 2.5V supply voltage here is actually not appropriate. According to this result, supply voltage of 1.1 V shows moderate reduction in power and doesn’t sacrifice too much speed compared to 0.8 V. Power consumption in the active mode turns out to be bigger in the improved dual Vt circuit compared to the standard dual vt circuit while it is largely reduced during idle mode. In addition, the application of the sleep transistor adds extra power consumption which enables the circuit to enter and leave the sleep mode. This energy overhead is small compared to the energy savings if the circuit should remain in idle mode for a long time. Thus the total power consumption gets reduced after the number of the total cycles the circuit goes through reaches a certain value. That is when the power saved during the idle mode finally compensates the energy needed to enter/exit the sleep mode. [3] TR AN SI ST O R 0 0 ST AN DA RD 3. RESULT AND ANALYSIS OF SIMULATION 3.1 2 - Input AND Gate Current Delay Product (n-ps) 10 80 STANDARD STANDARD DUAL VT SINGLE VT DUAL VT WITH SLEEP (VTL) TRANSISTOR Figure 10. Power consumption in 16bit adder comparison In 16 bit adder, the delay degradation is more severe as show in . figure 11. However the power –delay – production still gets reduced in idle mode in the dual Vt with sleep transistor. 2.9 0.6 Delay (ns) tPLH 0.5 tPHL 0.4 tP 2.8 2.7 0.3 2.6 0.2 2.5 0.1 2.4 Power delay product (W-ns) 3.0 Power delay product 0.7 VT DU AL (V TL ) W IT H SL EE P ST AN DA RD VT SI NG LE ST AN DA RD TR AN SI ST O R 0.0 DU AL VT Figure 12. Power consumption versus the parameter – Vth0 Figure 11. Delay and current – delay – product in idle mode of a 16 bit adder with various techniques . To investigate the trade off between the power and delay caused by tuning the threshold voltage, a series of varying V t is applied to the adder. The high and low . Vt are defined in Table 1. By increasing both the value of high and low V t, the drop in the power consumption is significant in all the circuits as shown in figure 12. However, as for the dual Vt with sleep transistor, the power reduction is moderate when No. Vth0=2. Further increment in Vt may cause serious degradation in speed. Future work can be done to optimize the power – delay – product by tuning the value of the threshold voltages. Temperature dependence of the techniques is also considered. Figure 13. shows that dual Vt with sleep transistor also successfully mitigates the degradation caused by heating effect. Table1. Definition of Vth0 and the corresponding power consumption STAND- STANDARD VT (VTL) Vth0 ARD DUAL VT DUAL VT WITH SLEEP TRANSISTOR NO. PMOS PMOS NMOS NMOS POWER POWER POWER Vth0 VTL VTH VTL VTH (µW) (µW) (µW) 1 -0.20 -0.40 0.20 0.40 283.60 72.65 59.4 2 -0.30 -0.50 0.32 0.60 15.34 4.703 3.9 3 -0.35 -0.65 0.35 0.65 4.93 1.27 1.04 4 -0.40 -0.70 0.40 0.70 1.37 0.36 0.28 5 -0.45 -0.75 0.45 0.75 0.44 0.31 0.10 6 -0.50 -0.80 0.50 0.80 0.21 0.06 Figure 13. idle mode power consumption of a 16 bit adder with while varying the temperature. 4. CONCLUSION . The sub-threshold leakage current reduction is investigated by looking into two circuits – 2 input AND gate and 16 bit domino adder. Both result shows that dual V t with sleep transistor suppress the leakage current the most without considering energy overhead caused by entering/exiting sleep mode. Power – delay – product is considered to optimize the trade off between power and delay. By introducing a parameter – Vth0, a specific value of high and low Vt have been found through simulation. Temperature dependence also supports the dual V t with sleep transistor as the most reliable technique to reduce the sub-threshold leakage in the 16 bit adder. 5. REFERENCES [1] James T. Kao and Anantha P. Chandrakasan, ‘Dual-threshold voltage techniques for low-power digital circuits’, IEEE journal of solid-state circuits’, VOL. 35, NO. 7, July 2000. [2] Salendra. Govindarajulu and T. Jayachandra Prasad, ‘Design of low power, high speed, dual threshold voltage CMOS domino logic circuits with PVT Variations’, International Journal of Electronic Engineer Research, Volume 2 Number 5, 2010 [3] Volkan Kursun, Eby G. Friedman, ‘Multi-voltage CMOS Circuit Design’, John Wiley & Sons Ltd, 2006.