timing

advertisement

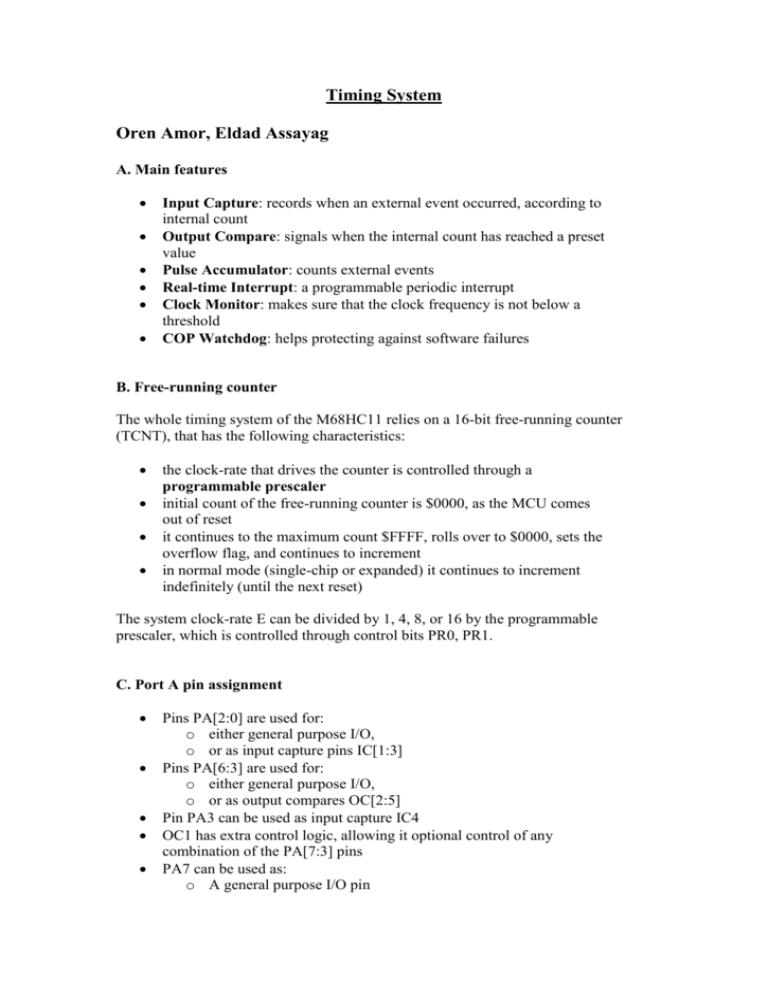

Timing System Oren Amor, Eldad Assayag A. Main features Input Capture: records when an external event occurred, according to internal count Output Compare: signals when the internal count has reached a preset value Pulse Accumulator: counts external events Real-time Interrupt: a programmable periodic interrupt Clock Monitor: makes sure that the clock frequency is not below a threshold COP Watchdog: helps protecting against software failures B. Free-running counter The whole timing system of the M68HC11 relies on a 16-bit free-running counter (TCNT), that has the following characteristics: the clock-rate that drives the counter is controlled through a programmable prescaler initial count of the free-running counter is $0000, as the MCU comes out of reset it continues to the maximum count $FFFF, rolls over to $0000, sets the overflow flag, and continues to increment in normal mode (single-chip or expanded) it continues to increment indefinitely (until the next reset) The system clock-rate E can be divided by 1, 4, 8, or 16 by the programmable prescaler, which is controlled through control bits PR0, PR1. C. Port A pin assignment Pins PA[2:0] are used for: o either general purpose I/O, o or as input capture pins IC[1:3] Pins PA[6:3] are used for: o either general purpose I/O, o or as output compares OC[2:5] Pin PA3 can be used as input capture IC4 OC1 has extra control logic, allowing it optional control of any combination of the PA[7:3] pins PA7 can be used as: o A general purpose I/O pin o An input to the pulse accumulator (PAI) o OC1 output pin D. Input Capture Function: The input capture function records the time an external event occurs by latching the value of the free-running counter when a selected edge is detected at the associated timer input pin. Synchronization: An asynchronous input capture edge is synchronized to an internal clock (PH2), so that the latching occurs on the opposite half cycle of PH2 from when the timer counter is being incremented. This synchronization causes a delay. Timer Control Register 2 (TCTL2): The control bits of this register are used to program input capture functions to detect a particular edge polarity on the corresponding timer input pin: o Rising edge o Falling edge o Any edge (rising or falling) The input capture functions operate independently of each other Timer Input Capture Registers (TICx): Each input capture function has its own timer input capture register. The registers are named TIC1, TIC2, and TIC3 Timer Input Capture 4/Output Compare 5 Register (TI4/O5): The TI4/O5 Register is used either as an input capture register, or as an output compare register The I4/O5 bit in the pulse accumulator control register (PACTL) is used to determine the function of PA3 as IC4 or as OC5 E. Output Compare: Function: The output compare function is used to program an action to occur at a specific time Each one of the output compare functions has a separate 16-bit compare register, and a dedicated 16-bit comparator The value in the compare register is compared to the value of the free running counter on every bus-cycle When the compare register matches the counter value, an output compare status flag is set. This function can be used to generate an output signal of a specific frequency and duty cycle, at the resolution of the free-running counter Timer Output Compare Registers (TOCx): TOC1-TOC4 and TI4/O5 are 16-bit read-write registers, initialized to $FFFF If an OC register matches the free-running counter TCNT, the corresponding output compare flag is set in timer interrupt flag register 1 (TFLG1) If that particular interrupt is enabled in the timer interrupt mask 1 (TMSK1) an interrupt is generated In addition to an interrupt, a specified action can be initiated at one or more timer output pins For OC[5:2], the pin action is controlled by pairs of bits (OMx and OLx) in the TCTL1 register The OC1 output action taken when a match is found is controlled by to 8-bit registers OC1M (OC1 Mask Register) and OC1D (OC1 Data Register), which specify which port A pins are to be used, and what data is placed on these port pins, respectively Timer Compare Force Register (CFORC): The CFORC register allows forced early compares. FOC [1:5] bits correspond to the five output compares. Forcing an output compare results in an action (as if there were a match), but the interrupt status flag bit is not set. CFORC bits should not be used on an output compare function that is programmed to toggle its output on a successful compare. Timer Control Register 1 (TCTL1): The bits of this register specify the action taken as a result of a successful Ocx compare: o Disconnected o Toggle output line o Clear output line to 0 o Set output line to 1 Timer Interrupt Mask Register 1 (TMSK1): this 8-bit register is used to enable or inhibit the timer input capture and output compare interrupts Timer Interrupt Flag 1 (TFLG1): Bits in this register indicate when timer system events have occurred. Coupled with the bits of TMSK1, the bits of TFLG1 allow the timer subsystem to operate in either a polled or interrupt driven system. Timer Interrupt Mask 2 Register (TMSK2): This 8-bit register is used to enable or inhibit timer overflow and realtime interrupts The timer prescaler control bits are included in this register Timer Interrupt Flag 2 Register (TFLG2): Bits in this register indicate when certain timer system events have occurred. F. Real-time Interrupt Function: The real-time interrupt (RTI) feature is used to generate hardware interrupts at a fixed periodic rate It is controlled and configured by two bits (RTR1 and RTR0) in the pulse accumulator control (PACTL) register The RTII bit in the TMSK2 register enables the interrupt capability Every timeout causes the RTIF bit in TFLG2 to be set If RTII is set, an interrupt request is generated G. Computer Operating Properly Watchdog Function The MCU includes a COP system to help protect against software failures When the COP is enabled, the software is responsible for keeping a free-running watchdog timer from timing out. If the watchdog timer times out, a system reset is initiated. The NOCOP bit in the CONFIG register determines whether the COP system is enabled or disabled The COP timer rate control bits CR[1:0] in the OPTION register determine the COP timeout period. In normal operating mode, these bits can be written within 64 bus cycles after reset. Writing $55 to the COPRST register arms the COP timer. Writing $AA to the COPRST register clears the COP timer. H. XOUT Pin Control Function: The XOUT pin is used when the MCU is driving the clock input of another processor (in order to synchronize external devices with the MCU) This pin outputs the CLKX signal. The CLKX bit in the CONFIG register controls whether this clock is on or off The CLKX signal, when enabled, is a buffered XTAL signal, and is four times the frequency of the E-clock. The frequency of the clock that is driven out the XOUT pin is controlled by the XDV[1:0] bits in the OPT2 register. These bits determine the scaling factor (1, 4, 6, or 8) I. Pulse Accumulator Function: An 8-bit counter that can be configured to operate o Either as a simple event counter o Or as a gated time accumulation The PAMOD in the PACTL register determines the operation mode of the pulse accumulator In the event counting mode, the 8-bit counter is clocked to increasing values by an external pin. The maximum event rate is E-clock/2. In gated time accumulation mode, a free-running E-clock/64 signal drives the 8-bit counter, but only while the external PAI (port A pin 7) is activated. Pulse Accumulator Control Register (PACTL): The PAMOD bit selects the pulse accumulator’s operating mode (event counter or gated timer) The PEDGE bit selects o Rising or falling edge increments counter, in event counting mode o Zero or one on PAI inhibits counting, in gated time accumulation mode The PAEN enables or disables the pulse accumulator system Pulse Accumulator Count Register (PACNT): An 8-bit read/write register Readable even if PAI is not active in gated time accumulation mode Not affected by reset Synchronized to the internal PH2 clock Pulse Accumulator Status and Interrupt Bits: Bits in TFLG2: o PAOVF – status bit that is set each time the pulse accumulator count rolls over from $FF to $00. o PAOVI – control bit that enables or disables the pulse accumulator overflow interrupt (interrupt driven or polled), and does not affect the state of PAOVF. o When the PAOVI control bit is set, a hardware interrupt request is generated each time PAOVF is set. o Before leaving the interrupt service routine, software must clear PAOVF by writing the TFLG2 register Bits in TMSK2: o PAIF – status bit that is automatically set each time a selected edge is detected at the PA7/PAI/OC1 pin. o PAII – control bit that enables or disables the pulse accumulator edge detect interrupt (interrupt driven or polled), and does not affect the state of PAIF. o When the PAII control bit is set, a hardware interrupt request is generated each time PAIF is set. o Before leaving the interrupt service routine, software must clear PAIF by writing the TFLG2 register