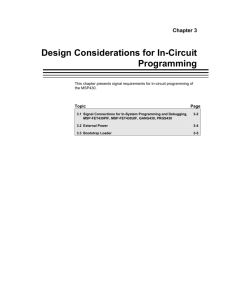

Embedded System Vulnerabilities

advertisement