The G8ACE version of the CT1DMK PLL using a CPLD Oct2005

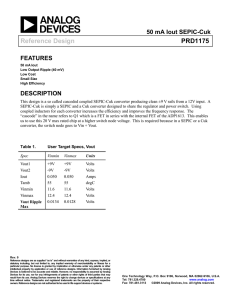

advertisement

The G8ACE version of the CT1DMK PLL using a CPLD (Complex Programmable Logic device) Version with input mmic. This design is an adaptation of the PLL design by Luis Cupido CT1DMK and originally published in Dubus Magazine 3/2002 and also available as a pdf download. http://gref.cfn.ist.utl.pt/cupido/reflock.html With the availability of GPS locked 10 MHz reference sources this unit provides an almost universal solution to locking Microwave local oscillator sources. It may itself be used to lock a 10 MHz Reference to a GPS module using the 1pps or 10KHz signal. The PLL is shown to the right in a tin plate box 55 x 55 x 25mm deep. Either two or three sma connectors are required depending on the configuration. Used with a ‘brick’ oscillator where a monitor output is available from the oscillator only two sma are required. RF in and Reference in. Otherwise the RF signal must loop thro via the third socket to the following microwave multiplier chain. Top right is the 44 pin CPLD with program and lock type selection jumpers. Top left is the 3.3v regulator and toward the CPLD the 04 input signal squarer. Programming of the CPLD is accomplished via the 10 pin connector in the centre of the PCB. Lower right is an op amp which supplies the correction voltage to the oscillator varicaps and will also drive a meter to provide lock centring information. This particular PLL is the most basic. The PCB will support additional features some of which still need to be tested and All but two components are placed on the top side of the PCB. Terminations are placed on the lower side and are optional depending how the inputs are wired. eg. the RF termination is not used with loop through. The 44pin CPLD is soldered onto the PCB first. It may appear a daunting task due to the tiny spacing of the lead outs however the use of solder wick will mop up any solder bridging the connections. Place the CPLD on the board and observe static precautions in the construction from this point. Double check the orientation of the chip. There is one corner on the CPLD with a chamfer adjacent to Pin 1 not on all corners as the CAD drawing above shows it and this chamfer should be placed upper left. The PCB also has a white spot near Pin 1. Use a sprung wooden clothes peg to hold down the CPLD making sure both x and y pin alignments are correct onto the pads before soldering. Be sparing with solder although the solder wick will remove it. The less solder used the better. Inspect the pins carefully after soldering and cleaning for good joints. The centre programming socket and the programming pins are best left until after the PCB is soldered into the box. As these are tall they may obstruct soldering the smaller parts. Otherwise the only ordered construction should be the top right corner. Fit the regulator first then the 4u7 capacitors followed by the 56 ohms. The clothes peg technique may also be useful to hold the LCX04 IC for soldering. CH2 is an RF suppressor of 200mA rating and 70 ohms impedance. If a GPS 1pps TTL input is used for the reference then C18 (connecting to the LCX04) is also replaced with a 0 ohm link. The CPLD although a 3.3v device is 5v tolerant for TTL interfacing. R21 (51 ohms) is not used for either 10 KHz or 1PPS TTL inputs. This version is for use with 10 MHz reference. The 10 KHz & 1pps version requires some component value changes. Note the value of R13 shown on the circuit diagram is incorrect, use 15K. The rear side of the PCB shows the sma connection pads. Three on the right hand edge, Out 1, Out 2 and Ref. Note these pads are duplicated and connected via pth holes on the PCB topside. These pads should align with the centre pins of the sma connectors mounted on the box side. Out 1 and 2 require a wire link for the RF loop through. R15 and R21, 51 ohms, are installed as required. The 12v supply is wired to the top right Pad marked +12v. The output to the oscillator varicaps is from the second from bottom pad marked Tune 2. As with the sma pads these connection pads are duplicated on the PCB topside via pth holes. Feed through capacitors are used through the box side for the 12v supply and varicap tuning connections. External varicap tuning wiring should also be via screened cable. The connectors should be positioned centrally in the height of the box side wall so that the sockets do not interfere with the lids. 4-5mm is required on each sidewall edge for the lid flange to clip on. Two hole sma sockets are required, these can be fabricated from 4 hole types by cutting off the diagonally opposite mounting holes. The PCB is soldered into the box. A strip around the edge of the PCB underside is free from solder resist for this purpose. Note also when marking and drilling the box side wall that a cut out is provided on the PCB to cater for the tin plate box corner overlap. Check for correct orientation of these when marking out. When the programming connector is fitted to the top side of the PCB the indexing cut out should face the CPLD. Its pins are soldered on the PCB under side as are the programming jumper pins. Parts list for the Phase Locked Loop Comp. Ref. R11 R23 R32 R15 R21 R4 R7 R14 R1 R24 R25 R27 R28 R34 R35 R37 R41 R42 R26 R33 R40 R13 R16 R17 R19 R22 R36 R10 R12 L1 CH2 IC1 IC2 IC3 IC4 Value 0 Link 0 Link 0 Link 51 See note 51 56 220 820 4K7 4K7 4K7 4K7 4K7 4K7 4K7 4K7 4K7 5K6 10K 10K 10K 15K 100K 100K 100K 100K 100K 110K 110K 1.8h See note 70 Suppressor 3.3v Regulator EPM3064-44-4 74LCX04D LM358 or LM2904 Package Size 0805 0805 0805 0805 0805 1812 1206 0805 0805 0805 0805 0805 0805 0805 0805 0805 0805 0805 0805 0805 0805 0805 0805 0805 0805 0805 0805 0805 0805 0805 1210 Dpak 44 pin SO14 Marking SO08 358 or 2904 1 000 000 000 510 510 560 221 821 472 472 472 472 472 472 472 472 472 562 103 103 103 153 104 or 1003 104 or 1003 104 or 1003 104 or 1003 104 or 1003 114 or 1103 114 or 1103 1R8 Yellow LM1117DT CPLD LCX04 Qty 3 2 1 1 1 9 1 3 1 1 5 2 1 1 1 1 1 IC5 MAR8-ASM Mmic ASM 1 D1 CD BAV99 Useful files SOT23 A7 1 1 Comp. Ref. C15 C14 C16 C17 C9 C10 C11 C12 C13 C18 C21 C4 C23 C24 C3 C7 C8 C-add Value Jumper Handbag 6 pin link Connector 10pin Plug 10pin Plug Pins 10pin For Feedthros 1500p Box 1200p 1200p 2200p 2200p 10nF 10nF 10nF 10nF 10nF 10nF 10nF 100nF 100nF 100nF 4u7 4u7 4u7 1uF Package Size 0805 0805 0805 0805 0805 0805 0805 0805 0805 0805 0805 0805 0805 0805 Elect Elect Elect 0805 Marking Clear/red 2 Red/red/red 2 Clear 7 Brown/green 3 Black is -ve Black is -ve Black is -ve Blue 3 1 2 x 3 Pins 2 4 Connector 1 Ribbon Connector 1 Wires above Connector 1 10 2 55x55x25mm PCB SMA Connectors Qty 1 1 Not supplied 3 When the PLL is used for locking a 10 MHz OCXO with the 10 KHz signal use C24 100nF in the C21 position and discard C21. Use the additional capacitor C-add 1uF for C24. Note the 100K and 110K resistors may use the four digit marking code. A plug is are supplied for the programming connector, a ribbon cable type which is polarised like the PCB socket. SMA connectors are not supplied other connectors may be substituted if required which fit the box size constraints. Programming the CDLD A CD is supplied which contains a copy of MAX+PlusII programmer only software. Additionally .pof files are required which contain the necessary programming information for the CPLD. The CPLD have various speeds and numbers of gates. The EPM 3064-4 supplied in the kit is a fast device with more gates. You must read the text file (list.txt) which accompanies the .pof files CT1DMK has written to select the correct file for both the correct CPLD device and for the correct application and operation. An interface is required between the PC and the PLL programming connector. The ByteblasterMV is a straight forward circuit and is shown below. Construct using the 74HC244 as this will operate satisfactorily from the 3.3v supply available via the programming connector. This programmer uses the PC printer port. The 10 pin plug connections are wired one to one with the PLL programming connector. Altera Stand-Alone Programmer 10.22 Installation Instructions Begin installation by executing the ASAP2_1022.exe file, i.e., type the following command at a DOS or command prompt: <drive letter><path>ASAP2_1022 or Double-click the file name in the Windows Explorer (Windows 95, 98, 2000) or Windows NT Explorer (Windows NT 4.0). The MAX+PLUS II installation wizard is unpacked and launches. In the Welcome page, click Next. After reading the license agreement, click Yes. Enter your name and company in the User Information page and click Next. Choose the items you wish to install in the Select Components page. By default, the ASAP2 software, online help, and readme files are selected for installation. Specify a destination directory for the MAX+PLUS II Programmer Only software installation. The installation program specifies the c:\maxplus2 directory by default. If you have a previous installation of MAX+PLUS II software, Altera recommends that you install the ASAP2 version 10.22 software into another directory. You can click on the Browse button to create or search for a directory (click OK to save your choice). Click Next when you are finished. Select a program folder in which the installation program will add program icons. Click Next and installation will begin. When installation is complete, you will be returned to your desktop. You can view the MAX+PLUS II 10.2 ReadMe file by selecting it from the MAX+PLUS II 10.2 Programmer Only menu in the Start menu. It should be possible to go to obtain a license directly from this page: http://www.altera.com/support/licensing/lic-index.html Go to the very bottom of the web page where its says: MAX+PLUS II software for students & universities The program will run and program the CPLD without a license if you simply ignore all the messages and proceed until you see the red bar in the programming window which indicates programming taking place. This method however may not function reliably on your PC and OS so a license is recommended. On first running the program select the tab MAX+PlusII and select programmer. A window should popup so that you can tell it the programmer type you are using. Scroll down the list to Byteblaster II and select along with your printer port. (LPT1). If you cannot get this setup then choose the Options tab followed by Hardware setup. Now with the programming window open select the File tab and select Programming file. You should have previously read the text file in the CT1DMK pof zip file and saved all the pof files to a directory. Point now to this directory and select the file: ref_e1_64_4.pof which should appear in the programmer window. Power the PLL module from a 12v supply. Current drawn should be approximately 60ma. Click on the program button and the red bar should traverse the bottom of the window as the programming takes place. Any persistent error message such as unrecognised or socket empty may mean the CPLD requires further soldering inspection and troubleshooting. It is highly recommended to start with this pof file as it simplifies verification of proper operation of the PLL. Once familiarised with programming and knowing that the construction and operation of the PLL is proven then other .pof files can be tried such as the Universal Lock. Some component changes particularly to the integrator might be necessary, refer to the original CT1DMK articles for the required values. Quartus software is the current version from Altera. Testing for correct operation of the PLL The selected .pof file has configurations for the most commonly used crystal. That part of the pof text file (named list) which lists these configurations is shown below. Classical version european list of frequencies: conf=000 xtal=96.000 MHz for 1296MHz >> 144 MHz conf=001 xtal=90.000 MHz for 2304GHz >> 144 MHz conf=010 xtal=90.667 MHz for 2320GHz >> 144 MHz conf=011 xtal=117.000 MHz for 5760GHz >> 144 MHZ conf=100 xtal=106.500 MHz for 10GHz >> 144 MHz conf=101 xtal=125.250 MHz for 24GHz >> 144 MHz conf=110 xtal=122.250 MHz for 47GHz >> 144 MHz conf=111 xtal=100.0 MHz for secondary 100MHz standard. Referring to the initial graphic at the beginning of this article, the jumper links are shown set to conf 100 (106.5 MHz) and the second single jumper to XOR comparator output. A simple method to confirm operation if you have an Adret is to run open loop. First connect the 10MHz reference signal to Ref in and observe with an oscilloscope at the XOR selection jumper. A square wave should be seen. Apply the 106.5MHz signal to RF in and the frequency should double. The mark space ratio will possibly be very asymmetric. Breaking RF in and reconnecting will undoubtedly bring it up in a different relationship. Change the Adret frequency by 1 KHz and the mark/space ratio of the comparator waveform will sweep at around one sweep every two seconds. This demonstrates a clear unlock state. Reduce the error in the 106.5 frequency and the sweep rate will slow down. It will appear stationary if your 106.5 is accurate at 106.5 In reality of course unless your Adret is also locked given time the mark space ratio of the waveform will change, the rate depending on the frequency error. Change the conf jumpers to another crystal frequency in the table and set the Adret to it to confirm an understanding of the jumper selection. The dc varicap output of the PLL can be set to 0-5 or 0-10v by exchanging the resistors R33 and R42 10K and 5K6. Select these resistors as appropriate for the oscillator to be disciplined by the PLL. The MKII OCXO preffered control range is 0-10v. Once familiar with the operation then connect to an Oscillator and operate closed loop. If you are without an Adret then detune the oscillator to observe the waveforms discussed above. Setting the waveform to 50:50 duty cycle (1/2 the control voltage range) will be near the centre of the lock control range dependent on the linearity of the varicaps in the oscillator. The PLL used for locking a 10 MHz OCXO with a GPS 10 KHz signal will lock quite slowly. (Using the pof file mwref_g6gxk_3064-4.pof) Monitoring the CPLD comparator output signal with an oscilloscope will show a gradual shift in the mark space ratio as lock is achieved. Monitoring the varicap volts will show the result of the changing mark space in the comparator waveform. This voltage may take several seconds to change even by 1mV as the PLL gets closer to lock. The CD contains numerous files which will assist in the construction. G8ACE Issue 2 13 october 2005. Notes/changes. Latest CT1DMK .pof programming files July 2005 The programming software may only operate once in some circumstances. Close and re-open if this is the case to do for example a verify operation.