Input and Output

advertisement

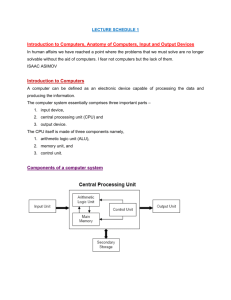

INPUT AND OUTPUT Why not connect peripherals directly to system bus? Wide variety of device operation Much slower data transfer rate Wide varieties of data format and word lengths Major functions of an I/O Module Interface to CPU and memory via system bus or central switch Interface to one or more peripheral devices by custom data links 6.1 EXTERNAL DEVICES I/O Module Address lines Data lines Control lines I/O Module Page 1 6.2 EXTERNAL DEVICES Categories of external devices Human readable: (Humans) VDT Machine readable: (Equipment) Magnetic disk/tape, Sensors, Actuators Communication: (Remote devices) Modem, Network interface 6.2.1 KEYBOARD/MONITOR ASCII: 7, 8 bits (Table pp181) Format Control: BS, HT, VT, LF, FF, CR Transmission control: SOH, STX, ETX, EOT, ACK, NAK, SYN,... Miscellaneous: NUL, BEL, SO, SI, DEL, SP, DC1, DC2, DC3, ESC, … 6.2.2 DISK DRIVE Data exchange Control signals Status signals Control from I/O module, Status to I/O module Control Logic Data bits to/from I/O module Buffer Transducer Data to/from environment Page 2 6.3 I/O MODULES 6.3.1 FIVE CATEGORIES OF MODULE FUNCTION Control and Timing CPU Communication Device Communication Data Buffering Error Detection Example: Transfer of data from CPU to external device 1. CPU interrogates I/O module, checks status of attached I/O device 2. I/O module returns device status 3. If ready and operational, CPU requests data transfer 4. CPU receives grant signal from I/O module 5. CPU transfers data. I/O module sends received (ACK) signal Data Rate (bps) Keyboard Mouse Modem 101 – 102 – 103 – Laser Ethernet Hard Fast Graphics Gigabit Printer Disk Ethernet Display Ethernet 104 – 105 – 106 – 107 – 108 – 109 Page 3 Three I/O techniques: Programmed I/O: CPU controls I/O module, waits until I/O is complete Interrupt-driven I/O: CPU issues command,, continues with other instructions Direct memory access: Direct exchange between I/O module and memory 6.4 PROGRAMMED I/O 1. CPU encounters an instruction in program, issues a command to I/O module 2. I/O Module performs action, sets status bits in I/O status register 3. No interrupts, CPU checks periodically Four types of I/O commands: Control - activates peripheral Test - checks various status conditions of I/O module Read - I/O module obtains data from peripheral, places it in buffer Write - I/O module transmits data from data bus to peripheral Usually, each I/O device has a unique identifier or address/es. Memory Mapped I/O: Single address space for memory and I/O devices. CPU treats status registers and data registers like memory locations. So, a single read, single write command needed. Isolated I/O: Separate I/O read/write and memory r/w lines thus, I/O address space is isolated from memory address space. Different CPU commands for I/O and memory access. Page 4 6.5 INTERRUPT-DRIVEN I/O Programmed I/O "ties up" the CPU and CPU must interrogate I/O module repeatedly. Interrupt I/O is more efficient Interrupt Processing 1. I/O device issues interrupt signal to CPU. 2. CPU tests for interrupts at end of cycle, sends ACKnowledgement signal to I/O device, and device removes interrupt signal 3. CPU saves current processor status and other info (registers, etc) on system control stack, loads interrupt handler program and executes it 4. When done, saved values (processor status) are re-instated Categories of multiple interrupt handling Multiple interrupt lines Software poll Daisy chain (hardware poll, vectored interrupts) Bus arbitration Page 5 6.6 DIRECT MEMORY ACCESS Disadvantages of Programmed and Interrupt-Driven I/O Both require CPU intervention (management) for data transfer Data is transferred "through" the CPU I/O transfer rate limited by CPU speed of testing and servicing a device DMA Function Requires a DMA module. CPU issues r/w command to DMA with following information. Whether read(r) or write(w) is requested Address of I/O device Starting location of memory to read from or write to Number of words to be written CPU then continues with "other work", while DMA transfers entire block of data directly to memory. DMA signals completion of task Cycle-stealing: CPU temporarily suspends its control of the bus (pauses while DMA occurs) Various DMA mechanism configurations are possible (pp201) Page 6 6.7 I/O CHANNELS AND PROCESSORS Evolution of the I/O function CPU directly controls peripheral device I/O module (controller) added - Programmed I/O Interrupt-driven I/O DMA I/O Module becomes a dedicated processor in its own right I/O Module has a local memory, controls a large set of I/O devices 6.7.1 I/O CHANNELS Can execute I/O instructions CPU issues instruction to I/O channel, which manages entire data transfer Selector channels control one of many high-speed devices. Sets of devices grouped under a controller Multiplexor channel handles many low-speed devices "simultaneously" Page 7 6.8 EXTERNAL INTERFACE Parallel interface: Multiple lines connecting I/O module and peripheral, multiple bits transferred simultaneously Serial interface: One line, bits transferred one at a time Write operation: 1. I/O module sends control signal requesting permission to send data 2. Peripheral acknowledges request 3. I/O module transfers data (one word or one block) 4. Peripheral acknowledges receipt of data 6.8.1 SCSI INTERFACE Devices daisy chained, one end hooked to host. SCSI-2 (Wide SCSI) Exchanges between initiator and target Signals and Phases: Bus Free, Arbitration, Selection, Reselection, Command, Data, Status Page 8