First_Question_List_Solutions

advertisement

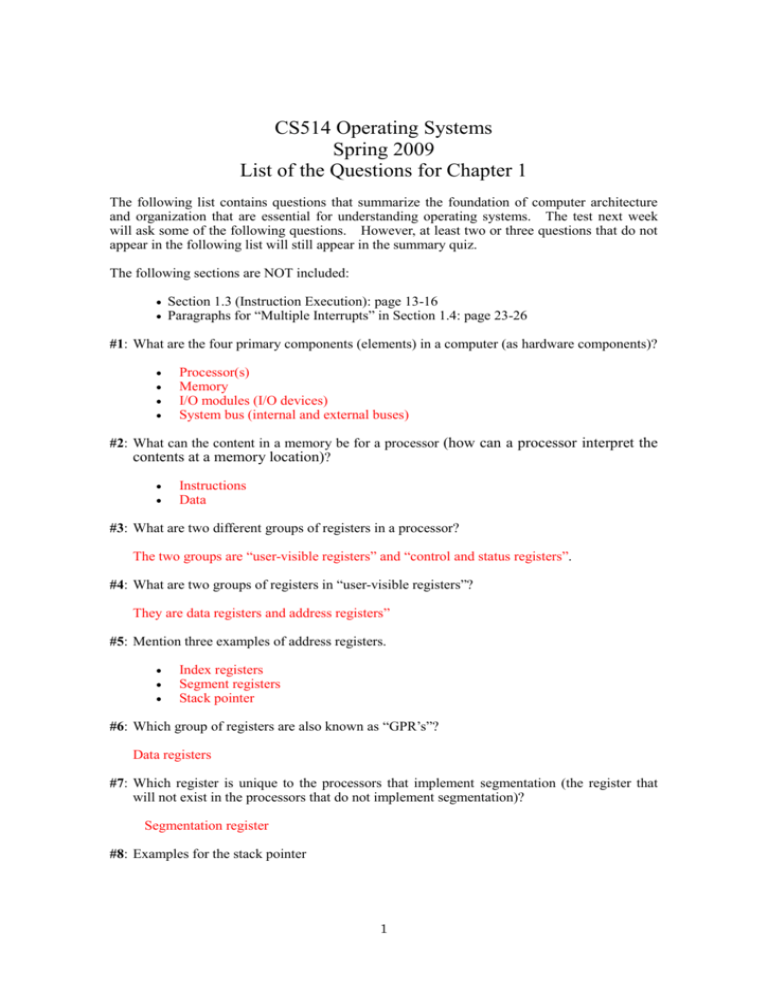

CS514 Operating Systems Spring 2009 List of the Questions for Chapter 1 The following list contains questions that summarize the foundation of computer architecture and organization that are essential for understanding operating systems. The test next week will ask some of the following questions. However, at least two or three questions that do not appear in the following list will still appear in the summary quiz. The following sections are NOT included: Section 1.3 (Instruction Execution): page 13-16 Paragraphs for “Multiple Interrupts” in Section 1.4: page 23-26 #1: What are the four primary components (elements) in a computer (as hardware components)? Processor(s) Memory I/O modules (I/O devices) System bus (internal and external buses) #2: What can the content in a memory be for a processor (how can a processor interpret the contents at a memory location)? Instructions Data #3: What are two different groups of registers in a processor? The two groups are “user-visible registers” and “control and status registers”. #4: What are two groups of registers in “user-visible registers”? They are data registers and address registers” #5: Mention three examples of address registers. Index registers Segment registers Stack pointer #6: Which group of registers are also known as “GPR’s”? Data registers #7: Which register is unique to the processors that implement segmentation (the register that will not exist in the processors that do not implement segmentation)? Segmentation register #8: Examples for the stack pointer 1 #9: Mention three examples of the control and status register. PC (Program Counter) IP (Instruction Register) Flag (Status) Register #10: Mention at least two flags in the flag (status) register. For each of the two flags you mentioned, briefly explain how it is used in assembly programs. Z (zero) flag: set to “1” when the result of an operation becomes zero. Used for controlling loops OF (overflow) flag: set to “1” when the results of an arithmetic operation caused an overflow. Used to compensate for the error caused by a mathematical overflow #11: Which flag in the flag (status) register is used to terminate a loop structure with a certain number of iterations? Zero flag #12: Briefly (within 40 words, using your words) explain why interrupt can improve efficiency? Without interrupt, a processor must wait for I/O operations to be completed. For slow I/O devices, the response time is long. Using interrupt, a processor can execute other instructions while an I/O device is in process. #13: Is the following statement TRUE or FALSE? “Interrupt can interrupt a processor while it is in the middle of executing an instruction”. FALSE: Interrupt can NOT interrupt a processor while one is executing an instruction. A processor can be interrupted after whichever instruction currently executed, but before the next instruction is executed. #14: What is “interrupt handler”? Interrupt handler is the software that handles interrupt signals to each I/O device. The interrupt handler is called by the operating system whenever an interrupt occurs to a particular I/O device (e.g., the interrupt handler for keyboard, NIC, floppy disk, hard disk, and etc.). Since each I/O device is a different hardware, dedicated handler is needed for each type. #15: What contains an interrupt handler (select the most appropriate option from the list below)? (a) User application program (b) Operating system bug patches (c) Device driver (d) User application updates (e) None of the above (f) All of (a) through (d) Solution: (c) 2 Each interrupt handler is a collection of procedures that tell a processor how to handle I/O events that occur in each particular I/O devices. Thus it is device-dependent. Any codes that must handle device-dependent operations are usually provided by device drivers (that’s why you need to install a device driver for each new I/O device you add to your PC). #16: As a part of interrupt handling, on an interrupt a processor switches from a currently executed process to an interrupt handler and the contents of the registers will be saved. How is this sequence of activities called? Context switching #17: What are the three primary performance metrics for memory? Access time (access latency, memory response time) Capacity Cost (price per byte) #18: What are the typical trade-off problems in memory subsystem in computers? Capacity vs. access latency Access latency vs. cost #19: What is “memory hierarchy”? Memory hierarchy means that a computer system combines different storage in layers, staring from the fastest (which are usually the processor’s internal registers) to the slowest (usually hard disks) so that the fastest is used first and the slowest the last. #20: Why is the memory subsystems for most of the computer systems is designed using memory hierarchy? Because the fastest memory unit is the most expensive (in terms of byte-cost) while the slowest is the cheapest. #21: What is “locality of references” in memory? “Locality memory reference” means the tendencies that: The contents of memory addresses that are located nearby (usually in consecutive addresses) will be accessed (used, referenced) by your computer (locality in “space”). Those memory addresses will be repeatedly accessed (used) in relatively short time only (locality in “time”). #22: Why is “locality of references” an important concept? By finding the size of memory that is in the locality of references, we can identify the amount of memory that maximizes the cost-performance (the minimum amount of the memory that strikes the best balance between the cost (capacity) and performance (reduction of capacity misses). #23: In the future, it could be that the concept of “locality of references” may not be an important concept any more, but how? If the unit price of memory becomes so low that we do not care “cost” any more. 3 #24: What is “secondary memory” (answer this question as a concept not by providing examples)? Explain the concept using your words (up to 8 words). Any non-volatile storage device. #25: What is the primary motivation of using cache memory? To reduce the access latency of the main memory or disk. #26: What is “word transfer”? Where is “word transfer” used? usually determined in a computer system? How is the “word size” #27: What is “block transfer”? Where is “block transfer” used? usually determined in a computer system? How is the “block size” Block transfer = All the data in the same block will be loaded to the cache memory when any one of them are requested by a processor. Block transfer is used between the main memory and cache memory. Block size is determined using the size that solves the trade-off between the initial misses and the capacity misses. #28: What is the advantage of using block transfer? Since “block transfer” will transfer the contents of all the consecutive in the same memory block, it will improve cache hit rate (initial misses) – this obviously is utilizing “space locality in reference” mentioned in the above question. #29: What are the primary design factors for cache memory? examples. For each factor, mention Write-through and write back #30: What if: If the block size is relatively too small? Many cache misses due to initial misses (cache hit rate will not be optimized in terms of initial misses). If the block size is relatively too large? Many cache misses due to capacity misses (cache hit rate will not be optimized in terms of capacity misses). #31: How (or “when”) is programmed I/O used? See the solutions for #34. 4 #32: How (or “when”) is interrupt-based I/O used? See the solutions for #34. #33: What program does “program” in “programmed I/O” mean (mention the name of the program)? Device drivers #34: What are the primary differences between “programmed I/O” and “interrupt-driven I/O”? “Programmed I/O” and “interrupt-driven I/O” are the same in that a processor executes instructions to process I/O events, but the following differences between them: Issues *Transfer direction Who initiates? * Timing Programmed I/O’s Memory I/O device Processor Predictable (since a processor initiates, the processor knows when programmed I/O’s are needed to be performed) Interrupt-driven I/O’s I/O device Memory I/O device Unpredictable (since each I/O device initiates, the processor never knows when interrupt-driven I/O’s are needed to be performed) Note: The above solutions are examples and some other correct solutions are possible (but the ones with “*” mark are the necessary solution. #35: For which of “programmed I/O” or “interrupt-driven I/O”, their response time is more important? Briefly explain why. Te response time is more important to “interrupt-driven I/O” than to “programmed I/O”, It is because, if the interrupt handler for an I/O device can not complete its interrupt handling before its next interrupt, the information that should be handled by the previous interrupt will be lost. #36: What problem(s) could occur if a computer system does not use “interrupt-driven I/O”? The processor must periodically execute the device handler for each I/O device installed in the system, which will waste a lot of the processor cycles. #37: Why was DMA introduced? Explain the primary reason using your words. To save the processor cycles. Using DMA, a processor only requests data transfer between I/O devices and the main memory and DMA performs the transfers on behalf of the processor. 5 #38: Describe the typical DMA procedure (for data transfer from memory to an I/O device). You can assume the DMA is the one available in the computer system (not in an I/O device). DMA Controller CPU Memory Command Data transfer to I/O device Data read from memory BUS Network Interface Card Buffer To Network #39: What are the typical parameters a processor needs to provide to a DMA controller (for data transfer from memory to an I/O device). You can assume the DMA is the one available in the computer system (not in an I/O device). The direction of the data transfer (from the memory to an I/O device) The destination I/O device ID (this specifies to which I/O device the data should be transferred to) Starting memory address The number of bytes to be transferred ***************************************************************************** Notes: (1) You can prepare your solutions for the above questions using group-study method and share the solutions except for those questions that are specified as “answer the question using your words”. For those questions, you must provide a solution using your words (i.e. you can NOT share a solution with your classmate). (2) Since the questions contained in the above list are all from undergraduate computer architecture and organization, everyone should not have a serious problem in preparing a solution. Therefore, Dr. Fujinoki will not provide solutions for the list before the test. For anyone who has serious problems in preparing solutions for the above list, it is strongly recommended for you to take CS516 (Computer Architecture) before you take this course. (3) Since the test for the above questions is a part of the first midterm exam, serious academic dishonesty will result in zero credit for your first midterm exam. If there is anything unclear for the SIUE standards for academic dishonesty, please talk to Dr. Fujinoki for his advises. Dr. Fujinoki will NOT be responsible for your wrong assumptions for the criteria for academic dishonesty. 6