Jitter tolerance - Progressivebusinessmedia

advertisement

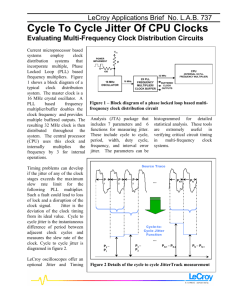

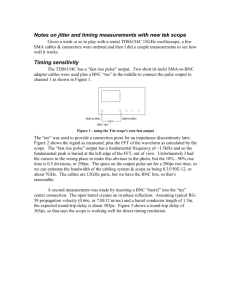

Jitter generation and measurement with off-the-shelf test equipment Slobodan Milijevic, Zarlink Semiconductor During the component selection process for a new communication product, jitter characteristics of Phase Locked Loops (PLLs) from different vendors are often evaluated to determine which one is best suited for the application. If specialized test equipment is not available, such as a jitter modulator, phase noise spectrum analyzer, and time interval analyzer, then standard test equipment can be used. This article will show that PLL jitter measurement can be done with a signal generator with phase modulation (PM) or frequency modulation (FM) and a digital oscilloscope. Specifically, we will outline how to measure jitter tolerance, jitter transfer, and jitter generation. Jitter basics Jitter is defined in ITU (International Telecommunication Union) and Telcordia specifications as “short-term variations of a digital signal’s significant instance from their ideal position in time.” Essentially, jitter is the term commonly used to describe the phase noise of digital signals. The two parameters that fully define phase noise are amplitude and frequency. Phase noise at frequencies below 10 Hz is referred to as wander, while phase noise at frequencies equal to or larger than 10 Hz is called jitter. 1UI Jitter frequency [Hz] = 1/Tj Tj Jitter amplitude [UIpp] Figure 1. Jitter amplitude and frequency When observing a jittery clock with an oscilloscope, we will see that the rising and falling edges of the clock are blurred (not clearly defined in time) as shown in Figure 1. The width of the blurred region defines jitter amplitude. The amplitude of the jitter in network communications is expressed in unit intervals (UI), where unit interval is equal to the clock period. For instance, the amplitude of the jitter in Figure 1 is 0.25 UIpp. The frequency of the jitter shown in Figure 1 illustrates a case where the jitter has a sine wave shape. Jitter in telecom networks typically has random shape in time domain. Consequently, its frequency spectrum is not discrete, although it may have some discrete components. There are number of jitter sources within telecom networks: Bit stuffing in a PDH network, used for asynchronous multiplexing of the lower level signals to one of the higher-level PDH signals. For example, bit stuffing is used to multiplex four asynchronous E1 signals to one E2 signal. Here, stuffing bits are used in the E2 signal either as fillers or as data bearers to compensate for frequency differences among mapped E1 signals. The major drawback of stuffing bits (and the other overhead bits) is that they generate a gapped (jittery) clock during demultiplexing of a higher-level signal into lower level signals. Pointer adjustment in a SDH/SONET network, which allows the virtual container (VC)/virtual tributary (VT) to move back and forth inside an STM-N/OC-N frame. Pointer adjustment is used to compensate for phase variations between clocks used for VC/VT and STM-N/OC-N. Pointer adjustment is done in steps of one byte, so it tends to generate jitter with large amplitudes. Imperfection of the clock extraction in line receivers and repeaters. Crosstalk and impulse noise in transmission lines. Imperfection in transmission line equalization. Equalization is used in transmission lines to cancel out symbol interference. Due to imperfection in transmission line equalization, some residual symbol interference will cause either positive or negative phase errors during the clock extraction depending on previous received symbols. Hence, the generated jitter will be data dependant. Intrinsic jitter in synchronization elements (PLLs). PLLs are used to attenuate jitter but they also generate a certain amount of jitter, which is dependent primarily on the PLL’s loop bandwidth and Voltage Controlled Oscillator (VCO) phase noise. Jitter tolerance Jitter tolerance specifies how much jitter the PLL can tolerate and still maintain synchronization without generating any alarm. Test set-up for jitter tolerance measurement is shown is Figure 2. Figure 2. Test set-up for jitter tolerance measurement Two signal generators with the same time-base (by slaving one from the other) are used for this test. One is used to generate stimulus (clock with sinusoidal jitter) for the PLL whose output is fed to the digital scope. The output of the other signal generator is used as a trigger signal for the scope. Because of the high jitter amplitudes applied to the input of the PLL, its output can also have high jitter amplitudes (especially for low jitter frequencies). For the output jitter amplitudes above 0.5 UIpp we will not be able to check if the PLL is still locked because the whole signal trace will be blurred. Therefore, we should either use the PLL output clock with lower frequency if available or use an external divider. The frequency of the clock used as a trigger has to be lower or equal to the frequency of the clock under test. Otherwise, the input and output clocks will not look synchronized on the scope, because the scope does not display continuously input signal. Instead, it takes spaced snapshots and overlays them on the display. For example, (Figure 3) if the scope were triggered with the clk2, the clk1 would not appear synchronized. Figure 3. clk1 appears not locked to clk2 if the clk2 is used for triggering If the PLL includes any alarm output, such as outside of range indication or lock indication of the input clock, they should be also observed on the scope. Testing is performed in the following way: The jitter amplitude of the PLL input clock is slowly increased until the PLL either looses lock or generates an alarm signal; Jitter frequency is increased and the procedure is repeated. Measured jitter tolerance values are compared against the jitter tolerance template of the timing spec we are trying to meet, as shown in Figure 4. Figure 4. Typical jitter tolerance test result Let us now see how to generate jitter using a phase modulation (PM) or frequency modulation (FM) capable signal generator. The general form of an angle-modulated signal (FM and PM) is: st A cos2f c t t (1) For simplicity we are using a sine wave function for s(t), although in digital communications it is usually a square-wave function. It can be shown that squaring the sine wave function does not affect angle modulation. We consider here only the sine wave modulating signals. For PM, the phase t in (1) is proportional to the modulation signal. (t ) DPM cos2fm t DPM is the phase deviation (peak variation of the phase) and f m is the modulating frequency. (2) The modulating frequency is the same as the jitter frequency. The relationship between phase deviation and jitter amplitude is straightforward and can be obtained from: Jitter[UIpp] DPM 180 DPM has units of radians in communications theory, but for convenience most signal generators use degrees instead. For FM, the phase t in (1) is proportional to the integral of modulating signal. (t ) 2DFM cos2f m t dt (3) DFM is the frequency deviation (peak variation of the frequency) and f m is the modulating frequency. The FM modulating frequency is the same as the jitter frequency. The jitter amplitude can be obtained from: Jitter[UIpp] DFM f m (4) This is derived from: (t ) 2DFM cos2fm t dt 2DFM 1 cos 2fm t 2fm 2 Therefore, the peak-to-peak deviation of (t ) is: pp 2 2DFM 2 DFM 2f m fm (5) The factor 2 in (5) comes from the peak-to-peak amplitude of a sine wave function. To get jitter/wander in UIpp we need to divide equation (5) by the period of the sine wave function (2). Thus, we get equation (4). It should be noted here that equation (4) is only valid when the modulating signal is a sine wave because the integral of a sine wave is also a sine wave function (just shifted in phase). Fortunately, sine wave modulation is almost exclusively used in jitter tolerance tests. Some signal generators use phase and frequency span as opposed to phase and frequency deviation. For PM, the span is peak-to-peak variation of the phase and for FM the span is peakto-peak variation of the frequency. That is Span = 2 x Deviation for both PM and FM. In this case the jitter amplitude for PM is: Jitter[UIpp] Span PM 360 Jitter[UIpp] Span FM 2f m And for FM: Jitter transfer Jitter transfer shows the ratio between the output and input jitter with respect to the jitter frequency. It is defined as: Output _ jitter[UIpp] Jitter _ Transfer[dB] 20 * log Input _ jitter[UIpp] Because a PLL can be viewed as a low pass filter of the phase noise, the jitter transfer is equivalent to the frequency characteristic of this filter. The jitter transfer shows at what jitter frequencies the PLL starts to attenuate jitter (PLL loop bandwidth). It also shows if the PLL exhibits any jitter peaking (gain) in the passband region. The maximum allowable jitter gain in passband region is usually limited to very small values (0.1 dB to 0.2 dB) because jitter can accumulate to unacceptably high values when the clock is passed through the chain of synchronization elements (PLLs). A typical PLL jitter transfer curve is shown in Figure 5. Figure 5. Typical jitter transfer test result Jitter transfer test setup is the same as jitter tolerance testing (Figure 2.) Jittery clock generated with the signal generator is fed to the PLL input. The amplitude of the PLL output jitter is measured with an oscilloscope set to infinite persistence mode triggered by the jitter-free clock from the other signal generator. Measurement is repeated for different jitter frequencies of the input clock and the results are compared against the jitter transfer template from the targeted timing specification. Input jitter amplitude should be constant for all measurements and it is selected to be smaller than the jitter tolerance of the PLL at highest jitter frequency. This is typically below 0.5 UI so that the PLL output clock and the trigger reference from the second signal generator do not have to be divided down. Jitter generation Jitter generation represents the amount of intrinsic jitter a PLL generates when it is fed with the jitter free input clock. Jitter measurement techniques used for jitter transfer are not recommended here unless the PLL has relatively large intrinsic jitter (typically a few nanoseconds or more). This is primarily because the accuracy of jitter measurement is dependent on how clean the reference clock used for triggering is. More accurate jitter reading can be obtained if the clock under test (output of the PLL) is referenced to the delayed version of itself. This can be done with the delayed triggering feature offered on most digital oscilloscopes. As the triggering delay is increased, the measured jitter is also increased up to the point where it becomes constant, as shown in Figure 5. In statistical terms, the jitter autocorrelation decreases as the delay increases and becomes zero (jitter totally uncorrelated) as the measured jitter curve flattens out. It should be noted that this applies only for the random jitter. If the clock under test has deterministic jitter components (sinusoidal jitter) at frequencies n/T (n = 0, 1, 2, …) where T is triggering delay, the resulting measured jitter would be equal to zero. Therefore, the triggering delay behaves like a phase noise notch filter, with a first notch at 0 Hz, the next one at 1/T Hz and so on. The presence of the deterministic components can be detected if the measured jitter value oscillates with the change of the trigger delay above the corner delay value. Figure 6. Jitter vs. oscilloscope trigger delay Some high-end digital oscilloscopes have a jitter measurement feature that automatically sweeps the trigger delay, measures random and deterministic jitter and displays the histogram of jitter distribution. In network communication timing specs, the maximum intrinsic jitter is specified in Unit Intervals peak-to-peak when measured through a first order bandpass filter. Unfortunately, with an oscilloscope, we can only get total unfiltered jitter. However, if the measured unfiltered jitter is smaller that the spec requirement then the PLL meets the spec because unfiltered jitter is always larger than or equal to the filtered jitter. This is fine for the majority of network interface jitter requirements, such as T1, E1, T3, E3 and OC-3 (STM-1). However, for higher speed network interfaces such as OC-12, OC-48, OC-192, use of phase noise spectrum analyzers is indispensable because they can measure sub-picosecond jitter (rms) and provide insight into frequency distribution of the phase noise, which can be easily filtered and integrated. Conclusion This article has illustrated how off-the-shelf signal generators and a digital oscilloscope can be used to evaluate jitter related parameters of a PLL. In addition, it has shown how to convert PM and FM parameters (phase deviation, frequency deviation and modulating frequency) into jitter parameters (amplitude and frequency) used in network communications. References 1. Synchronous Optical Network (SONET) Transport Systems: Common Generic Criteria GR-253-CORE, Issue 3, 2000 2. Clocks for the Synchronized Network: Common Generic Criteria GR-1244-CORE, Issue 2, 2000 3. Timing characteristics of SDH equipment slave clocks (SEC) ITU-T Recommendation G.813, 1998 4. Definitions and terminology for synchronization networks ITU-T Recommendation G.810, 1996 5. Transport Systems Generic Requirements (TSGR): Common Requirements GR-499CORE, Issue 2, 1998 Slobodan Milijevic is a Senior Applications Engineer with Zarlink Semiconductor. He can be reached at slobodan.milijevic@zarlink.com.