Homework 10

advertisement

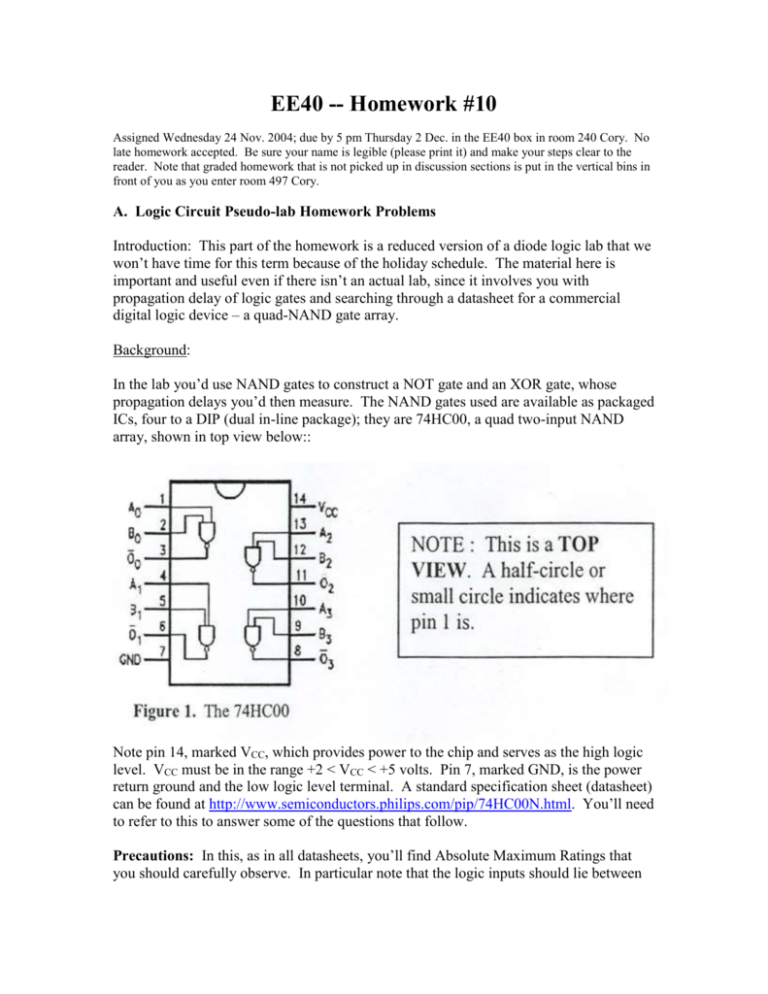

EE40 -- Homework #10 Assigned Wednesday 24 Nov. 2004; due by 5 pm Thursday 2 Dec. in the EE40 box in room 240 Cory. No late homework accepted. Be sure your name is legible (please print it) and make your steps clear to the reader. Note that graded homework that is not picked up in discussion sections is put in the vertical bins in front of you as you enter room 497 Cory. A. Logic Circuit Pseudo-lab Homework Problems Introduction: This part of the homework is a reduced version of a diode logic lab that we won’t have time for this term because of the holiday schedule. The material here is important and useful even if there isn’t an actual lab, since it involves you with propagation delay of logic gates and searching through a datasheet for a commercial digital logic device – a quad-NAND gate array. Background: In the lab you’d use NAND gates to construct a NOT gate and an XOR gate, whose propagation delays you’d then measure. The NAND gates used are available as packaged ICs, four to a DIP (dual in-line package); they are 74HC00, a quad two-input NAND array, shown in top view below:: Note pin 14, marked VCC, which provides power to the chip and serves as the high logic level. VCC must be in the range +2 < VCC < +5 volts. Pin 7, marked GND, is the power return ground and the low logic level terminal. A standard specification sheet (datasheet) can be found at http://www.semiconductors.philips.com/pip/74HC00N.html. You’ll need to refer to this to answer some of the questions that follow. Precautions: In this, as in all datasheets, you’ll find Absolute Maximum Ratings that you should carefully observe. In particular note that the logic inputs should lie between 0 V and VCC. If the logic inputs exceed VCC, the IC will be destroyed; likewise, if the logic input voltages are negative with respect to ground, the part will be destroyed. To repeat, logic inputs must be positive voltages in the range of 0 V to VCC, a positive voltage no greater than +5 V. Problem 1. [10 points] a. Write the truth table for the exclusive OR (XOR). b. Write a sum-of-products expression for the XOR function. c. Draw the logic circuit for this function using AND and NOR gates. d. Draw a circuit equivalent to the XOR using only NAND gates – NAND gates can be used to implement any logic function. Your text shows NAND realizations of NOT, AND and OR functions. (Note that you can use a two-input NAND gate as an inverter for the variable A either by connecting the two inputs together and applying input A to them, or by putting a logical 1 on one input and applying the variable A to the other input. The second realization may be preferable when speed is important because it loads the gate producing A with only one FET input capacitance.) e. Verify your design by finding the truth table for your circuit and comparing it with the XOR truth table. Problem 2. [15 points] The propagation delay of a logic gate such as a simple inverter is the time between when the rising input reaches 50% of VCC and the time the falling output reaches 50% of VCC. This is denoted in the Figure below (from the datasheet referred to above) as tPHL for a rising input and as tPLH for a falling input. The values for these quantities are given on the page headed “AC CHARACTERISTICS” in the datasheet. You will note that typical values for these times (for an ambient temperature between –40 and +85 oC) vary from 7ns to 25ns, become longer as the value of VCC is lowered from 6.0 V to 2.0 V. This is because the delay is governed by RC time constants where R is the resistance of the FET channel, which is larger when the bias voltage is lower. In a lab you would hook up in series a few (N) inverters made by connecting NANDs as described above, and measure the time it takes for a digital pulse to travel from the input of the first inverter to the output of the last inverter. This technique magnifies the fairly small propagation delay of a single gate by N (placing less stringent demands on the speed of the measurement equipment) and also by having most of the inverters “see” a typical load – another logic gate. a. For 74HC00 NAND gates at an ambient temperature Tamb = -40 to +85 oC at the maximum bias voltage, what is the time delay from when both inputs reach 50% of the logic 1 level until the inverter output falls to 50% of the 0 logic level? b. For the same conditions, what is the time delay from when both inputs fall to 50% of the logic 1 level until the output rises to 50% of its logic 1 level? c. The average gate delay is the average of these two values, Tpropagation delay = (Tlow-to-high + Thigh-to-low)/2. What would this value be for the conditions stated?? d. What would be the delay from the input of gate 1 to the output of gate 4 (in a 5-gate string, so that gate 4 was loaded by a gate rather than an oscilloscope or voltmeter probe with its larger capacitance)? B. Regular Problems on Digital Logic Problem 3 [20 points] Deriving and simplifying a logic function a. Consider the following situation. You want to start your car’s engine, which requires gas (logical variable G). You may or may not have a charged battery (logical variable B) and you may or may not be at the top of a hill (logical variable H). Write a truth table for starting (logical output S). Write a truth table for the situation, laying the variables in order – G, B, H – for the output S using “positive logic”: if you’ve got gas G = 1, … successful start S = 1. b. Using the sum-of-products method write the function S(G, B, H). c. Draw the logic circuit for this function. d. Simplify the expression for S using Boolean algebra. Make your method clear to the grader. e. Use a Karnaugh map to simplify the function S. f. Draw the logic circuit for the simplified function S. g. How many transistors are required to realize the un-simplified function (part b) using NOT, OR and AND gates as needed. (Note: to make an AND gate you can put a NAND gate in series with an inverter.) h. Determine how many transistors are required to realize the simplified version of S? i. If you were to use only NAND gates to realize the simplified function S how many transistors would be required? j. Comment on the answers to parts g, h and i. Problem 4. [10 points] Text Problem 7.23 Problem 5 [10 points] Text Problem 7.29, parts A, B, C only. Problem 6 [10 points] Text Problem 7.67. Also, comment on what output Q0 does relative to VIN. Likewise for output Q1. Problem 7 [10 points] Text Problem 7.70