NCSUSyllabusFall02

advertisement

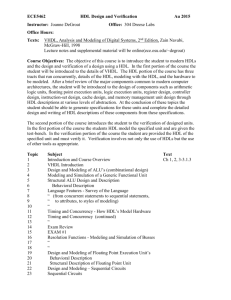

ECE 591 E - ASIC Verification Fall 2002 Course Syllabus Introduction Welcome to ASIC Verification, I am pleased to be working with Dr. Paul Franzon on bringing this class to NCSU. To let everyone know a little about myself, I am a verification engineer for IBM Corp. I have a background in ASIC verification, ASIC design, and tools. I have worked for IBM Corp. for approximately 9 years. My latest responsibilities include being the verification lead for a multimillion gate (approximately 40 million) next generation Network Processor. My e-mail is: jcgoss@unity.ncsu.edu My phone number is: (919) 254-0820 I tend to not be at my desk throughout the day, so I would prefer that you send questions and correspondence via e-mail. Office hours will be before class (6:30 – 7:30 PM, Mon/Wed). Course Layout There will be at least 3 homework assignments (maybe more), these homework assignments will consist of 15% of a students overall grade. The homework will be handed out, and you will have 1 week to complete the assignment. Late homework will not be accepted unless prior approval and arrangements are made. There will be 3 working labs. These labs will consist of 40% of a students overall grade. Each lab will be different in duration based on its complexity. Each lab is constructed so that each student must find all the bugs in the design in order to achieve a 100%. But because all bugs are found, does not necessarily deem the student achieves a 100%. Each student is required to hand in an analysis of the bugs and how they were found. There will be 2 exams – a midterm and a final. Each exam will consist of 20% of a student’s grade. Cheating will not be tolerated. Anyone found cheating will result in a zero for that lab and be turned in to the Academic Review Committee. Course Syllabus Class Topic 1 2 3 4 5 6 7 8 9 10 11 Course Introduction What is Verification Verification Tools Verification Plan – Strategies Verification Plan – Testcases Verification Plan – Testbenches Architecting Testbenches Architecting Testbenches Architecting Testbenches Architecting Testbenches Lab 1 Solution Discussion / Architecting Testbenches Architecting Testbenches EXAM #1 – Chapters 1,2,3,6 Lab 2 Overview / Stimulus and Response Review EXAM #1 Stimulus and Response 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 Chapters in Book Chapter 1 Chapter 1 Chapter 2 Chapter 3 Chapter 3 Chapter 3 Chapter 6 Chapter 6 Chapter 6 Chapter 6 Chapter 6 HW/Labs HW 1 Assigned HW 1 Due/HW 2 Assigned HW 2 Due/HW 3 Assigned HW 3 Due/Lab 1 Assigned Lab 1 Due Chapter 6 Chapter 5 Lab 2 Assigned Chapter 5 Lab 1 Due/Lab 2 Assigned Stimulus and Response Stimulus and Response Special Topic Day Chapter 5 Chapter 5 Lab 2 Solution Discussion / Stimulus and Response Behavioral HDL Behavioral HDL Lab 3 Overview / Behavioral HDL Simulation Management Special Topic Day Chapter 5 EXAM #2 – Chapters 5,4,7 Lab Day Review Exam #2 Exam Week Chapter 6 Chapter 4 Chapter 4 Chapter 4 Chapter 7 Online NetSeminar on new verification technologies Lab 2 Due Lab 3 Assigned Online NetSeminar on new verification technologies Lab 3 Presentation/Escape Analysis