February 6, 2008 Santa Clara, California

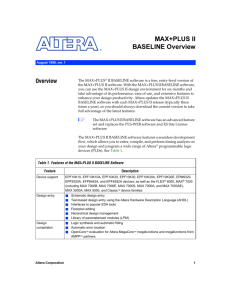

advertisement

Conference February 4 - February 7, 2008 Exhibition February 6 - February 6, 2008 Santa Clara, California CD-ROM Technical Paper Proceedings Sponsor www.bertscope.com BERTScope Clock Recovery Primer Part 1 Clock Recovery Primer Part 2 Guy Foster, SyntheSys Research, Inc. Track 1 | Chip-Level Architectural & Functional Design 1-TA1 How to Quickly Create Complicated Message Sequence Charts Automatically without Spending Money on Software Debra Klopfenstein, SGI 1-TA2 Designing and Verifying Ratio Synchronous Clocks (RSC) for High-Performance Low-Power Processors Ping Yeung, Mentor Graphics Chris Kwok, Mentor Graphics Matt Berman, Mentor Graphics Harry Stuimer, Sun MicroSystems Scott Wakefield, Sun MicroSystems Eugena Talvola, Sun MicroSystems Catherine Ahlschlager, Sun MicroSystems 1-TA3 ESL Driven Instrumentation Interfaces Neal Stollon, HDL Dynamics Mark Burton, GreenSocs Ltd 1-TA4 A Reset Control Apparatus for PLL Power-Up Sequence and AutoSynchronization Kazi Asaduzzaman, Altera Tim Hoang, Altera Kang-Wei Lai, Altera Wanli Chang, Altera Leon Zheng, Altera Mian Smith, Altera Sergey Shumarayev, Altera 1-TP1 Design and Application of Embedded Waveform Viewing Technology for Integrated Circuits Gary McCormack, Vitesse Semiconductor Eric Sweetman, Vitesse Semiconductor Ian Kyles, Vitesse Semiconductor 1-TP2 Methods for Configurable Hardware Design Craig Rawlings, Kilopass Technology 1-WA1 Multimedia Application Specific Engine Design Using High-Level Synthesis Nitin Chawla, STMicroelectronics Roberto Guizzetti, STMicroelectronics Yan Meroth, STMicroelectronics Arnaud Deleule, STMicroelectronics Vishal Gupta, STMicroelectronics Vinod Kathail, Synfora Pascal Urard, STMicroelectronics 1-WA2 Evaluating Embedded Non-Volatile Memory for 65 nm and Beyond Wlodek Kurjanowicz, Sidense 1-THA1 On-Chip Instrumentation for In-System IP Validation of a 6 Gbps Serial ATA Platform Device Martin Schrader, Infineon Technologies AG Miron Abramovici, DAFCA Daniel Hoggar, DAFCA 1-THA2 HW/SW Partitioning Tradeoffs in 3G & WiMAX Wireless Base Stations Jakob Saxtorph, Integrated Device Technology 1-THA3 Transaction Level Assertions in an Interface Definition Language Dave Whipp, NVIDIA Track 2 | Functional and Performance Verification 2-TA3 Hope Is Not a (Verification) Strategy – Coverage Model Driven Functional Scenario Generation Adnan Hamid, Breker Verification 2-TA4 Bridging Block-Level to Top-Level CDC Verification: Hierarchical CDC Verification Chris Kwok, Mentor Graphics Corporation Jean-Yves Larguier, Infineon Technologies Wesley Park, Mentor Graphics Corporation Japinder Singh, Mentor Graphics Corporation Andreas Meyer, Infineon Technologies 2-TP1 A Python-Based SoC Validation and Test Environment Nicolas Tribie, Wipro Newlogic Olivier Fargant, Wipro Newlogic 2-TP2 Sources of Non-Determinism in Microprocessors James Golab, Freescale Semiconductor 2-WP1 How to Find if My Checker Is Complete and Exhaustive — A Set of Guidelines Using Systemverilog and Memory Controller Example Leena Singh, Qualcomm Dinesh Malviya, Rambus 2-WP2 Mixed-Signal Integration: Functional Verification in the Presence of Linear Analog Components Thomas Sheffler, Rambus 2-THA1 Visual Data Analysis Approach to Design Verification Pandy Kalimuthu, WIPRO Technologies 2-THA2 Formal Verification Flow in FPGA Designs Sanjana Nair, Synplicity Vidyulatha Murthy, Synplicity Track 3 | Chip – Level Physical Design and DFM 3-WA1 Using Programmable Logic for Receiver Offset and Yield Enhancement Simar Maangat, Altera Corporation Toan Nguyen, Altera Corporation Wilson Wong, Altera Corporation Tina Tran, Altera Corporation Sergey Shumarayev, Altera Corporation Tim Hoang, Altera Corporation 3-WA2 Packaging DfM into Design Service Flavio Cali, Silicon & Software Systems Track 4 | Chip-Level Electrical and Package Design 4-TP2 Simulations and Characterizations for GHz On-Chip Power Delivery Network (PDN) Vishram S. Pandit, Intel Corporation Woong Hwan Ryu, Intel Corporation Kirupa Pushparaj, Intel Corporation Sankalp Ramanujam, Intel Corporation Farag Fattouh, Intel Corporation 4-WP1 Process and Temperature Variations on Electrical Parameters of Wire-Bond BGA Packages: an Impact Analysis Using Simulation-Based DOE Methodology Hui Liu, Altera Hong Shi, Altera 4-WP2 FPGA I/O Timing Variations Due to Simultaneous Switching Outputs Zhe Li, Altera Iliya Zamek, Altera Peter Boyle, Altera Bozidar Krsnik, Altera Track 5 | PCB and Passive Component Technology 5-TA1 Utilization of Buried Capacitance(TM) — A Case Study Jun Fan, University of Missouri-Rolla Norm Smith, Teradata Jim Knighten, Teradata John Andresakis, Oak-Mitsui Yoshi Fukawa, Techdream Mark Harvey, Sanmina-SCI 5-TA2 Application of Foldy-Lax Multiple Scattering Method to Via Analysis in Multilayered Printed Circuit Board Xiaoxiong Gu, IBM Mark Ritter, IBM 5-TA3 Modeling Issues and Possible Solutions in the Design of High Speed Systems with Signals at 20 Gbps Antonio Ciccomancini Scogna, CST of America Jianmin Zhang, Cisco Systems Kelvin Qiu, Cisco Systems Qinghua Bill Chen, Cisco Systems 5-TA4 Solutions for Causal Modeling and a Technique for Measuring Causal, Broadband Dielectric Properties Chad Morgan, Tyco Electronics 5-TP1 ATE Interconnect Performance to 43 Gbps Using Advanced PCB Materials Heidi Barnes, Verigy Jose Moreira, Verigy Tom McCarthy, Taconic William Burns, Verigy Crescencio Gutierrez, Harbor Electronics Mike Resso, Agilent Technologies Track 6 | High-Speed Parallel Interface Design 6-WA1 A Fast Algorithm to Instantly Predict FPGA SSN for Various I/O Pin Assignments Geping Liu, Altera Zhuyuan Liu, , Altera Kundan Chand, Altera San Wong, Altera Kaiyu Ren, Altera Nafira Daud, Altera 6-WA2 Challenges in Implementing DDR3 Memory Interface on PCB Systems — A Methodology for Interfacing DDR3 SDRAM DIMM to an FPGA Phil Murray, Altera Corporation Feras Al-Hawari, Cadence Design Systems 6-WP1 Counting the Picoseconds: Integrating Timing, Signal, and Power Integrity Analysis Doug Burns, SiSoft Todd Westerhoff, SiSoft Jeff Boyd, Denali 6-WP2 Study of Signal and Power Integrity Challenges in High-Speed Memory I/O Designs Using Single-Ended Signaling Schemes Kyung Suk (Dan) Oh, Rambus Inc. Woopoung Kim, Rambus Inc. Joong-Ho Kim, Rambus Inc. John Wilson, Rambus Inc. Ralf Schmitt, Rambus Inc. Chuck Yuan, Rambus Inc. Lei Luo, Rambus Inc. Jade Kizer, Rambus Inc. John Eble, Rambus Inc. Fred Ware, Rambus Inc. Track 7 | Multi-Gigabit Serial Interconnects 7-TA1 The Impact of Common Mode Currents and Interconnect Inductance on the Signal Quality of Differential Signals in Multi-Board PCB Systems Samuel Connor, IBM Bhyrav Mutnury, IBM Mosin Mondal, IBM Pravin Patel, IBM Joseph (Jay) Diepenbrock, IBM Moises Cases, IBM Bruce Archambeault, IBM 7-TA2 Data Mining 12-Port S-Parameters Eric Bogatin, Bogatin Enterprises Mike Resso, Agilent 7-TA3 Demonstration of SerDes Modeling Using the Algorithmic Model Interface (AMI) Standard Michael Steinberger, Signal Integrity Software Todd Westerhoff, Signal Integrity Software Christopher White, Independent 7-TA4 BladeServer 10 Gbps Ethernet Backplace Design with Equalization Using Statistical Channel Analysis Pravin Patel, IBM Jeff Cutcher, Ansoft Corporation Tony Donisi, Ansoft Corporation Michael Tsuk, Ansoft Corporation Steve Pytal, Ansoft Corporation 7-TP1 Strategies for Coping with Nonlinear and Time Variant Behavior for High-Speed Serial Buffer Modeling Richard Mellitz, Intel Michael Tsuk, Ansoft Tony Donisi, Ansoft Steven G. Pytel Jr., Ansoft 7-TP2 Multi-GB/s Serial Channel Design Using a Hybrid Measurement and Simulation Platform Andrew Byers, Ansoft Dima Smolyansky, Tektronix Eugene Mayevskiy, Tektronix Will Miller, Efficere Technologies 7-WA1 The Need for Impulse Response Models and an Accurate Method for Impulse Generation from Band-Limited S-Parameters Fangyi Rao, Agilent Technologies Chad Morgan, Tyco Electronics Sanjeev Gupta, Agilent Technologies Vuk Borich, Agilent Technologies 7-WA2 Aggregation of Crosstalk in Backplanes Atul Gupta, InspireSys Corporation Henry Wong, Gennum 7-THA1 In Situ Characterization of High-Speed Signaling Systems with On-Chip Measurements Qi Lin, Rambus Kyung Suk (Dan) Oh, Rambus Jihong Ren, Rambus Brian Leibowitz, Rambus Jared Zerbe, Rambus Xingchao (Chuck) Yuan, Rambus 7-THA2 Performance Limitations of Backplane Links at 6 Gbps and Above Jason Chan, Amphenol-TCS Brian Kirk, Amphenol-TCS Jose Paniagua, Amphenol-TCS 7-THA3 A Design of Experiments for Gigabit Serial Backplane Channels Jack Carrel, Xilinx Bill Dempsey, Red Wire Enterprises Mike Resso, Agilent Technologies Track 8 | High-Speed Timing, Jitter, and Noise 8-TA1 Analysis of Crosstalk Effects on Jitter in Transceivers Daniel Chow, Altera 8-TA2 Modeling a Phase Interpolator as a Delta-Sigma A/D converter Andrew Martwick, Intel 8-TA3 Characterization of Gaussian Noise Sources Ransom Stephens, Ransom's Notes Robert Muro, NoiseCom 8-TA4 Crosstalk Measurement, Extraction, and Validation in 10 Gbps Serial Systems Pravil Patel, IBM Rubina Ahmed, IBM Moises Cases, IBM Gourgen Oganessyan, Molex Dave Dunham, Molex 8-TP1 A Novel Approach for Characterizing Pulse Width Shrinkage in High-Speed Digital Communications Systems Greg Le Cheminant, Agilent Technologies Jim Stimple, Agilent Technologies Douglas Zhao, Q Logic 8-TP2 Exploration of Deterministic Jitter Distributions Michael Steinberger, Signal Integrity Software 8-WP1 PCI Express Timing Margins Greg Edlund, IBM 8-WP2 A Systematic Approach to Solving Clock Synthesis and Clock Recovery Problems in High-Data-Rate Serial Bus Systems Jim Stimple, Agilent Technologies Greg D. Le Cheminant, Agilent Technologies Track 9 | High-Speed Signal Processing, Equalization and Coding 9-TA2 Design Considerations in High-Speed SerDes (25Gbps) Charlie Zhong, LSI Cathy Y. Liu, Telegent Systems Wenyi Jin, LSI Amaresh Malipatil, LSI George Tang, LSI Freeman Y. Zhong, LSI 9-WA1 Semi-Analytic Performance of NRZ/PAM4/PR2 Modulation across 8.5-25 Gbps Backplanes with Analog Equalization Pervez Aziz, LSI Adam Healey, LSI Gregory W. Sheets, LSI 9-WA2 Pre-Cursor ISI Cancellation John Plasterer,PMC-Sierra Jurgen Hissen, PMC-Sierra Ognjen Katic, PMC-Sierra Matthew McAdam, PMC-Sierra Tony Zortea, PMC-Sierra 9-WP1 Half-Rate Decision-Feedback Equalization — Di-Bit Response Analysis & Evaluation Jihong Ren, Rambus Brian Leibowitz, Rambus Dan Oh, Rambus Jared Zerbe, Rambus 9-WP2 Multilevel Signaling in High-Density, High-Speed Electrical Links Dong Kam, IBM T. J. Watson Research Center Troy Beukema, IBM Young Kwark, IBM Lei Shan, IBM Xiaoxiong Gu, IBM Petar Pepeljugoski, IBM T. J. Watson Research Center Mark Ritter, IBM T. J. Watson Research Center Track 10 | Power Integrity and Power-Aware Design 10-TA1 Impact of PCB Laminate Dimensions on Suppressing Modal Resonances Jason Miller, Sun Microsystems Gustavo Blando, Sun Microsystems K. Barry A. Williams, Sun Microsystems Istvan Novak, Sun Microsystems 10-TA2 High Bandwidth Modeling and Simulation of SSO Effects on Single-Ended Switching Performance of Complex FPGA System Designs Scott McMorrow, Teraspeed Consulting Group Chris Herrick, Ansoft Corporation Steve Pytel, Ansoft Corporation 10-TA3 Analyzing the Impact of Simultaneous Switching Noise on System Margin in Gigabit Single-Ended Memory Systems Ralf Schmitt, Rambus Joong-Ho Kim, Rambus Woopoung Kim, Rambus Dan Oh, Rambus June Feng, Rambus Chuck Yuan, Rambus Lei Luo, Rambus John Wilson, Rambus 10-TA4 Pushing the Envelope without Tears: An Advanced Power Delivery Solution Scott McMorrow, Teraspeed Consulting Group Brian Vicich, Samtec Steve Weir, Teraspeed Consulting Group 10-TP1 Using Full Wave Solvers for Practical Analysis of Capacitor Mounting Structures Scott McMorrow, Teraspeed Consulting Group Fabrizio Zanella, CST of America Track 11 | Electromagnetic Compatibility and Interference 11-TP2 Mode Conversion and EMI Performance of Shielded Cable Assemblies for 10 Gbps Data Transmission Jim Nadolny, Samtec Julian Ferry, Samtec Cesar Arroyo, Samtec 11-WA1 Heat Sink Design Flow for EMC Philippe Sochoux, Cisco Systems Jinghan Yu, Cisco Systems Alpesh Bhobe, Cisco Systems Federico Centola, Flomerics, Inc. 11-WA2 Loaded Parallel Stub Common Mode Filter Predrag Acimovic, PMC-Sierra 11-WP1 Cable EMI Characterization Using a Reverberation Chamber Joseph (Jay) Diepenbrock, IBM Bruce Archambeault, IBM 11-WP2 EMI Shielding of Cable Assemblies Dana Bergey, FCI Nathan Altland, FCI Track 12 | Test Fixturing and Measurement Methodology 12-TA1 Challenges and Solutions for Removing Fixture Effects in Multiport Measurements Robert Schaefer, Agilent Technologies 12-TA2 Broadband Resonant-Plate Permittivity Measurement Technique for Printed Wiring Boards Aided by Electromagnetic Simulations Bart McCoy, Mayo Clinic Benjamin Buhrow, Mayo Clinic Barry K. Gilbert, Mayo Clinic Erik S. Daniel, Mayo Clinic 12-WA1 A Jitter Estimation Method for Cascaded, Programmable Phase-Locked Loops Daniel Chow, Altera Vincent Tsui, Altera San Wong, Altera 12-WA2 50 GHz End Launch Connector Test Boards: the Description of the Development of Coax to Grounded Coplanar Launches and Through Lines on 30 mil Rogers 4350 Material with Comparison to Microstrip Bill Rosas, Southwest Microwave 12-WP1 High-Speed Serial Interconnect Imbalance Barry Olawsky, Hewlett-Packard Shafiq Rahman, Hewlett-Packard 12-WP2 Characterization Methodology for High-Density Microwave Fixtures Brock LaMeres, Probing Technology Brent Holcombe, Probing Technology Emad Soubh, Samtec 12-THA1 High-Speed Probe Interconnect Techniques Andy Heltborg, Tektronix Ira Pollock, Tektronix Richard Van Epps, Tektronix 12-THA2 Performance at the DUT: Techniques for Evaluating the Performance of an ATE System at the Device Under Test Socket Heidi Barnes, Verigy Jose Moreira, Verigy Michael Comai, Advanced Micro Devices Abraham Islas, Advanced Micro Devices Francisco Tamayo-Broes, Advanced Micro Devices Mike Resso, Agilent Technologies Antonio Ciccomancini Scogna, CST of America Orlando Bell, GigaTest Labs Ming Tsai, Amalfi Semiconductor 12-THA3 Frequency Domain Calibration: A Practical Approach for the Serial Data Designer Steven Corey, Tektronix Eric Bogatin, Bogatin Enterprises Dima Smolyansky, Tektronix Track 13 | RF and Signal Integrity 13-TA3 Study of Fundamental Limit and Packaging Technology Solutions for 40-Gbps Transceiver Package Design Hong Shi, Altera Xiaohong Jiang, Altera John Yuanlin Xie, Altera 13-TA4 Issues of Frequency Content of S-Parameter Data for High-Speed Channel Evaluation Anthony Sanders, Infineon Technologies AG Gourgen Oganessyan, Quellan Dan Gorcea, Flextronics 13-TP1 Validation Methods for S-Parameter Measurement-Based Models of Differential Transmission Lines Peter Pupalaikis, LeCroy 13-TP2 A New Test Fixture Crosstalk De-Embedding Technique Using Time-Domain Gating Eugene Mayevskiy, Tektronix Track 14| Chip/Package/Board/System Co-Design 14-TP2 Techniques for Co-Design of the Power Supply Chain from IC to Printed Circuit Board David Quint, Hewlett-Packard Charles Keen, Hewlett-Packard 14-WA1 The Future of Multi-Clock Systems Ransom Stephens, Ransom's Notes Roman Boroditsky, NEL Frequency Controls Jorge Gomez, NEL Frequency Controls 14-WA2 Interface Based Design Concepts for IC, PKG, PCB Co-Design William McCaffrey, Cadence Design Systems Vikas Kohli, Cadence Design Systems 14-WP1 Efficient Modeling and Design Optimization Methodology for Integrated Power and Signal Distribution in Digital Systems Nam Pham, IBM Bhyrav Mutnury, IBM Moises Cases, IBM Erdem Matoglu, IBM Tae Hong Kim, IBM 14-WP2 Modeling FPGA Current Waveform and Spectrum and PDN Noise Estimation Iliya Zamek, Altera Peter Boyle, Altera Zhe Li, Altera Shishuang Sun, Altera Xiaohe Chen, University of Missouri-Rolla Sandeep Chandra, University of Missouri-Rolla Tun Li, University of Missouri-Rolla Daryl Beetner, University of Missouri-Rolla James L. Drewniak, University of Missouri-Rolla Track 15| Business and Engineering Impacts 15-TA1 Is Congress Killing Innovation? Dennis Fernandez, Fernandez and Associates Christopher Fasel, Fernandez & Associates Garrett Eastham, Fernandez and Associates 15-TA2 Case Study Using the VSIA QIP to Evaluate Internally Developed Information Property David Parent, SJSU Paul Weil, Cadence 15-TA3 Lifecycle Cost Is a DIME — How to Make Build/Buy Decisions Lawrence Ricci, Applied Data Systems 15-TA4 ASIC 2-0 Chris Turner, Cambridge Consultants 15-TP1 BDU — A Complexity Measure for a Board Design Project Jitender Kumar Misra, Wipro Technologies Lakshmi Prasad Nanduri, Wipro Technologies Anand Mathew, Wipro Technologies Rajshekhar Patil, Wipro Technologies Amit Chhibba, Wipro Technologies Sajna Ibrahim, Wipro Technologies