ECE 272 Lab Manual: Digital Logic Design

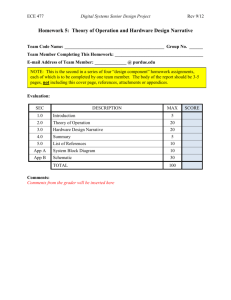

advertisement

ECE 272 Lab Manual Fall 2015 Copyright Information c Copyright 2015 Oregon State University School of Electrical Engineering & Computer Science (EECS) This document is the property of Oregon State University and the School of EECS. Limited use of this document is allowed, according to the following criteria: Materials are free to use, except for the cost of reproduction, and must always bear this statement in any reproduction. Materials created using this information may not be labeled as TekBots’ materials, without the prior written consent of both Oregon State University and the School of EECS. Disclaimer of Liability Oregon State University, Platforms for Learning, TekBots and other partner schools are not responsible for special, consequential, or incidental damages resulting from any breach of warranty, or under any legal theory, including lost profits, downtime, goodwill, damage to, or replacement of equipment or property, or any costs of recovering, reprogramming, or reproducing any data stored in or used with our products. The aforementioned parties are also not responsible for any personal damage, including that to life and health, resulting from use of any of our products. You take full responsibility for your product/ application, no matter how life-threatening it may be. Internet Access We maintain Internet systems for your use. They can be used to obtain free TekBots’ software and documentation and also to purchase TekBots products. These systems may also be used to communicate with members of TekBots and other customers. Access information is shown below: E-mail: tekbots@eecs.oregonstate.edu Web: http://www.tekbots.com ECE 272 Manual Contents 0 Preface 9 0.1 Lab Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 0.2 Objectives . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 0.3 Materials . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 0.4 Installing Lattice Diamond . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11 0.5 Lab Manual Conventions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11 0.6 Etiquette . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12 0.7 Resources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 0.8 Academic Dishonesty . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 0.9 Preparation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14 1 Basic Combinational Logic and the MachXO2 15 1.1 Section Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16 1.2 Objectives . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16 1.3 Materials . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16 1.4 Procedure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17 1.5 Design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18 1.6 Design Entry . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21 1.6.1 Start Diamond . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21 1.6.2 Create a New Project . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21 1.6.3 Schematic Entry . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22 3 CONTENTS 1.7 Design Simulation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25 1.8 Synthesize and Map Design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25 1.8.1 Synthesis . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25 1.8.2 Spreadsheet View . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26 1.8.3 Creating the Programming File . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27 1.9 Program Hardware . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28 1.9.1 Program the FPGA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28 1.9.2 Assemble the Push Button board . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28 1.10 Test Hardware . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29 1.11 Study Questions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29 1.12 Challenge - Extra Credit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30 2 Combinational Logic (Computer Arithmetic) 31 2.1 Section Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32 2.2 Objectives . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32 2.3 Materials . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32 2.4 Procedure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32 2.5 Design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33 2.5.1 Make a block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33 2.5.2 Make a functional truth table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34 2.6 Design Entry . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35 2.7 Design Simulation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35 2.7.1 Creating the Testbench . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35 2.7.2 Changing the Verilog Template . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35 2.7.3 Running the Simulation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36 2.8 Synthesize and Map Design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37 2.9 Program Hardware . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38 2.10 Test Hardware . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39 ECE 272 Manual CONTENTS 2.11 Study Questions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39 2.12 Challenge - Extra Credit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39 3 Combinational Logic (Seven Segment Driver) 41 3.1 Section Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42 3.2 Objectives . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42 3.3 Materials . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42 3.4 Procedure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42 3.5 Design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42 3.5.1 Make a block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43 3.5.2 Make a functional truth table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43 3.5.3 Minimize the logic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44 3.6 Design Entry . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44 3.7 Design Simulation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44 3.8 Synthesize and Map Design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44 3.9 Program Hardware . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44 3.9.1 Assemble Seven Segment Board,4digit.0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45 3.9.2 Test Hardware . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45 3.10 Study Questions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45 3.11 Challenge - Extra Credit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46 4 Multi-digit Display 47 4.1 Section Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48 4.2 Objective . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48 4.3 Materials . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48 4.4 Procedure: . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49 4.5 Display four digit reading on 4digit.0 board . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50 4.6 Study Questions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51 ECE 272 Manual CONTENTS 4.7 Challenge . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51 5 Voltmeter 53 5.1 Section Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54 5.2 Objective . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54 5.3 Materials . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54 5.4 Procedure: . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55 5.5 Block 1: Interface the ADC with the FPGA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56 5.5.1 ADC Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56 5.5.2 Procedure: . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56 5.6 Final Design: Interface the ADC with the 7-Segment Display . . . . . . . . . . . . . . . . . . . . . . . . . 57 5.6.1 Decode the Raw Output from the ADC and Display . . . . . . . . . . . . . . . . . . . . . . . . . 57 5.7 Study Questions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58 6 Final Design Project 59 6.1 Section Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60 6.2 Objective . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60 6.3 Materials . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60 6.4 Study Questions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60 A MachXO2 System Overview 61 A.1 System Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62 A.2 Parts of the Logic Board . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62 A.3 I/O Connectors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63 A.4 Programming Interface and LED Array . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64 A.4.1 USB Programming and Debug Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64 A.4.2 Bypassing the USB programming Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64 A.4.3 LEDs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64 A.5 Power Supply . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65 ECE 272 Manual CONTENTS A.5.1 Test Points . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65 A.5.2 Applying External Power . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65 A.5.3 Auxiliary Power Output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65 B Schematics 67 B.1 MachXO2 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68 B.2 USB Interface to JTAG . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69 B.3 FPGA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70 B.4 FPGA (cont.) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71 B.5 Power and LEDs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72 B.6 4-digit Seven Segment Display Board . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73 B.7 Push Button Board . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74 C Silk Screens and Pinouts 75 C.1 MachXO2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76 C.2 USB Buck Boost Converter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76 C.3 4-digit Seven Segment Display Board . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77 C.4 Push Button Board . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78 D Parts and Suppliers 79 D.1 Parts List . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80 D.2 Suppliers List . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80 c 2015 Oregon State University ECE 272 Manual 7 CONTENTS 8 ECE 272 Manual c 2015 Oregon State University Section 0 Preface 9 SECTION 0. PREFACE 0.1 Lab Overview Welcome to the ECE 272 lab manual! ECE 272 is the companion lab to ECE 271, the Digital Logic Design Class. This lab focuses on design hierarchy that begins with schematic capture and finishes with Verilog Hardware Description Language. The lab starts in Chapter 1 by introducing Lattice Diamond–the software suite that will be used throughout the lab to syntesize designs, simulate them, and program the FPGA. Chapters 2 through 4 use methods and skills learned in ECE 271–added to and refined over time–to construct different parts of a voltmeter, such as driver software for a digital display module. These will then finally be compiled together in Chapter 5 with an ADC into a complete product. Chapter 6, the final lab, will be open-ended and encourage you to do your own research and problem solving to come up with an experiment or project to show your mastery of the material. This lab provides the skills and tools needed to design digital logic systems and integrate them with other digital or analog systems. 0.2 Objectives • Materials • Lab Manual Conventions • Etiquette • Resources • Academic Dishonesty • Preparation 0.3 Materials • Lattice MachX02 Breakout development kit • Button board (8pushbtn.0) • 4 Digit 7 Segment Display Board (4 digit.0) • USB to mini cable • Tool kit • Soldering iron tip and barrel nut • Solder 10 ECE 272 Manual c 2015 Oregon State University 0.4. INSTALLING LATTICE DIAMOND 0.4 Installing Lattice Diamond 1. Create an account on Lattice’s webpage http://www.latticesemi.com/ 2. Navigate to ’Products, Design Software & Intellectual Property, Lattice Diamond’ 3. Click ’Downloads’ and select the most recent version for your operating system, for example ’Diamond 3.5 64-Bit for Windows’ If you are not logged in, the actual program download may not appear 4. Request license by clicking on ’Licensing’ then ’Lattice Diamond Software Free License’ and following the instructions Find your physical address by following the instructions at the top of the page Make sure you choose your Wi-Fi adapter, not your Ethernet port 5. Download license file and place it into the correct folder 6. Install based on your operating system Choose node-locked license when prompted for license settings If you are using Windows 8, Diamond must be run in compatibility mode. This can be done by right-clicking the shortcut, selecting properties, then checking the compatibility mode box in the compatibility tab and selecting Windows 7 0.5 Lab Manual Conventions This lab uses the following symbols. Many of these are important and should not be ignored or skipped. This symbol indicates an important note that should be remembered/memorized. Paying attention to notes like these will make tasks easier and more efficient. This symbol designates caution, and the information in this caution-table should be read thoroughly, and adhered to, before moving ahead. If the caution warning is ignored, the task may appear impossible and/or lead to damaged TekBot and systems. This symbol represents something that helps you make your task easier by reminding you to perform a particular task before the next step. These reminder symbols are not normally critical things to complete, but can make things easier. The innovation symbol will give information to enrich your experience. These sections will give more insight into the what, why, and how the task being done. Use these to learn more, or to get ideas for cool innovations. c 2015 Oregon State University ECE 272 Manual 11 SECTION 0. PREFACE Italicized writing is used to indicate the exact text on the menu or button for the next step in the lab manual. The entire lab is divided into various sections, in order to break up the tasks. Typically, each section will have the Section Overview as the introductory paragraphs and information detailing the tasks in the Procedure paragraphs. Towards the end, there are Study Questions (which will be your homework from this lab), and/or Challenges. Challenges are extra credit and are great learning opportunities. 0.6 Etiquette Proper etiquette in the labs is very important when working with other students or the Teaching Assistants (TAs). Engineers work with many different types of people and need to be able to do so efficiently. Another part of proper lab etiquette is also cleanliness in the lab. Engineers work in a variety of spaces. Sometimes they work in spaces that are exclusively theirs, but many work in shared spaces. When sharing work spaces, it’s important to respect others that must use that space by keeping it clean and removing any mess when finished. Students Students are expected to: • Prepare for each lab. Some labs require a prelab and background research before lab. Students should review appropriate sections in the lab manual before going to lab. This is important to make sure all the required tools are available and you have time to think conduct any necessary background research before lab. • Ask questions. Students should talk to their peers and the TAs when questions arise. Other people may have a different perspective on an issue. • Respect their peers. Everybody comes from a different background and has a different level of knowledge. Teaching Assistants (TAs) Teaching Assistants are expected to: • Ensure the lab is prepared. TAs make sure the lab is kept in good working condition and the provided materials are ready for the students during lab. • Fairly assess student performance. TAs should outline their requirements for full credit on prelabs and study questions at the beginning of the term and grade to this standard for the term. • Help students think through problems in lab. TAs will not give instant answers to problems encountered. They are available to guide students towards the correct answer. Workspace Keeping a workspace clean is very important. A messy workspace can be a safety hazard and create a chaotic environment. It is much easier to lose a small component when there are other items cluttering the table top. It is also important to keep a workspace clean because there are other classes that use the same room for their labs. Respect the lab and the other people that are working in the lab. 12 ECE 272 Manual c 2015 Oregon State University 0.7. RESOURCES 0.7 Resources There are many sources of information available for students in need of help. There is a hierarchy that students should follow to ask questions before going straight to the instructor. When a student has a question they should start on the first level to ask questions and progress from there without skipping levels. 1. Peers A student’s peers should be the first people to ask when a question arises. Asking peers not only helps the student with the question, but it reinforces the concept to the person asked when they explain it. A student has many peers so the total amount of time available with peers is much more than any other resource. 2. Teaching Assistants Teaching Assistants (TAs) have gone through this material before and are confident with the content, making them a valuable source of information. They have recent experience as a student in course and can offer insight regarding the course. 3. Instructor Going to the instructor or professor with a question should only happen when other students and the TAs couldn’t help. There is only a limited amount of time that an instructor is available for students to ask questions. Instructors will know the most about a topic and how it pertains to the course. Try to visit their office hours at least once during the term. Bring prepared questions or some suggestions on how to improve the lab. 0.8 Academic Dishonesty The following is taken from the Oregon University System, Oregon State University Student Conduct Code1 and for more information please refer to it. 1. Academic or Scholarly Dishonesty is defined as an act of deception in which a Student seeks to claim credit for the work or effort of another person, or uses unauthorized materials or fabricated information in any academic work or research, either through the Student’s own efforts or the efforts of another. 2. It includes: (a) CHEATING – use or attempted use of unauthorized materials, information or study aids, or an act of deceit by which a Student attempts to misrepresent mastery of academic effort or information. This includes but is not limited to unauthorized copying or collaboration on a test or assignment, using prohibited materials and texts, any misuse of an electronic device, or using any deceptive means to gain academic credit. (b) FABRICATION – falsification or invention of any information including but not limited to falsifying research, inventing or exaggerating data, or listing incorrect or fictitious references. (c) ASSISTING – helping another commit an act of academic dishonesty. This includes but is not limited to paying or bribing someone to acquire a test or assignment, changing someone’s grades or academic records, taking a test/doing an assignment for someone else by any means, including misuse of an electronic device. It is a violation of Oregon state law to create and offer to sell part or all of an educational assignment to another person (ORS 165.114) (d) TAMPERING – altering or interfering with evaluation instruments or documents. (e) PLAGIARISM – representing the words or ideas of another person or presenting someone else’s words, ideas, artistry or data as one’s own, or using one’s own previously submitted work. Plagiarism includes but is not limited to copying another person’s work (including unpublished material) without appropriate referencing, presenting someone else’s opinions and theories as one’s own, or working jointly on a project and then submitting it as one’s own work. 1 http://arcweb.sos.state.or.us/pages/rules/oars c 2015 Oregon State University 500/oar 576/576 015.html ECE 272 Manual 13 SECTION 0. PREFACE 3. Academic Dishonesty cases are handled initially by the academic units, following the process outlined in the University’s Academic Dishonesty Report Form, and will also be referred to SCCS for action under these rules. 0.9 Preparation Proper preparation allows for a smoother and more efficient lab time. Make sure to follow these steps before starting each lab. 1. Start with a clean work space. Often times, the electronic components used in lab are very small, and if dropped, they could be easily lost (among usual desktop clutter). Therefore, put away papers, keyboards, mice, clothing, etc. 2. Keep your parts neatly organized. Often times, parts come neatly packaged and ready for use. Do not dump all of these parts together, such as in a box. Instead, if parts come separated in small bags, try to keep them that way. When taking parts out of their packages, using a small container to keep them organized. Some people use ice cube trays, kitchen bowls, or other containers. 3. Care for your tools. The quality of electronics assembly is based on your own experience, and on the tools you use for the assembly. Hence, try to keep your tools in the best condition possible. When using cutting tools, try not to cut things that the tools are not designed to cut. An important lab rule to remember is to take care of your soldering iron properly. 4. Make sure you have everything you will need. When working with electronics, there is nothing more annoying than not having the parts you need, and/or having to stop what you are doing to go find them. Prevent this by double-checking that you have what is needed before starting the lab. This includes manuals, tools, components, pens, and paper. 14 ECE 272 Manual c 2015 Oregon State University Section 1 Basic Combinational Logic and the MachXO2 15 SECTION 1. BASIC COMBINATIONAL LOGIC AND THE MACHXO2 1.1 Section Overview The use of the logic gate integrated circuit (IC) has had several evolutions. The 7400-series logic chips were the most common digital logic devices around for many years. Most of these devices were single or quad chips that were the hardware equivalent of the logical (AND, OR, NOT, etc ...) gates. Designers using the 7400 series chips would configure multiple chips on a PCB to get the desired hardware equivalent to their logic design. Most digital logic implementations have moved either towards Programmable Logic Devices (PLDs) or towards Field Programmable Gate Arrays (FPGAs). These newer devices are designed so that the user can program the device configuration and/or logic. Using a hardware description language (HDL) these devices allow designers to move from physically configuring multiple chips on a circuit board in a permanent design to programming a versital single device to achieve the same result. 1. PLDs have a wide range in complexity and application. At one end the Programmable Logic Array (PLA) has a set number of hardware defined logic gates which get programmed in user defined configurations. While Complex Programmable Logic Devices (CPLD) use a HDL to design both the logic gates and the configuration. CPLDs are capable of representing thousands of logic gates and their configuration while PLAs are capable of only a few pre-defined gates in user defined configurations. 2. FPGAs are capable of being programmed to represent several hundred-thousand logic gates in user defined configurations on a scale of three times the amount of logic than that of a CPLD. Comparing the two PLDs are traditionally thought of as more limited in logic complexity than FPGAs, but also are considered more stable. Architectural differences are attributed to the FPGA outperforming the CPLD. CPLDs use Electrically Eraseable Programmable ReadOnly Memory (EEPROM–Information about this can be found by referencing the textbooks index) which is less volatile than the RAM the FPGA uses. The MachXO2 used in the TekBots program is an FPGA made by Lattice Semiconductor. There is more information about this board in Appendix A. 1.2 Objectives In this section, the following items will be covered: 1. Using the Lattice Diamond software to draft digital logic designs 2. Programming the MachXO2 provided in the ECE 272 kit 3. Verifying combinational logic designs 1.3 Materials 1. Lattice Diamond 3.5 software (Currently installed on the lab computers) 2. MachXO2 breakout board 3. Button Board (8pushbtn.0) 4. USB to mini-USB cable 16 ECE 272 Manual c 2015 Oregon State University 1.4. PROCEDURE 1.4 Procedure There are 6 steps to digital logic design: Figure 1.1: This six step process is used for designing in ECE 272. 1. Design: The context of the design is established in the ”Design” step. The context involves defining the desired output, input, and all of the logic required to connect the two. In this step, all of the minimizations and layout is planned for the entry process. While this step is not always the most lengthy, it involves the most thought and effort. 2. Design Entry: The actual drafting of the digital logic design occurs in this step. Drafting includes entering the logic gates and blocks to build the design in the software tool. 3. Design Simulation: Before committing to hardware, this step tests the design in a controlled computer simulation. If the design does not function as specified in the ”Design” step, it is revised. 4. Synthesize and Map Design: When the design simulates correctly, the source files are synthesized into a design file that configures the FPGA. Mapping the design to pins assigning the inputs and outputs of the design to IO pins on the MachXO2 FPGA. 5. Program Hardware: After the design file is created it is used to configure (program) the MachX02 FPGA. Programming uses the USB to mini-USB cable and the Lattice Diamond software to send a bit stream to configure the FPGA. 6. Test Hardware: Verify hardware operation once the FPGA has been programmed. The FPGA should operate exactly as the simulation predicted, but sysnthesis problems, timing violations, or incorrect assumptions about the hardware can require the designer to return to the ”Design” step. c 2015 Oregon State University ECE 272 Manual 17 SECTION 1. BASIC COMBINATIONAL LOGIC AND THE MACHXO2 1.5 Design A good design is the key to any successful project. In electrical engineering, many of our designs stem from a ’Block Diagram’ developed near the start of a project and evolved throughout the course of it. Block diagrams can encompass all levels of detail and abstraction in a project, so choosing the scale of the initial diagram can be a challenge. A good starting point is to represent each piece of hardware with a block and define all interfaces with it. Figure 1.2 shows the start of a simple block diagram for this lab. Figure 1.2: Incomplete block diagram for Section 1 At the beginning of a project, the block diagram should include: • Labelled blocks representing each piece of hardware used in the project • All interfaces (connections) between blocks, represented with lines • Which signals are carried on each interface • How the interfaces connect to each block, for example: pin numbers Depending on the project, more detail is added to the block diagram, often with very detailed blocks inside of the main hardware blocks. Figure 1.3 is the design that will be drafted in Diamond. Figure 1.3: Section1 Combinational Logic There are a few design choices that are dictated by the hardware.Familiarize yourself with the following concepts before attempting to design your logic. 18 ECE 272 Manual c 2015 Oregon State University 1.5. DESIGN Boolean Logic is true/ high or false/ low logic. In electrical engineering this logic can be expressed by two levels that are logical high and logical low with regards to the voltage being applied; which generally correspond to a binary 1 = VCC and 0 = GND. Signals with one of these two levels are often used used in digital circuit design or analysis. 1. Button Board: The buttons on the button board are active low. Refer to Figure 1.4 to get a partial schematic of the button board. The full schematic can be found in the appendices. Without a pull-up resistor the button board can output a floating voltage for a logic high. A pull-up resistor is a resistor connected between a signal conductor and a positive power supply voltage to ensure that the signal will be a valid logic level if external devices are disconnected or high-impedance is introduced. Figure 1.4: Example of an active low button 2. MachXO2: The LEDs on the MachXO2 are active low. This means they turn on when a logic low signal is sent to the FPGA pin and they turn off when a logic high signal is sent. When using the Lattice Diamond software, in spreadsheet view you can add a pull-up or pull-down resistor to any input or output on the MachX02. This allows the designer to ensure that the signals in and out are not floating values. Figure /refPullModes shows how the pulling resistor is connected to the pin inside of the FPGA. c 2015 Oregon State University ECE 272 Manual 19 SECTION 1. BASIC COMBINATIONAL LOGIC AND THE MACHXO2 Figure 1.5: PullModes 20 ECE 272 Manual c 2015 Oregon State University 1.6. DESIGN ENTRY 1.6 Design Entry 1.6.1 Start Diamond Click Start → All Programs → Lattice Diamond 2.2 (64 bit) → Lattice Diamond Installation instructions for Diamond can be found on the ECE272 page on TekBots.com 1.6.2 Create a New Project A project in Lattice Diamond is a collection of sources (Schematic or HDL), testbenches, and simulation outputs. Follow these steps to create the project for this section: 1. Click File → New → Project 2. Click Next to advance 3. In the Project Name field, enter ”section1”. Note that the project name automatically creates a subdirectory in the main directory path. However, the main directory must be specified. 4. In the Project Location field, browse to the directory that will store all projects and create a new folder for Section1. Diamond does not automatically create a folder for each project. Click Next. Using the C:\drive to store projects will make the software operate quicker than using the Z:\drive. Using the Z:\allows access to project files from any lab machine and is regularly backed up. The files in C:\are stored locally and can only be accessed from one computer. Keep a back up on Z:\to avoid frustrating crashes that will cause all project files to be corrupted. 5. In the Add Source window, leave everything blank and click Next. 6. Set the Device Settings to match Figure 1.6 and then click Next. c 2015 Oregon State University ECE 272 Manual 21 SECTION 1. BASIC COMBINATIONAL LOGIC AND THE MACHXO2 Figure 1.6: Copy these values for all projects 7. Select Lattice LSE as the Synthesis Tool and click Next. 8. Review the Project Information and click Finish. 9. The project’s Input Files folder is empty at this point. To add a source, Click File → New → File 10. In the New File window, under Source Files, select Schematic Files. 11. In the File name field, enter ”section1 schematic” 12. Make sure that the Add to Implementation box is checked and then click New. 13. The Diamond project screen will now be showing the blank schematic file. 1.6.3 Schematic Entry Follow these steps to create the schematic shown in Figure 1.3: Add Symbols: Follow these steps to add logic gates to the schematic: 22 ECE 272 Manual c 2015 Oregon State University 1.6. DESIGN ENTRY Figure 1.7: Add symbol process 1. Click the Symbol button 2. Select the lattice.lib library. 3. Select and2. 4. Place one AND gate onto the schematic. 5. Add both of the other gates from Figure 1.3 onto the schematic. Connect the Symbols: Use Figures 1.8 and 1.9 to understand how to properly draft a schematic. Proper design has inputs on the left stretching vertically and logic gates connected to the correct input lines. Use this general structure to create a schematic that reveals the structure, intent, and flow of the design. Figure 1.9: Good Layout Figure 1.8: Bad Layout c 2015 Oregon State University ECE 272 Manual 23 SECTION 1. BASIC COMBINATIONAL LOGIC AND THE MACHXO2 1. Click the Wire button 2. Wire all of the symbols together. Left click once for each segment, right click to stop placing wire. 3. Add hanging wires off of the inputs and output so that they can be named and designated as inputs or outputs in the next step. The marker for hanging wires and nodes are the same: a small square. Always double check these to make sure that you have made the connection that you intended. Define Inputs and Outputs Labeling the inputs and outputs on the schematic allows diamond to create a ’netlist’ (stands for a ’list of electrical networks’) during the synthesis process. A netlist contains all inputs, outputs, and gates for the design. and rename the hanging wires A, B, C, and Z. The labels must be placed on the 1. Click the Net Name button very end of the hanging wires or Diamond will not correctly place IO markers in the next step. 2. Click the IO Port button and specify the type as Input, and add a marker to A, B, and C. 3. Add an Output marker to Z. 4. Save the schematic (Ctrl-S). 24 ECE 272 Manual c 2015 Oregon State University 1.7. DESIGN SIMULATION 1.7 Design Simulation This design is trivial and the simulation of it will not fit in this lab. Simulation of digital logic designs will be in a future section of ECE 272. 1.8 1.8.1 Synthesize and Map Design Synthesis During synthesis, the design is minimized and transformed into a netlist describing the hardware. Minimizations reduce the amount of hardware and space required for the design. After synthesizing, Diamond knows how many inputs and outputs are required for the design. Follow this process to synthesize the design. Figure 1.10: Synthesize Design 1. Open the Process tab to the left of the schematic and double click Synthesize Design. c 2015 Oregon State University ECE 272 Manual 25 SECTION 1. BASIC COMBINATIONAL LOGIC AND THE MACHXO2 1.8.2 Spreadsheet View Spreadsheet view is a tool that will connect A, B, C, and Z from the schematic to Inputs/Output pins on the MachXO2. Use Figure 1.11 to organize the information required for Spreadsheet view. The PULLMODE setting determines if the port reads high (1) or low (0) when the port is undriven. PULLMODE UP assigns a pullup resistor to pull the pad voltage up to VCC. This results in an input port reading logic high when it is undriven. The FPGA pins are printed on the silkscreen of the MachXO2 board. Figure 1.11: This table should be recreated for every ECE 272 project Without a pullup resistor an input pin will float between logic high and logic low when the button is unpressed. Floating inputs cause eratic behavior. Run Spreadsheet View Follow these steps to run Spreadsheet view and configure the IO pins. Figure 1.12: Spreadsheet View 1. Click Tools → Spreadsheet View 2. In Spreadsheet View, select Port Assignments along the bottom edge. This page contains all the inputs and outputs from your schematic. 3. Here we assign the physical I/O pins that you chose for each input and output in the Pin column. The output Z in Spreadsheet View should be assigned to an LED on the MachXO2 so the output can be quickly verified. Figure 1.13 contains the FPGA pins for the LEDs. Inputs in Spreadsheet View should be assigned to empty IO pins on the MachXO2 and later connected to the active low buttons on the button board. 26 ECE 272 Manual c 2015 Oregon State University 1.8. SYNTHESIZE AND MAP DESIGN Figure 1.13: MachXO2 LED pinout 4. Select whether the port will use a pullup or pulldown resistor in the PULLMODE column (Reference figure 1.11). 5. Save the pin assignments (Ctrl-S). LEDs are an extremely useful tool for circuit verification, since they visually show the designer what is happening during any given moment. Carefully picking which signals get assigned to the LEDs can make troubleshooting much easier and save you a lot of time later. 1.8.3 Creating the Programming File The programmer needs a .jed (JEDEC programming specification) file in order to program the MachXO2. This step uses Diamond to generate a .jed programming file. 1. Open the Process tab to the left of the schematic and double click JEDEC File under Export Files. c 2015 Oregon State University ECE 272 Manual 27 SECTION 1. BASIC COMBINATIONAL LOGIC AND THE MACHXO2 1.9 Program Hardware 1.9.1 Program the FPGA Use this process to program the .jed file onto the FPGA. : Figure 1.14: Programmer 1. Plug the MachXO2 into the computer with the provided USB cable. Communication between the Breakout Board and a PC via the USB connection cable requires installation of the FTDI chip USB hardware drivers. Loading these drivers enables the computer to recognize and program the Breakout Board. Refer to the Diamond Installation instructions for FTDI driver installation instructions. 2. Click Tools → Programmer 3. Click OK to identify the correct cable. If Diamond cannot identify the target device, manually select ”LCMXO2-7000HE” from the Device dropdown menu. 4. In the File Name column, browse to the .jed file that Diamond created in the project directory. 5. Click Program 1.9.2 Assemble the Push Button board The inputs A, B, and C will be provided by three buttons on the push button board that will be connected to the corresponding three pins you chose on the MachX02. J1-J8 buttons correspond to each of the buttons in order. For the applications in this lab, if SW COM is tied to ground, the outputs J1-J8 can be connected to the FPGA and the buttons will operate as active low buttons. To assemble the push button board, follow these steps. All required parts should be in the kit. 1. Open a webpage to tekbots.com. 2. Click on Hardware, and find the 8 Push Button board. 3. Now that you are on the 8 Push Button page click on Assembly Guide. Follow the guide to complete this task. Soldering the header into either side of the PCB will function identically, however, it will be easier to use the buttons if they are placed on the opposite side as the board. 28 ECE 272 Manual c 2015 Oregon State University 1.10. TEST HARDWARE 1.10 Test Hardware Create and fill in a truth table that shows your hardware operates correctly. This truth table has 3 inputs and 1 output. Look at Figure 1.15. Assume that A and B are active low buttons and Z is connected to an active low LED. The filled in row indicates that when A is not pushed, B is pushed, then the output Z turns on the LED. In future labs this truth table should match your simulation results. Since simulation is not required in this lab we will skip this comparison. Figure 1.15: Truth Table for Section 1 Testing What if you want to measure voltage? To do this you need to use a Digital Multimeter (DMM). A DMM has two probes, black and red. To measure a voltage, place the black probe’s metal tip on a pin on your board you know is 0V. Next, place the metal point of the red probe on the output you want to measure. Assuming you have set the DMM to measure DC voltage, you will see a number around either 0, or 3.3V. The T.A. must verify that the students schematic design matches figure 1.3 and spreadsheet inputs/outputs match the students Pin & Pullmode Table (figure 1.11). Student must demonstrate that their hardware logic matches their truth table (figure 1.14). TA Signature: (The MachXO2 board logic is operational & lab work is displayed) 1.11 Study Questions 1. Turn in a printed copy of the schematic designed in this lab. 2. Describe any problems encountered in this lab and your solutions to those problems. 3. Give an example of where discrete logic ICs (7400 series logic chips) are used in industry and why. 4. Give an example of when you should use an FPGA instead of a PLA and explain why. Give an example of when you should use an PLA instead of a FPGA and explain why. Expand on the background information given in the Section Overview. c 2015 Oregon State University ECE 272 Manual 29 SECTION 1. BASIC COMBINATIONAL LOGIC AND THE MACHXO2 1.12 Challenge - Extra Credit Research a ring oscillator. This circuit is a great way to explore the propagation delay of a simple logic gate (the inverter). Credit for the challenge is allocated based on lessons learned from experiments that you design yourself. Here are some beginning ideas: These ICs can be purchased either from the TekBots store in KEC 1110, or from the IEEE store in the Dearborn basement, or from a local electronic parts store. 1. Try to implement a ring oscillator with an integrated circuit of 7400 series logic chips. How fast does it oscillate? How does the propagation time relate to the VCC powering the integrated circuit? 2. Try to implement the ring oscillator with the FPGA. How fast does it oscillate? Can the FPGA be reconfigured to operate faster or slower? 3. Try to implement the ring oscillator with hand made inverters (either discrete integrated circuits or in your FPGA). How fast does it oscillate? Does it vary with temperature? 30 ECE 272 Manual c 2015 Oregon State University Section 2 Combinational Logic (Computer Arithmetic) 31 SECTION 2. COMBINATIONAL LOGIC (COMPUTER ARITHMETIC) 2.1 Section Overview This section uses logic gates to build a 1 bit adder, and then 1 bit adders to build a 4 bit adder. The two 4 digit binary numbers are controlled with 8 buttons, and the sum is displayed on 5 Light Emitting Diodes (LEDs). 2.2 Objectives In this section, the following items will be covered: 1. Defining the problem — what is the adder really doing? 2. Defining the inputs to the combinational logic 3. Defining the outputs from the combinational logic 2.3 Materials 1. Lattice Diamond 3.4.1 software 2. MachXO2 breakout board 3. USB to mini-USB cable 4. Button board (8pushbtn) 5. Chapter 5 of the textbook 2.4 Procedure There are 6 steps to digital logic design: Figure 2.1: Use this process for designing the adder. In Section2 we will follow the same implementation steps we used for Section1. 32 ECE 272 Manual c 2015 Oregon State University 2.5. DESIGN 2.5 Design Configure two 4 bit inputs to represent binary inputs with the 8 Push Button board. These inputs will be the four digit binary numbers that will be added together. The binary sum will be displayed on the MachX02s LEDs. 2.5.1 Make a block diagram Draw out the function of the system using blocks that only describe the basic function of how they work, not the details of how each block accomplishes its task. Draw the adder in two fashions, truth table and using ripple carry adders. Two example block diagrams are below for these possible systems. The higher level block diagram is only a single block (Figure 2.2 left) while the ripple carry adder is built with multipler simple 1 bit adders ( Figure 2.2 right). The left diagram is easier to understand, but the right diagram is easier to construct. Figure 2.2: Two Block Diagram Options Follow these steps to create a complete block diagram from Figure 2.2: 1. Show how the button board connects to the FPGA. 2. Add the power source used for each of the button board, FPGA, and LEDs. The FPGA takes 5V in from the mini-USB port, but has a high logic level voltage of 3.3V. The button board is powered from one of the 3.3V connections on the FPGA. The boards and the LEDs need to share a common ground to be able to communicate. To achieve this connect all of the grounds, so that there is a common ground reference for your separate boards. 3. Label the FPGA pins on the block diagram. This makes it easier to connect wires between the button board, to assign the pins correctly in Lattice Diamond, and to check correct operation of the final adder. c 2015 Oregon State University ECE 272 Manual 33 SECTION 2. COMBINATIONAL LOGIC (COMPUTER ARITHMETIC) The FPGA pins are printed on the breakout board. Find which ones will be convenient to use for the inputs and outputs and label them on the block diagram. 2.5.2 Make a functional truth table 1. Add the decimal values of the outputs for each row. Don’t forget these are signed numbers! 2. Write the binary equivalents for each output. Operand 1 0b0000 0b0000 0b0000 0b0000 0b0000 0b0000 0b1000 0b1000 0b1000 0b1000 0b1111 0b1111 0b1111 0b1111 + + + + + + + + + + + + + + + Operand 2 0b0000 0b0001 0b0010 0b0011 0b0100 0b0101 0b0000 0b0001 0b0010 0b0011 0b1000 0b1001 0b1010 0b1011 = = = = = = = = = = = = = = = Binary Value (5 bits) Unsigned10 Signed10 This table is incomplete, and in fact would be 256 (28 ) possible combinations. Minimizing and drawing the logic for this high level adder is unfeasible. This adder (and lots of other computational devices) can be solved by first designing logic for a single bit and then scaling to multiple bits. Look at the textbook to learn how to implement a 4 bit ripple carry adder. This adder should use 4 single bit adders. Define truth table for a single bit wide adder. Start by filling in the table for a full adder below. In this table, there are the two bits to be added (operand 1 and 2) and a ’carry in’ bit. Adding 3 ones together yields a 310 or 112 as an output. Operand 1 0b0 0b0 0b0 0b0 0b1 0b1 0b1 0b1 + + + + + + + + + Operand 2 0b0 0b0 0b1 0b1 0b0 0b0 0b1 0b1 + + + + + + + + + Carry In 0b0 0b1 0b0 0b1 0b0 0b1 0b0 0b1 = = = = = = = = = Value10 Value2 A description of a full adder, the base unit of a ripple carry adder, is shown at the beginning of Chapter 5 in the textbook From the table above, the least signifignt bit of the output is the sum while the upper bit is the carry bit. It is easier to name them this way. Pay special attention to the carry input on the least significant bit of the 4 bit adder. 34 ECE 272 Manual c 2015 Oregon State University 2.6. DESIGN ENTRY 2.6 Design Entry Enter the design using the same process as in Section 1. Make a full adder module and connect 4 of them together to create a final 4 bit ripple-carry adder. This involves making a symbol from your full adder schematic. To make a custom symbol follow the Design Entry process, then go to the Design tab and click Generate Symbol. When making the four bit ripple-carry adder and adding the symbol, simply choose the file path that goes to the folder that contains the symbol. 2.7 Design Simulation In this section the design is tested by entering in all possible input combinations and comparing the simulated output to the desired output. If they match, the design is verified and the process can advance. Debug and try again until the desired output is achieved if there are discrepancies. 2.7.1 Creating the Testbench Follow this process and refer to Figure 2.3 to create a Verilog testbench. A testbench contains commands for simulation. Figure 2.3: Testbench generation process 1. Synthesize the design. Double click Synthesize Design on the Process tab. 2. Right click the top level source on the Hierarchy tab and click Verilog Test Fixture Template. Diamond puts this testbench into the source files folder on the File List tab. 2.7.2 Changing the Verilog Template Input all of the simulation directives here. These tell the simulator what different combination of inputs to use and how long to hold each combination. The output will be displayed based on the input directives inserted in the testbench. 1. Change the text between ”initial begin” and ”end” to match the text below. c 2015 Oregon State University ECE 272 Manual 35 SECTION 2. COMBINATIONAL LOGIC (COMPUTER ARITHMETIC) The #10 at the beginning of each line denotes how long the simulation is to use that combination of inputs before moving on to the next line. It is measured in time units specified during the simulation (default is nanoseconds). initial begin A0 = 0; A1 = 0; A2 = 0; A3 = 0; B0 = 0; B1 = 0; B2 = 0; B3 = 0; #10 A0 = 0; A1 = 0; A2 = 0; A3 = 0; B0 = 1; B1 = 1; B2 = 1; B3 = 1; (0 and 15) #10 A0 = 1; A1 = 1; A2 = 0; A3 = 0; B0 = 1; B1 = 1; B2 = 0; B3 = 0; (3 and 3) #10 A0 = 0; A1 = 0; A2 = 1; A3 = 0; B0 = 0; B1 = 0; B2 = 1; B3 = 0; (4 and 4) #10 A0 = 1; A1 = 1; A2 = 1; A3 = 1; B0 = 1; B1 = 1; B2 = 1; B3 = 1; (15 and 15) (Continue adding different numbers like so.) end 2.7.3 Running the Simulation 1. Run Simulation Wizard. Tools → Simulation Wizard 2. Welcome Screen: Click Next to pass the welcome screen. 3. Simulator Project Name: Type any name for Simulator Project Name. This creates a new folder within your project folder that holds the simulation files. Ensure Active-HDL is selected for as the Simulator and click next. Click Yes to create the simulation folder. 4. Process Stage: This option selects the amount of realism the simulation will use. Select RTL for simulating ideal conditions (no gate or trace delay). 5. Add and Reorder Source: Ensure that all of the source files and the testbench file are located here in the box (they should be auto-populated by default. If they are missing, backtrack and find where a mistake was made). Click Next to advance. 6. Parse HDL files for simulation: Ensure that no errors appear in the output box and that the testbench is selected as the ”Simulation Top Module.” Click Next. 7. Summary: Make sure all check-boxes are selected and click Finish. 8. Prompt: If a prompt appears, the simulation has previously ran. Click Yes to overwrite old settings and the simulator will open. ActiveHDL must be closed and restarted before you can simulate again. Zooming in and out of the simulation makes the outputs easier to see. Zoom by holding the Ctrl key and scrolling with the scroll wheel or by using the zoom controls on the top toolbar. 36 ECE 272 Manual c 2015 Oregon State University 2.8. SYNTHESIZE AND MAP DESIGN 2.8 Synthesize and Map Design Follow the same process for using Spreadsheet view as in Section 1. c 2015 Oregon State University ECE 272 Manual 37 SECTION 2. COMBINATIONAL LOGIC (COMPUTER ARITHMETIC) 2.9 Program Hardware 1. Program the MachXO2 using the same process as in Section 1. 2. Wire the FPGA to both the push button board and the 5 LEDs using the block diagram made earlier as a guide. Refer the information on LEDs in section 1 for a reminder about how to wire the LEDs. 38 ECE 272 Manual c 2015 Oregon State University 2.10. TEST HARDWARE 2.10 Test Hardware Validate that the hardware performs according to the functional table completed earlier in Section 2. TA Signature: (Adder illuminates LEDs correctly based on inputs from push buttons) 2.11 Study Questions 1. You explored ripple-carry adders and creating a single logic block for adding two 4 bit numbers. In 200 or more words, what are the advantages and disadvantages of each option? 2.12 Challenge - Extra Credit This section designed, built, and tested (simulation and hardware validation) a simple 4 bit adder. Now design and demonstrate a 4 bit ALU that can add or subtract based on if an extra input is set to high or low (Information on ALUs can be found in chapter 5 in your textbook). Implement a 4 bit adder/subtractor. Full credit will be given for design, simulation, and implementation into the FPGA. 1. Subtract input low: (Operand 1) + (Operand 2) 2. Subtract input high: (Operand 1) - (Operand 2) c 2015 Oregon State University ECE 272 Manual 39 SECTION 2. COMBINATIONAL LOGIC (COMPUTER ARITHMETIC) 40 ECE 272 Manual c 2015 Oregon State University Section 3 Combinational Logic (Seven Segment Driver) 41 SECTION 3. COMBINATIONAL LOGIC (SEVEN SEGMENT DRIVER) 3.1 Section Overview Being able to display numbers is useful for a variety of applications. Seven segment displays are used to display numbers in alarm clocks, VCRs, microwaves, and many other devices. Section 3 builds a seven-segment display decoder, which is described in Example 2.10 of the ECE 271 textbook. The decoder will take a 4 bit bus as input from buttons and output a 7 bit bus for the seven segment display. 3.2 Objectives In this section, the following items will be covered: 1. Define the problem, what is the decoder really doing? 2. Define the inputs to the combinational logic. 3. Define the outputs from the combinational logic. 3.3 Materials 1. Lattice Diamond 3.5 software 2. MachXO2 Breakout Board 3. Seven segment display board (4digit.0) 4. Button board (8pushbtn.0) 5. USB to mini-USB cable 3.4 Procedure There are 6 steps to digital logic design: Figure 3.1: Use this process for designing the seven segment display. 3.5 Design Figure 3.2 shows all of the different outputs that the seven segment decoder should produce. Shade in the segments that should be on for each input, 0-F. Figure 3.2: The decoder should produce all 16 outputs 42 ECE 272 Manual c 2015 Oregon State University 3.5. DESIGN 3.5.1 Make a block diagram Turn in the block diagram as part of the study questions. Use clean paper and write neatly. 1. Add the power source used, if any, for each of the three blocks. See Figure 3.5 or 4digitSchematic in Appendix B f igureB.7 for information about how to power the 7 segment display board. 2. Label all FPGA pins that are used for this project on the block diagram. Figure 3.3: Incomplete block diagram for the remote control 3.5.2 Make a functional truth table 1. Use the shading in Figure 3.2 and the diagram in Figure 3.4 to fill in the functional truth table below. Figure 3.4: This diagram indicates which segments are which on the display (should match what was found in the pre-lab.) c 2015 Oregon State University ECE 272 Manual 43 SECTION 3. COMBINATIONAL LOGIC (SEVEN SEGMENT DRIVER) Input Hex 0 1 2 3 4 5 6 7 8 9 a b c d e f Inputs, ĀB̄ C̄ D̄ 0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 1010 1011 1100 1101 1110 1111 SegA 0 SegB 0 SegC 0 SegD 0 SegE 0 SegF 0 SegG 1 Make sure to double check the above table for accuracy. Errors this early in the design can lead to a lengthy debugging process. 3.5.3 Minimize the logic 1. Use seven K-maps to make minimized logic for SegA , SegB , SegC , SegD , SegE , SegF , and SegG . 2. Write out the minimized Boolean Equations for each output. 3.6 Design Entry Enter the design using the same process as in Section 1. A larger workspace in Diamond will be needed to fit the entire minimized schematic. To change the schematic size click Edit → Sheet. 3.7 Design Simulation Simulate the design to verify correct operation of the digital logic. Use Section 2 as a guide for this process. 3.8 Synthesize and Map Design Follow the same process for using Spreadsheet View as in Section 1. 3.9 Program Hardware 1. Program the FPGA 44 ECE 272 Manual c 2015 Oregon State University 3.10. STUDY QUESTIONS 3.9.1 Assemble Seven Segment Board,4digit.0 To assemble the Seven Segment Board, follow these steps. All required parts should be in the kit. 1. Open a webpage to tekbots.com. 2. Click on Hardware, and find the 4 Digit LED board. 3. Now that you are on the 4 Digit LED Board page click on Assembly Guide. Follow the guide to complete this task. 3.9.2 Test Hardware 1. Wire together the FPGA and Seven Segment Board as depicted in the block diagram made earlier. Refer to figure 3.5 for wiring instructions. Make sure that every labelled pin on the diagram is connected. The select pins should be attached according to the table on the left of the diagram. 2. Test to see if the buttons cause the correct outputs on the seven segment display. Figure 3.5: Display Board wiring diagram. TA Signature: (Seven Segment display is working and all lab steps are shown) 3.10 Study Questions 1. When is a simulation necessary? Was it useful for this section? 2. Attach the detailed block diagram, digital logic schematic, and simulation results for this project. c 2015 Oregon State University ECE 272 Manual 45 SECTION 3. COMBINATIONAL LOGIC (SEVEN SEGMENT DRIVER) 3.11 Challenge - Extra Credit Connect the 7 segment display to the adder from section 2. Display the sum output from the adder onto the 7 segment display. 46 ECE 272 Manual c 2015 Oregon State University Section 4 Multi-digit Display 47 SECTION 4. MULTI-DIGIT DISPLAY 4.1 Section Overview Section 3 developed a design to drive a 7-segment display. This section will use POV (Persistance of Vision) to display all 4 digits. Essentially this will turn on the 1000’s digit for a few milliseconds, then the 100’s digit, then the 10’s digit, and finally the 1’s digit, before repeating the cycle starting at the 1000’s digit. A state machine controls the cycle between the different digits. 4.2 Objective In this section, the following items will be covered: 1. Build a system that will diplay a large binary value (maybe 10 bits) as an input and output 0 - 1023 on the seven segment board. 2. Use the button board to generate an 8 bit digital value. 3. Design and test a state machine that will cycle through turning on 1 digit at a time. 4. Import a provided math module that separates a 10 digit value into 4 distinct 4 bit values for each digit. 5. Combine the digit cycler state machine, the provided digit separater module, and lab 3 into a multi-digit display. 6. Simulate the design and validate the hardware. 4.3 Materials 1. Lattice Diamond 3.5 software 2. MachXO2 Breakout board 3. 4digit.0 4. The ECE 271 textbook, Digital Design and Computer Architecture by Drs. David and Sarah Harris 48 ECE 272 Manual c 2015 Oregon State University 4.4. PROCEDURE: 4.4 Procedure: There are 6 steps to digital logic design Figure 4.1: Use this process for the designing section 4. In section 4 we will follow the same implementation steps we have used in previous labs. Only this time the implementation steps will be applied to smaller blocks and again before integrating all the blocks into one system. c 2015 Oregon State University ECE 272 Manual 49 SECTION 4. MULTI-DIGIT DISPLAY 4.5 Display four digit reading on 4digit.0 board Take lessons learned in section 3 about the 4digit.0 board and what we learned in section 4 about HDL and state machines to make a display for the ADC readings. Procedure: 1. Design HDL system that will display numerical values on all four digits of the seven segment board. A state machine should be used to cycle between the four digits (four states). Use the 7-Seg SEL inputs to choose which digit is being displayed. The frequency at which the digits are cycles will determine the brightness of the LEDs. Refer to HDL Example 4.24 on the Verilog reference sheet, available at Tekbots.com, for an example on how to write a decoder in Verilog for a seven segment display. A multiplexer works well for switching the value displayed on each digit. Look up persistence of vision to find out how quickly the state machine should cycle 2. Using your design, enter the digital logic into the software 3. Simulate with enough possible inputs to have confidence that your design will perform as expected. 4. Follow synthesis and map design from previous labs, by connecting the seven segment board control lines to the pins you selected in the pin assignments. Figure 4.2: Display Board Wiring Diagram and Digit Select Table. 5. Program the FPGA 6. Test the implemented system by hard coding a multi-digit number into the input of the FPGA logic to verify that you get the expected results. TA Signature: (A meaningful analog voltage is digitized and displayed on the seven segment display board) 50 ECE 272 Manual c 2015 Oregon State University 4.6. STUDY QUESTIONS 4.6 Study Questions 1. Include a detailed block diagram of Section 4, the HDL Schematic, and a copy of the Verilog source. 4.7 Challenge 1. Use the PWM input on the 4digit.0 board to control the brightness of the numbers. c 2015 Oregon State University ECE 272 Manual 51 SECTION 4. MULTI-DIGIT DISPLAY 52 ECE 272 Manual c 2015 Oregon State University Section 5 Voltmeter 53 SECTION 5. VOLTMETER 5.1 Section Overview To interface with the analog world, embedded systems use Analog to Digital Converters (ADCs). An ADC takes an analog voltage as input and outputs a digital value. In this lab, the digital value will be converted to seven segment output on multiple digits. It is important to be able to actually use the concepts learned in this course to design real systems. Solving a design problem that will use multiple concepts is tough, but rewarding. Interfacing smaller working blocks together can quickly result in a larger system. This design is easier to visualize if split into a series of less difficult pieces. Figure 5.1: Incomplete Block Diagram for Final Project. 5.2 Objective In this section, the following items will be covered: 1. Build a system that will take an analog voltage as an input and output 0 - 1000 on the seven segment board. Refer to Figure 5.1 for a block diagram of this project. 2. Use a potentiometer to generate an analog voltage for the ADC. Connect the ADC to the FPGA and display the ADC’s binary output on the MachXO2’s onboard LEDs. 3. Design and test a module that will display all four digits of the seven segment display 4. Interface the two modules so that the raw output from the ADC is displayed on the seven segment display 5. Decode the raw ADC data into an analog voltage value 5.3 Materials 1. Lattice Diamond 3.5 software 2. MachXO2 Breakout board 3. AD7705 Dual 16-bit ADC Data Acquisition Module 4. 4digit.0 5. The ECE 271 textbook, Digital Design and Computer Architecture by Drs. David and Sarah Harris 54 ECE 272 Manual c 2015 Oregon State University 5.4. PROCEDURE: 5.4 Procedure: There are 6 steps to digital logic design Figure 5.2: Use this process for designing the final project. Follow the same implementation steps for section 5 as was used in previous labs. Only this time the implementation steps will be applied to smaller blocks and again before integrating all the blocks into one system. c 2015 Oregon State University ECE 272 Manual 55 SECTION 5. VOLTMETER 5.5 Block 1: Interface the ADC with the FPGA As discovered in the prelab, the ADC operates based on serial control signals. A Verilog module that generates the required signals can be found on the lab webpage. 5.5.1 ADC Introduction Analog to Digital Converters, or ADCs, are the electronic bridge between the analog and digital worlds. The implementations are often very different, but the functionality remains the same: the ADC will input an analog voltage and represent the value with a certain number of bits. In our application, the ADC outputs 16 bits and operates at 3.3 volts. In order to use the ADC properly in our digital system, In1+ should be connected to the voltage we want to measure and In1- should be connected to ground Figure ??. The control signals, CS, Din, Dout, and RST are generated by a provided Verilog module and are described in detail in the ADC’s datasheet. Don’t forget to also connect power and ground to the ADC module. Figure 5.3: ADC Visual Representation Figure 5.3 shows a visual representation and the mathematical relationship between Vin and Dout, as well as some examples of typical voltages. 5.5.2 Procedure: 1. Since the design has already been given, instantiate the ADC Verilog module that outputs the control signals to the ADC. Use the LEDs on the FPGA to display the eight most significant bits of the ADC output data. 2. Simulate with enough possible inputs to have confidence that your design will perform as expected. 56 ECE 272 Manual c 2015 Oregon State University 5.6. FINAL DESIGN: INTERFACE THE ADC WITH THE 7-SEGMENT DISPLAY 3. Follow synthesis and map design from previous labs, by connecting the ADC control lines to the pins you selected in the pin assignments. 4. Program the FPGA 5. Test the system by varying the voltage at IN+ of the ADC with a potentiometer. Figure 5.4 shows how to wire the potentiometer to the ADC module inputs. Remember to be sure the ground on the potentiometer connects back to the ground of your FPGA and all other grounds. Figure 5.4: ADC Potentiometer Wiring 5.6 Final Design: Interface the ADC with the 7-Segment Display Display the raw output from the ADC on the 7-Segment Display. Procedure: 1. Designing the final system requires you to understand how the ADC output needs to be manipulated to give you a usable value. Use math to extract the individual digit that is needed from the 0-32768 range. For example, to grab the hundreds digit: hundreds = input_8_bit / 100 Verilog truncates any remainder and leaves the whole number result of the division. The modulus operator (%) will be useful for obtaining individual numbers. After extracting an individual 0-9, the number can be sent to a decoder for seven segment output. If any modules have a bus that needs to be separated into wires for each bit or several wires that need to be combined into a bus for another input, refer to section 4.2.9, Bit Swizzling, in the textbook. 5.6.1 Decode the Raw Output from the ADC and Display Display an analog voltage range on the seven segment board, for example: 2.456 Volts. This effectively creates a voltmeter. Getting from ADC output to a usable value takes a conversion equation. Consider an input from 0 to 3.3V that corresponds to an output from 0 to 32768, what conversion is necessary to get the voltage? c 2015 Oregon State University ECE 272 Manual 57 SECTION 5. VOLTMETER A decimal point will have to be added. There is one decimal point per digit, operated with an eighth pin. During which states will it be on? The digit isolation developed for checkpoint 3 should be done after the number conversion 2. Now that you have your final design follow the procedure to complete the system. TA Signature: (A meaningful analog voltage is digitized and displayed on the seven segment display board) 5.7 Study Questions 1. Include a detailed block diagram of Section 5, the HDL Schematic, and a copy of the Verilog source. 58 ECE 272 Manual c 2015 Oregon State University Section 6 Final Design Project 59 SECTION 6. FINAL DESIGN PROJECT 6.1 Section Overview Design and build something interesting, using primarily parts from an ECE lab offered at OSU. Some ideas would be controlling the FPGA or the Teensy2.0 with a retro gaming controller, TV remote, bluetooth device, or something else. Develop a guitar tuner or effects pedal with the FPGA. Experiment with different functions in Verilog and see how many blocks are used in the synthesis (large multipliers or adders). 6.2 Objective Learn something about the FPGA and digital logic. 6.3 Materials 1. Lattice Diamond 3.5 software 2. MachXO2 Breakout board 3. 4digit.0 4. The ECE 271 textbook, Digital Design and Computer Architecture by Drs. David and Sarah Harris TA Signature: (An impressive project was completed and documented with a professional final report.) 6.4 Study Questions 1. Include a detailed block diagram of Section 6, the HDL Schematic, and a copy of the Verilog source. 2. What was the toughest aspect of ECE 272? What should be changed or added to the ECE 272 manual to make this course better? 3. What would you like to explore further about Lattice Diamond or Digital Logic Design? 4. What section of ECE 272 did you dislike the most? Why? 5. What was your favorite section of ECE 272? Why? 60 ECE 272 Manual c 2015 Oregon State University Appendix A MachXO2 System Overview 61 APPENDIX A. MACHXO2 SYSTEM OVERVIEW A.1 System Overview The MachXO2 breakout board is an easy-to-use platform for evaluating and designing with the Lattice MachXO2 ultra-low power FPGA. The recommended development software is the Diamond Programmer available free of charge from Lattice. This section will cover the specifics of the board. Further information about the MachXO2 chip or the Lattice Diamond software can be found on the Lattice website. A.2 Parts of the Logic Board The various parts of the MachXO2 board are: I/ O Connectors, Power and Clock Connectors, LEDS, a 60 hole Prototyping Area, the USB Connector and the Programming Connection. Figure A.1 highlights these parts. Figure A.1: MachXO2 Top Side 62 ECE 272 Manual c 2015 Oregon State University A.3. I/O CONNECTORS A.3 I/O Connectors A good rule of thumb when using the I/ O ports on the MachXO2 breakout board and any other system is that, if you do not understand it, do some research. Do not use it until you do understand it. The MachXO2 board can be damaged by actions that are hasty or ignorant. Figure A.2: I/O Connections c 2015 Oregon State University ECE 272 Manual 63 APPENDIX A. MACHXO2 SYSTEM OVERVIEW A.4 Programming Interface and LED Array Figure A.3: Programming Pins and LED Array A.4.1 USB Programming and Debug Interface The USB mini-B socket of the Breakout Board serves as the programming and debug interface. For JTAG programming, a preprogrammed USB PHY peripheral controller is provided on the Breakout Board to serve as the programming interface to the MachXO2 FPGA. Programming requires the Lattice Diamond or ispVM System software. A.4.2 Bypassing the USB programming Interface The USB programming interface circuit (USB Programming and Debug Interface section) may be optionally bypassed by removing the 0 ohm resistors: R5, R6, R7, R8. Header landing J1 provides JTAG signal access for jumper wires or a 1x8 pin header. A.4.3 LEDs A green LED (D9) is used to indicate USB 5v power. Eight red LEDs are driven by I/O pins of the Mach XO2. The red LEDs are active low. 64 ECE 272 Manual c 2015 Oregon State University A.5. POWER SUPPLY A.5 Power Supply When powered from a USB cable, the 3.3V and 1.2V power supply rails are converted from the 5V line on the USB interface. A.5.1 Test Points There are three test points for checking the voltae levels on the MachXO2 board: TP1: +3.3V TP2: +1.2V TP3: GND A.5.2 Applying External Power It is possible to power the breakbout board from a source besides the USB input, but it is not recommended. The best method is to apply a regulated 5V power source to the USB connector. Your external power source must be regulated to prevent damage to the MachXO2 board. A.5.3 Auxiliary Power Output The 3.3V, 1.2V, and GND pins on the MachXO2 board to provide power to external devices. The on board voltage regulators are capable of supplying a maximum current of 1A. Exceeding the specifications of the regulators can cause them to fail. Read the datasheet for a regulator before attaching higher current devices. c 2015 Oregon State University ECE 272 Manual 65 APPENDIX A. MACHXO2 SYSTEM OVERVIEW 66 ECE 272 Manual c 2015 Oregon State University Appendix B Schematics 67 APPENDIX B. SCHEMATICS B.1 MachXO2 Block Diagram Figure B.1: The Digital Logic Board Schematic 68 ECE 272 Manual c 2015 Oregon State University B.2. USB INTERFACE TO JTAG B.2 USB Interface to JTAG Figure B.2: Power Supplies Schematic c 2015 Oregon State University ECE 272 Manual 69 APPENDIX B. SCHEMATICS B.3 FPGA Figure B.3: FPGA Schematic 70 ECE 272 Manual c 2015 Oregon State University B.4. FPGA (CONT.) B.4 FPGA (cont.) Figure B.4: FPGA Schematic c 2015 Oregon State University ECE 272 Manual 71 APPENDIX B. SCHEMATICS B.5 Power and LEDs Figure B.5: Power and LED Schematic 72 ECE 272 Manual c 2015 Oregon State University B.6. 4-DIGIT SEVEN SEGMENT DISPLAY BOARD B.6 4-digit Seven Segment Display Board Figure B.6: 4 digit Seven Segment Display Board c 2015 Oregon State University ECE 272 Manual 73 APPENDIX B. SCHEMATICS B.7 Push Button Board Figure B.7: Push Button Board Schematic 74 ECE 272 Manual c 2015 Oregon State University Appendix C Silk Screens and Pinouts 75 APPENDIX C. SILK SCREENS AND PINOUTS This appendix has all the silk screens and pinouts used in this course. C.1 MachXO2 Figure C.1: The MachXO2 Silkscreen C.2 USB Buck Boost Converter Figure C.2: The USB Buck Boost Silkscreen 76 ECE 272 Manual c 2015 Oregon State University C.3. 4-DIGIT SEVEN SEGMENT DISPLAY BOARD C.3 4-digit Seven Segment Display Board Figure C.3: The top silkscreen Figure C.4: The bottom silkscreen c 2015 Oregon State University ECE 272 Manual 77 APPENDIX C. SILK SCREENS AND PINOUTS C.4 Push Button Board Figure C.5: The Push Button Board Silkscreen 78 ECE 272 Manual c 2015 Oregon State University Appendix D Parts and Suppliers 79 APPENDIX D. PARTS AND SUPPLIERS D.1 Parts List Board MachXO2 Breakout USB Buck Boost 4-digit Seven Segment Push Button Qty. 1 5 1 1 1 1 14 2 1 8 8 Description MachXO2 2 x5 Male Header .1” USB Buck Boost Converter 1 x 4 Female Header .1” Display Board 4 digit 7 Segment LED, Yellow, CA 1/8 Watt Resistors Single Row Male Header .1” 2 x 5 Male Header .1” Push Button Board 1N4148 Diode Tactile Switch 6x6mm Single Row Male Header .1” Ref. Fig. Supplier Digi-Key Supplier # 220-1518-ND TekBots Digi-key TekBots Digi-Key Mouser usb pwr.0 S7002-ND 4digit.0 160-1546-5-ND 299-XXX-RC Jameco 2076826 TekBots Digi-Key Mouser Jameco 8pushbtn.0 568-1360-1-ND 101-06610EV 2076826 A B L5 R1-R9, R23, R27-R29 C E D A D11-D17 S5-S12 F G D Figure D.1: Use these figures to determine which parts to use. D.2 Suppliers List Digi-Key Mouser Electronics TekBots Jameco Electronics 80 701 Brooks Ave. South Thief River Falls, MN 56701-0677 (800) 344-4539 http://www.digikey.com 1000 N. Main Street Mansfield, TX 76063 (800) 346-6873 http://www.mouser.com 1110 Kelley Engineering Center Oregon State University Corvallis, OR 97331 http://eecs.oregonstate.edu/tekbots 1355 Shoreway Rd Belmont, CA 94002 (800) 831-4242 http://www.jameco.com ECE 272 Manual c 2015 Oregon State University