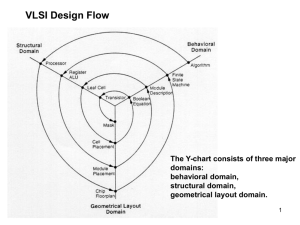

VLSI Design – 1

advertisement

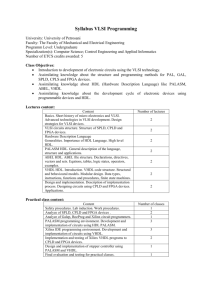

VLSI Design – 1 Introduction to VLSI Design Styles Professor Yusuf Leblebici Microelectronic Systems Laboratory (LSM) yusuf.leblebici@epfl.ch 1 Main Challenge is Complexity ! Remember the key message from our previous lecture: We will need efficient design approaches and methodologies to deal with the very high complexity of integrated systems. 2 Structured Design Principles Hierarchy: “Divide and conquer” technique involves dividing a module into submodules and then repeating this operation on the sub-modules until the complexity of the smaller parts becomes manageable. Regularity: The hierarchical decomposition of a large system should result in not only simple, but also similar blocks, as much as possible. Regularity usually reduces the number of different modules that need to be designed and verified, at all levels of abstraction. Modularity: The various functional blocks which make up the larger system must have well-defined functions and interfaces. Locality: 3 Internal details remain at the local level. The concept of locality also ensures that connections are mostly between neighboring modules, avoiding long-distance connections as much as possible. Structured Design Decomposition of a complex design into hierarchical, regular components. 4 Structured Design Further decomposition... 5 Resulting in blocks with manageable complexity, that can be designed individually. VLSI Design Styles FPGA 6 Full Custom Design Following the partitioning, the transistor level design of the building block is generated and simulated. The example shows a 1-bit full-adder schematic and its SPICE simulation results. 7 Full Custom Design After the initial transistor level schematic design is completed and verified, work begins on the full custom mask layouts of the cells. Most regular structures are built with a relatively small number of elementary components. The three blocks shown above are the only blocks required for a typical fast adder. Special care is given to ensure the modularity and regularity of the structure. 8 Full Custom Design In full-custom style, the designer has many degrees of freedom to optimize a circuit design: • Adjust individual transistor dimensions (channel width, channel length, aspect ratio, etc.) to satisfy: •DC specifications (voltage levels, switching thresholds) •Transient specifications (delay times, rise- and fall-times) • Freely choose the most appropriate topology (placement and routing) for each circuit block. • Decide for the interconnection strategy between neighboring blocks. • Decide for the global distribution of power, ground and clock. 9 Full Custom Design 10 Full Custom Design 11 Full Custom Design Flow 12 Full Custom Design The main objective of full custom design is to ensure fine-grained regularity and modularity. 13 Full Custom Design A carefully crafted full custom block can be placed both along the X and Y axis to form an interconnected two-dimensional array. Example: Data-path cells 14 Full Custom SRAM Cell Design 15 Mapping the Design into Layout Manual full-custom design can be very challenging and time consuming, especially if the low level regularity is not well defined ! 16 Design Hierarchy 4-input logic gate Flip-Flop 17 Design Hierarchy 4-bit register 18 Design Hierarchy 19 Design Hierarchy 20 Full Custom Design Full-custom design style allows the designer to have complete control over all aspects of the design. Potentially achievable: Highest possible performance (speed) Smallest silicon area Lowest power dissipation However, full-custom design requires extensive experience, and the design time can be very long !! 21 VLSI Design Styles FPGA 22 HDL Design 1980’s Hardware Description Languages (HDL) were conceived to facilitate the information exchange between design groups. 1990’s The increasing computation power led to the introduction of logic synthesizers that can translate the description in HDL into a synthesized gate-level net-list of the design. 2000’s Modern synthesis algorithms can optimize a digital design and explore different alternatives to identify the design that best meets the requirements. 23 HDL Design Modern hardware description languages allow structural descriptions that basically determine all interconnections between well-defined blocks: adder: component adder port map (a,b,ci,co,s); as well as purely behavioral descriptions like: sum <= a + b - c; The synthesizer is responsible for converting the behavioral description into an optimized design. 24 HDL Design The design problem is divided into blocks and sub blocks. A separate description is entered for each block. 25 HDL Design This is the main window of the Synopsys HDL compiler. At this stage the VHDL files have been read into the program. 26 HDL Design This is the cell “one-bit” that describes a one-bit full adder. The synthesizer was able to map the HDL code definition to a gate level description. 27 HDL Design The design is completely synthesized and mapped into the target technology. The logic gates have one-to-one equivalents as standard cells in the target technology. 28 Standard Cells AND 29 DFF INV XOR Standard Cells Each standard cell is pre-designed, with: Same cell height for all elements in the library Horizontal PWR and GND lines at the top and at the bottom Fixed pin locations (inputs and outputs) 30 Standard Cells 31 Standard Cells “routing” between the cells completed in the channel 32 Standard Cells 33 Standard Cells 34 Standard Cells 35 Standard Cells Rows of standard cells with routing channels between them Memory array 36 Standard Cells 37 Automatic Placement of Cells 38 Automatic Routing between Cells Close-up detail in Silicon Ensemble: 39 VLSI Design Styles FPGA 40 Mask Gate Array 41 Mask Gate Array Before customization 42 Mask Gate Array After customization (metal lines) 43 VLSI Design Styles FPGA 44 Field Programmable Gate Array 45 Field Programmable Gate Array 46 Field Programmable Gate Array Internal structure of a CLB 47 Field Programmable Gate Array 48 49 50 51 52