FLIP-FLOPS

advertisement

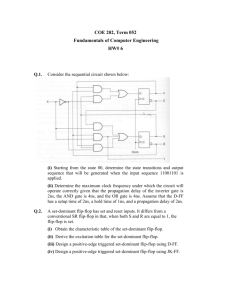

2013.04.14. DIGITAL TECHNICS II Dr. Bálint Pődör Óbuda University, Microelectronics and Technology Institute 3. LECTURE: ELEMENTARY SEQUENTIAL CIRCUITS: FLIP-FLOPS, PART 2 1st year BSc course 2nd (Spring) term 2012/2013 1 FLIP-FLOPS: PART 2 1. Flip-flops (RS, JK, and T) revision and emphasis 2. D (delay, data) and D-G (gated D) flip-flop 3. Flip-flops in practice 4. Mutual transformation of flip flops 2 1 2013.04.14. FLIP-FLOPS The most important flip-flops are the following: R-S (or S-R) flip-flop J-K flip-flop T flip-flop D-G flip-flop D flip-flop All flip-flops listed above can function in synchronous or clocked mode, the R-S and D flip-flops can operate in asynchronous mode too. The behaviour of a particular type can be described by truth/characteristic table and the characteristic equation, which gives the next output in terms of the input control signals and the current output. OPERATION OF FLIP-FLOPS -The change of state of asynchronous flip-flops occurs directly as a response to the change of the input/control variable(s), after the appropriate time delay of the circuit. -The change of state of synchronous (clock controlled) flipflops occurs only when the synchronizing signal (clock) arrives tot heir appropriate input. 4 2 2013.04.14. FLIP-FLOPS: STATIC AND DYNAMIC CONTROL The control of flip-flops can be either static or dynamic. Static: appropriate logic 0 and/or 1 levels should be applied to the static control inputs to initiate the state changes. Dynamic: the change of state of the flip-flop occurs due the change in the appropriate direction (10 or 01 transition) of the signal applied to the dynamic control input (edgetriggered). 5 R-S FLIP-FLOP: STATE TABLE AND STATE TRANSITION GRAPH SR Qn 0 1 Qn+1 00 01 11 10 ————————— 0 0 X 1 ————————— 1 0 X 1 ————————— Qn+1 _ = S + R Qn 0X X0 10 0 1 01 No oscillation occurs in any of the columns, therefore operation can be asynchronous or synchronous. (Red: stable states.) 6 3 2013.04.14. THE S-R (SET-RESET) FLIP-FLOP: TIMING BEHAVIOUR The S-R flip-flop is an active high (positive logic) device. In the NOR gate realization for the logically not defined S=R=1 input the output of both NOR gates is forced to 0 state. In this case the implicite condition of having complementary states in the output is not fulllfilled. J-K FLIP-FLOP: STATE TABLE AND STATE TRANSITION GRAPH Qn+1 JK Qn 0 1 00 01 11 10 ————————— 0 0 1 1 ————————— 1 0 0 1 ————————— JK 0X X0 1X 0 1 X1 No stable state exist in the JK= 1 column. The JK FF can only be operated as a synchronous circuit. Cannot operate without gating/clocking signal. Qn+1 _ _ _ n n =JQ +KQ +JK 8 4 2013.04.14. T FLIP-FLOP: STATE TABLE AND STATE TRANSITION GRAPH Qn+1 T Qn 0 1 0 1 ————— 0 1 ————— 1 0 ————— _ _ n+1 n Q = T Q + T Qn = T Qn T 0 0 1 0 1 1 No stable state exist in the T = 1 column. The T flip-flop can only be a synchronous sequential network. 9 D FLIP-FLOP (1) The state of the Q output of the D (DELAY) flip-flop Q in the next, (n+1)-th state will be equal to the state of the D control input in the pevious, nth state: Qn+1 = Dn 10 5 2013.04.14. D FLIP-FLOP (2) Truth table and characteristic equation n-th (n+1)-th state Qn+1 = D D Qn Qn+1 ———————— 0 0 0 0 1 0 1 0 1 1 1 1 In fact the state in the (n+1)-th state in fac t will nt depend on what was the state of the FF in the n-th state! The D flip-flop does not remember its previous stater 11 D FLIP-FLOP: STATE TABLE AND STATE TRANSITION DIAGRAM D Qn 0 1 Qn+1 0 1 ————— 0 1 ————— 0 1 ————— D 0 Characteristic equation: 1 1 0 1 0 Qn+1 = D 12 6 2013.04.14. A D FLIP-FLOP (3) -The D flip-flop is mostly used to as a component in storage registers. -E.g.to store the value displayed by a digital instruments, till the value of the new reading arrives. 13 D FLIP-FLOP WITH CLOCK Operation of D (DELAY) flip-flop with synchronizing clock. If there is no clock signal (C=0) the output does not change (Qn = Qn-1), if there is a clock signal (C=1) the output will take the actual value of the input, i.e. Q n = D. 14 7 2013.04.14. GATED D FLIP-FLOP Qn+1 G G Qn 0 0 1 0 1 1 1 0 D D _ Qn+1 = D G + G Qn + D Qn 3rd loop: hazard elimination Operation can be asynchronous or synchronous. TIME DIAGRAM OF GATED FLIP-FLOP 16 8 2013.04.14. CHARACTERISTIC EQUATIONS OF FLIP-FLOPS: A SUMMARY T _ = S + R Qn _ _ _ n+1 n n Q =JQ +KQ +JK _ _ Qn+1 = T Qn + T Qn = T Qn D Qn+1 = Dn D-G Qn+1 Qn+1 RS JK _ = D G +G Qn + D Qn Note: The third terms in the equation of JK and D-G flip-flops serve for the elimination of race hazards FLIP-FLOPS IN PRACTICE 18 9 2013.04.14. NOTES ON HISTORY The first electronic flip-flop (bistable circuit) was invented in 1919 by W. Eccles and F. W. Jordan (Eccles-Jordan trigger circuit), and consisted of two active elements (radio-tubes). The name flip-flop was later derived from the sound produced on a speaker connected with one of the backcoupled amplifiers output during the trigger process within the circuit. NOTES ON HISTORY William Henry Eccles and Frank Wilfred Jordan, Improvements in logic relays British patent number: GB 148582 (filed: 21 June 1918; published: 5 August 1920). W. H. Eccles and F. W. Jordan (19 September 1919) "A trigger relay utilizing three-electrode thermionic vacuum tubes," The Electrician, vol. 83, page 298. Reprinted in: Radio Review, vol. 1, no. 3, pages 143–146 (December 1919). 10 2013.04.14. _ THE BASIC RS FLIP-FLOP RS Q Q Eccles-Jordan circuit with transistors L L no change L H H L H L L H H H L L Q • • T1 • R • +Ucc _ Q T2 S NOR gate FLIP-FLOPS: ELECTRONICS Construction of a bistable flip-flop from two-transistor amplifying stages. Eccles-Jordan circuit with transistors. In practice, flip-flops made of discrete transistors are rarely used today. Being constructed on the basis of different types of integrated circuits, such as timer 555 (integrated circuit most22 commonly used for this purpose). 11 2013.04.14. FLIP-FLOPS: ELECTRONICS Bistable flip-flop with driving transistors (setting resetting inputs). This is the classical circuit with transistor amplifying stages T1, T2, with driving transistors Ta1, Ta2. The circuit has two outputs (main, Uq, complementary, /Uq) and two driving inputs (setting and resetting). If Us >0.65 V) Ta1 is switched (saturating), T2 is blocked (cutoff), T1 is switched, Ta2 is blocked, Uq UCC . 23 MOS version: six-transistor SRAM cell. D FLIP-FLOP IN PRACTICE: EDGE-TRIGGERED D FLIP-FLOP Logic structure of edge-triggered D flip-flop (logic diagram of type 7474). Auxiliary circuitry: asynchronous CLEAR and PRESET 12 2013.04.14. MASTER SLAVE J-K FLIP-FLOP MASTER-SLAVE D FLIP-FLOP: LOGIC DIAGRAM Auxiliary circuitry: asynchronous CLEAR and PRESET 13 2013.04.14. MASTER-SLAVE D FLIP-FLOP TIME DIAGRAM MSI CIRCUIT EXAMPLE (1) Vcc 14 13 12 D 11 10 CLR Q D >CK #Q 2 3 8 CLR Q >CK #Q PR 1 9 PR 4 5 6 7 GND Two independent D flip-flops in one package 28 14 2013.04.14. MSI CIRCUIT EXAMPLE (2) Vcc 20 1 19 18 17 16 15 14 13 12 D Q D Q D Q D Q >CK >CK >CK >CK CLR CLR CLR CLR CLR >CK CLR >CK CLR >CK CLR >CK D Q D Q D Q D Q 2 3 4 5 6 7 8 9 11 10 GND Eight D FFs with common CLK and CLEAR in one package: register 29 SETUP AND HOLD TIMES Cannot ignore effect of propagation delay. Need to worry about critical timing region. Setup time: minimum time that the signal D must be stable prior to the edge of the clock. Hold time: minimum time that the signal must be stable after the edge of the clock. 15 2013.04.14. CMOS D FLIP-FLOP • CMOS technology allows a very different approach to flip-flop design and construction. Instead of using logic gates to connect the clock signal to the master and slave sections of the flip-flop, a CMOS flip-flop uses transmission gates to control the data connections. MUTUAL TRANSFORMATONS OF FLIP-FLOPS Any flip-flop can be implemented on the basis of any other flip-flop. Functional diagram: from the input control(s) of the flip-flop to be implemented a combinational circuit produces the signals necessary to drive the implementing flip-flop’s inputs. The output (state bit) is appropriately fed back to the input of the whole system. 32 16 2013.04.14. CONVERSION OF FLIP-FLOPS Combinational circuit implementing flip-flop y X CC Z FF y Flip-flop to be implemented Clock Each flip-flop type can be realized and implemented on the basis of any other type. D FLIP-FLOP REALIZATIONS D J Q CLK CLK CLK K _ Q 1 R Q CLK D 1 S _ Q D J K Qn+1 ¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯ 0 0 1 0 1 1 0 1 D S R Qn+1 ¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯ 0 0 1 0 1 1 0 1 The D control excludes the occurrence of R =S = 1 excitation 17 2013.04.14. T FLIP-FLOP REALIZATIONS T J Q CLK & T K _ Q R Q CLK S & _ Q T 0 1 J 0 1 K 0 1 Qn+1 Qn Qn T 0 0 Qn 0 1 S 0 0 R 0 0 1 0 1 0 1 1 0 1 Qn+1 Qn Qn _ 1(Qn) _ 0(Qn) IMPLEMENTATION OF T FLIP-FLOP WITH RS FLIP-FLOP: SYNTHESIS OF THE FEEDBACK NETWORK Qn+1 S Qn Qn 0-0 1-1 T 0-1 1-0 R T 0 x 1 0 _ S = T Qn Qn T x 0 0 1 R = T Qn 18 2013.04.14. T FLIP-FLOP ON THE BASIS OF D FLIP-FLOP _ _ n D = T Q + T Qn & T 1 D Q CLK & _ Q Clock Note that T flip-flops are not available in the CMOS and TTL logic families. IMPLEMENTATION OF JK FLIP-FLOP WITH D FLIP-FLOP J & 1 K D Q • CLK & _ Q • Clock Note that D flip-flops are available in some PLA circuits. 19 2013.04.14. JK FLIP-FLOP BUILT WITH RS FLIP-FLOP J & S K & Clock Q • R = K Qn CLK R _ S = J Qn _ Q • The feedback ensures that the not allowed R=S=1 condition can not occur. ÁLTALÁNOS KÖVETKEZTETÉSEK ÉS ÖSSZEFOGLALÁS Az elemi sorrendi hálózatok, azaz a flip-flopok megismert tulajdonságait összefoglalva a szinkron sorrendi hálózatokra vonatkozóan is levonhatunk néhány általános következtetést. 40 20 2013.04.14. FLIP-FLOPS: SUMMARY T _ Qn+1 = S + R Qn _ _ _ n+1 n n Q =JQ +KQ +JK _ _ n+1 n Q = T Q + T Qn = T Qn D Qn+1 = Dn D-G _ Qn+1 = D G +G Qn + D Qn RS JK In the case of JK és D-G flip-flops the third terms ensure hazard free operation. SUMMARY OF FLIP-FLOP TYPES S=R=1 not allowed Most versatile type Most simple Gated (DG) Copies input to output Complements output if activated 21 2013.04.14. STATE TRANSITION DIAGRAMS: SUMMARY SR flip-flop JK flip-flop D flip-flop T flip-flop 43 EXCITATION TABLES OF FLIP-FLOPS Qn Qn+1 R S J K D T ¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯¯ 0 0 x 0 0 X 0 0 0 1 0 1 1 X 1 1 1 0 1 0 X 1 0 1 1 1 0 X X 0 1 0 The excitation table lists the required inputs for a given change of state, i.e. the input conditions that will cause the transition form a given present state to the next state. The excitation table is required and is used in the design process. 22 2013.04.14. IMPLEMENTATION OF FLIP-FLOPS: SOME PRACTCAL ASPECTS • In the popular CMOS and TTL logic families T flip-flop is not available. It should be build on the basis of an other type of flip-flop. • TTL, CMOS: basically JK and D flip-flops. • PLA, PLD: only D flip-flop (!), the JK flip-flop should be implemented by additional circuitry. • RS flip-flop: in TTL it is based on NAND gates, in CMOS it is based on NOR gates. APPLICATION OF FLIP-FLOPS: SOME PRACTICAL ASPECTS • T flip-flops are well suited for straightforward binary counters. But may yield worst gate and pin counts. • No reason to choose RS over JK FFs: it is a proper subset of JK. RS FFs don’t exist anyway. Tend to yield best choice for packaged logic where gate count is the key. • D FFs yield simplest design procedure. In many cases give the best pin count. D storage devices are very transistor efficient in VLSI. Best choice where area/pin count is the key. 23 2013.04.14. SUMMARY OF SOME ASPECTS OF FLIP-FLOPS Development of D flip-flop Level-sensitive is used in custom ICs Edge-triggered uesd in programmable logic deices Good choice for data storage register Historically JK flip-flop was popular but noe never used Similar to RS but wit 11 used to toggle output Good in days of TTL/SSI (more complex input function) Not a good choice for PALs/PLAs as it requires two inputs Can always be implemented using D flip-flops Preset and clear inputs are highly desirable on flip-flops Used at start-up or to reset systems to a known state SUMMARY OF SOME ASPECTS OF FLIP-FLOPS RS clocked latch: Used as storage element in narrow width clocked systems Its use is not recommended! However fundamental building block of other flip-flop types JK flip-flop: Versatile building block Can be used to implement D and T flip-flops Usually requires least amount of logic to implement f(In, Q) But has two inputs with increase wiring complexity D flip-flops: Minimizes wires, much preferred in VLSI technologies Simplest design technique Best choice for storage registers T flip-flops: Don’t really exist, constructed from JK flip-flops Usually best choice for implementing counters 24