DSP System Design and Implementations - E-GRID

advertisement

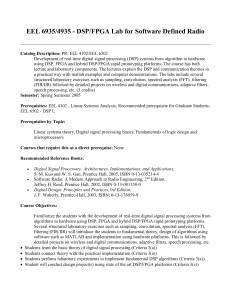

Department of Electrical Engineering SHORT COURSE PROGRAM August 2005 www.engr.sjsu.edu/eeshortcourse Courses Offered (click to select): DSP System Design and Implementations Wireless Transmitters FPGA DSP System Design Embedded Systems and Embedded FPGAs High-Speed Data Networks Registration Form Career-Advancement Short Courses with Labs Department of Electrical Engineering August Technology Series • • • • • Theoretical Aspects Hands-on Experience For working professionals Preparation for Tomorrow Excellent value; practical; timely topics 2 Choices the week of August 9-12: Digital Signal Processing -- 4-day class with labs: DSP System Design and Implementation Overview: Today’s technology provides DSP processors that can be easily used to design very sophisticated products for instrumentation, control systems, communications, and wireless systems. This course presents DSP system design and implementation using programmable signal processors. Handson laboratory exercises are used to present the design and implementation aspects, using hardware and software tools for system implementation. The 5 laboratory sessions follow the lectures, where participants will apply system design concepts by designing, implementing, debugging and evaluating DSP schemes. Embedded Systems and Embedded FPGAs Overview: This short course is designed to introduce the fundamentals of embedded systems, and embedded FPGA design methodology. The objectives are to give an overview of the technology, the fundamentals and advanced issues, and hand-on experience with embedded FPGAs. The Laboratory modules provide hands-on experience with configuring the processor core, developing IP with VHDL, writing driver, system integration and test routines. Students will be exposed to a learning experience balanced between fundamental and advanced issues, theoretical concepts to hand-on experiments that will help them progress from novice to expert within a short time. Digital System Design -- 4-day class with labs: FPGA DSP System Design Wireless -- 4-day class with labs: Wireless Transmitters Overview: There are a number of transmitter architectures developed to satisfy the linearity requirements of modulation techniques employed in short- and long-range communication applications. This exceptional course introduces the modulation techniques and wireless standards, and compares the RF properties and performance of the CMOS, SiGe and GaAs technologies. The laboratory sessions of the course involve using the MATLAB/VerilogA simulators for behavioral characterization of transmitters by generating baseband signals of constant envelope, varying envelope communication systems, and applying transmitter nonlinearities. Throughout the lab projects, one will be able to understand and characterize the mask, the bandwidth and the peak to average ratio of communication signals and measure the distortion and spectral regrowth caused by transmitters. Come to San Jose State! Easy access: class starts before most students arrive on campus, so parking in the 7th Street garage is a snap! Cost: $995 per course (includes student notebook, lunches and refreshments, CDs with class notes and problem solutions for certain classes) Review the full course Flyer: www.e-grid.net/docs/sjsu0508.pdf for course overviews, prerequisites, instructor profiles, registration, map JULY 2005 3 Choices the week of August 16-19: Digital System Design -- 4-day class with labs: Overview: This course provides an in-depth and state-of-theart coverage of the design and FPGA-based implementation of high-performance DSP systems. After presenting FPGA architectures and design tools by Xilinx and Altera, several hands-on design labs on DSP, digital communications and video/imaging will be covered, including FFT, FIR filters, error detection/correction circuits, modem, color space converter, and DWT (Discrete Wavelet Transform). Contents: Basic DSP/Communication theory, FPGA architecture/design tools, HDL (VHDL and Verilog), DSP-specific arithmetic circuits, hardware design of digital filters, FFT circuits, error detection & correction circuits, encryption/decryption circuits, and video/imaging circuits. Networking Engineering -- 4-day class with labs: High-Speed Data Networks Overview: This course covers architectures, delay modeling, and the latest innovations in broadband computer-communication networks – detailed studies on design and analysis of high-speed switches and routers, design of input/output interfaces for fast routers with quality-of-service provisions, design of multicast switches and networks, delay modeling, bandwidth allocations and congestion control methods for broadband networks, voice compression for higher data rates, voice over IP, and the latest techniques in wireless communication systems. The course starts with a brief overview of high-speed networks and architectures and continues with the design of switching systems and routers and router interfaces with quality-of-service provisioning. The course then addresses delay analysis and congestion control techniques, and then targets some of the most demanded topics such as the design of multicast high-speed networks, voice over IP, and wireless high-speed networks. The labs are hands-on experiments in Computer networking. Visit us at w w w . e - G R I D . n e t Page 7 Message from the Chair of the Electrical Engineering Department It is my pleasure to introduce to you the second set of short courses offered by the Electrical Engineering department of San Jose State University during this winter for working professionals who want to keep up with rapidly changing technology. We have offered several individual short courses before, however, starting in Spring 2004 we have a comprehensive program aimed at supporting the industry to address its training requirements. The second set of courses will be offered in August 2005. Five different courses will be offered ranging from DSP, Wireless Transmitters to Network Technology. The faculty members of the Electrical Engineering department will offer the courses. These courses provide an engineer with hands-on experience in addition to the theory. Selected courses offered in this program are based on our feedback from industry leaders. If your company has a special need for a course tailored to fit a particular engineering requirement, we will be glad to hear from you. I trust that this Short Course program will serve successfully as an adjunct to the important industry/ university relation that make the Silicon Valley thrive and maintain its success in global competition. James Freeman Chair – Department of Electrical Engineering San Jose State University D DIIG GIITTA ALL SSIIG GN NA ALL PPR RO OC CEESSSSIIN NG G DSP System Design and Implementations Aug. 9-12, 2005 8:30am – 4:30pm Course Overview Today’s technology provides DSP processors that can be easily used to design sophisticated products for instrumentation, control systems, communication and wireless systems. This course presents DSP system design and implementations using programmable signal processors. Hand-on laboratory exercises are used to present the aspects of design and implementation. Use of hardware and software tools for the system implementations using digital signal processors is part of the course. The laboratory sessions follow the lectures where the participants will apply system design concepts by designing, implementing, debugging and evaluating DSP schemes. Course Highlights ¾ Fundamentals of DSP System Design and Implementations ¾ DSP Implementation Issues including Quantization, Truncation/ Rounding, and Overflow/ Saturation ¾ Tools for DSP System Analysis and Design ¾ DSP Processors ¾ Code Composer Studio for DSP System Development ¾ A DSP Development System (DSK5416) ¾ Implementations examples including FIR Filters, IIR Filters, Interpolation Filters, Decimation Filters, PID Controllers, Adaptive Filters, and Nonlinear Operations ¾ Real-time DSP Implementations ¾ TheMcBSP-CODEC Interface Programming ¾ FFT Implementations Who should attend? Engineers and managers interested in evaluating digital signal processors and learning DSP system design techniques will benefit from the course. Prerequisites Basic undergraduate level background in linear systems, preferably in digital signal processing, is needed to understand the material covered in the course. A background in basic computer architecture will be helpful. A knowledge of computer1 programming, preferably at the assembly language level is desirable though not absolutely required. Course Materials Course Binder: with lecture notes and other related materials. CD: with course notes and solutions to the lab exercises Text: Singh, A. and Srinivasan, S., Digital Signal Processing Implementations Using DSP Microprocessors, Thomson Learning (Brooks/Cole), 2004. Optional Course Material: DSK5416 Development Board with CCS Development Software available from TI distributors. Laboratory There are 5 laboratory sessions to provide hands-on design and implementation experience. The DSP development stations equipped with development boards, MATLAB and the Code Composer Studio (CCS) development software will be used for the laboratory exercises. Course Instructor: Professor Avtar Singh Dr. Singh is a professor in the Electrical Engineering Department of San Jose State University. He has M.Tech from Indian Institute of Technology, and ME and Ph.D. from the City University of New York. He has worked in National Semiconductor, Anderson Jacobson, Vivix Corporation, and NASA Ames Research Center in the areas of Microprocessors, Data Communication, Biomedical Instrumentation, and Signal Processing. He has developed and taught Electrical Engineering courses at San Jose State University since 1987. He has published several papers in journals and conferences and eleven books including a recently published fourth edition of a textbook on microprocessors. His latest book is a textbook on Digital Signal Processing Implementations. He has served, for many years, as publicity, and publication chair for the Asilomar Conference on Signals, Systems and Computers. Daily Schedule Day 1 Introduction to DSP System Design and Implementations ¾ A Digital signal Processing System ¾ The Sampling Process Digital Signal Sequences ¾ Linear Time Invariant Systems ¾ Frequency Response and Digital Filters ¾ DFT and FFT ¾ Decimation and Interpolation ¾ Computational Accuracy in DSP Implementations ¾ Quantization, Truncation/ Rounding, Overflow/ Saturation Issues for Implementations ¾ Tools for DSP System Analysis and Design Lab 1: Using MATLAB for DSP System Analysis and Design Day 2 DSP Processors and System Development Tools ¾ Architectures for DSP Operations and Algorithms ¾ Commercial DSP Processors ¾ Architectural Analysis of the TMS320C54xx Signal Processors ¾ The Instruction Set and the Addressing Modes ¾ Developing Assembly/C++ Code for an Applications ¾ DSP Implementation Tools: Compiler, Assembler, Linker, Simulator, and Debugger ¾ Code Composer Studio for DSP System Development ¾ A DSP Development System (DSK5416) Lab 2: Using TMS320C5000 Software/ Hardware Development Tools Day 3 DSP Algorithm Implementations ¾ Q-Notation ¾ Implementations examples including FIR Filters, IIR Filters, Interpolation Filters, Decimation Filters, PID Controllers, Adaptive Filters, and Nonlinear Systems ¾ FFT Algorithms ¾ FFT Implementation Issues ¾ Spectrum Analysis Lab 3: Developing Assembly Code for Digital Filters Lab 4: Implementing an FFT Algorithm for Spectrum Analysis Day 4 - Real-time DSP Implementations ¾ ¾ ¾ ¾ ¾ Parallel and Serial A/D and D/A Converters Synchronous Serial Interface A Multi-channel Buffered Serial Port (McBSP) A Serial Analog Interface Circuit (CODEC) The McBSP-CODEC Interface Programming Lab 5: Implementing a Real-time DSP Scheme Fee $995 Location DSP Laboratory, E-386, College of Engineering, Department of Electrical Engineering C CO OM MM MU UN NIIC CA ATTIIO ON N SSY YSSTTEEM MSS Wireless Transmitters Aug. 9-12, 2005 8:30am – 4:30pm Course Overview Power amplifiers play a major role in the overall performance of transmitters. transmitters, there are a number of upconversion transmitter architectures developed to satisfy the linearity requirements of modulation techniques employed in short and long range communication applications. This course introduces modulation techniques and wireless standards, presents different transmitter and power amplifier architectures and also compares the RF properties and performance of the CMOS, SiGe and GaAs technologies. This course helps designers to understand the critical effects and the relationships among linearity, power and spectral efficiencies, output power level and frequency of operation. The laboratory sessions of the course involve using MATLAB/VerilogA simulators for behavioral characterization of transmitters by generating baseband signals of constant envelop and varying envelope communication systems and applying transmitter nonlinearities. Throughout the lab projects, one will be able to understand and characterize the mask, the bandwidth and the peak to average ratio of communication signals and measure the distortion and spectral regrowth caused by transmitters. Course Highlights ¾ Fundamentals of modulation techniques ¾ Overview of wireless standards ¾ Study of transmitter architectures ¾ Study of power amplifier architectures ¾ Characterization of IC technologies ¾ MATLAB/VerilogA simulations Who should attend? Anybody interested in learning and conducting leading edge research in the field of wireless transmitters and understanding the concurrent issues high tech companies are investigating. Prerequisites Basic circuit theory, digital communications and semiconductor physics. Some exposure to IC design. Course Materials Course Binder: with lecture notes and other related materials Recommended Text: to be announced during the lectures Course Instructor: Professor Sotoudeh Hamedi-Hagh Dr. Hamedi-Hagh received his Ph.D. degree in electrical and computer engineering from the University of Toronto, Toronto, ON, Canada in 2004. He has joined the faculty of the Electrical Engineering Department at San Jose State University since January 2005. His areas of research are design of RF, Analog and Mixed-Signal Integrated Circuits and Systems for Wireless, Wireline and Optical Communications using CMOS, SiGe and GaAs technologies. Dr. Hamedi-Hagh developed a new phase shifted (PS) transmitter architecture in 2001, based on the outphasing linearization technique. The PS transmitter operates without mixers and linearly amplifies RF signals to high power levels suitable for long-range communication applications. He has also worked on the design of SiGe A/D converters during his postdoctoral fellowship at the University of Toronto in 2004. He has investigated projects for research and development in industry and academia ranging from the design of three-dimensional sonar and radar systems to the design of CMOS 16-offset differential phase-shift-keying modulator and demodulator for wireline data communications. Dr. Hamedi-Hagh holds a US patent and was the recipient of the best paper award at the 2000 Micronet (a Canadian Network of Centers of Excellence on Microelectronics) annual workshop. He also received the best paper award of the 2004 IEEE International Symposium on Personal, Indoor and Mobile Radio Communications. Daily Schedule Day 1: ¾ Modulation techniques: GMSK, /4QPSK, QPSK ¾ Wireless standards: GSM, EDGE, CDMA ¾ IC technologies: CMOS and SiGe Lab 1 ¾ Characterizing the mask, the bandwidth and the peak to average ratio of constant envelope and varying envelope communication systems using MATLAB Day 2: ¾ Standard power amplifiers: Class A, AB, B, C and D ¾ Switching power amplifiers: Class E and F ¾ Lab2 ¾ Interfacing MATLAB and VerilogA ¾ Modeling standard and switching power amplifiers in VerilogA Day 3 ¾ Conventional transmitter architectures: Direct up conversion with Feedback, Feed forward and Predistortion linearization Lab 3 ¾ Modeling and characterizing conventional transmitters using VerilogA Day 4: ¾ Modern transmitter architectures: Polar and Out phasing Lab 4 ¾ Modeling and characterizing modern transmitters using VerilogA Fee $995 Location College of Engineering, Department of Electrical Engineering at San Jose State University D DIIG GIITTA ALL SSY YSSTTEEM MD DEESSIIG GN N FPGA DSP System Design Aug. 16-19, 2005 8:30am – 4:30pm Course Description and Objective This course provides an in-depth and state-of-the-art coverage on the design and FPGA-based implementation of high-performance DSP systems. After presenting FPGA architectures and design tools by Xilinx and Altera, several hands-on design labs on DSP, digital communications and video/imaging will be covered, including FFT, FIR filter, error detection/correction circuits, modem, color space converter, and DWT (Discrete Wavelet Transform). Course Highlights Basic DSP/ Communication theory, FPGA architecture and design tools, HDL (VHDL and Verilog), DSPspecific arithmetic circuits, Hardware design of digital filters, FFT circuits, error detection & correction circuits, encryption/ decryption circuits, video/ imaging circuits. Who should attend? Engineers and managers working or considering working on DSP, digital (wireless) communications, or video/ imaging areas. DSP engineers not familiar with the FPGA based DSP systems design flow. Prerequisites Basic knowledge of DSP and logic design Course Materials Course Binder: “FPGA DSP System Design” manuscript by Dr. Choo Optional Course Material: Uwe Meyer-Baese, Digital Signal Processing with Field Programmable Gate Array, Springer-Verlag, New York, 2001 (ISBN 3-540-41341-3). Laboratory FPGA based design using Quartus/ISE tools; DSP design using Matlab/Simulink; FIR filter design; Adaptive FIR filter design, FFT circuit design; FEC circuit design; Modem design; DCT & DWT circuit design. Course Instructor: Professor Chang Choo Dr. Choo is currently a Professor of Electrical Engineering at San Jose State University, San Jose, California. He was a Senior Member of the Technical Staff with Altera Corporation for two years from 1999. From 1986 to 1998, he was a Professor of Electrical Engineering at Worcester Polytechnic Institute. He taught and did research on DSP, digital design, computer architecture, and video/imaging. He has over 60 journal and conference publications and 5 patents in these areas. Also, he was a member of Technical Committee with several professional conferences including DSP World/ICSPAT and SPIE. He was a consultant for local companies including National Semiconductor, Innovacom, RealChip Communications, and Philips Semiconductor. Dr. Choo received his PhD in computer and systems engineering from Rensselaer Polytechnic Institute, Troy, New York. Daily Schedule Day 1 ¾ FPGA architecture ¾ HDL ¾ Quartus II & ISE tools, ¾ Matlab/Simulink Day 2 ¾ DSP arithmetic ¾ Basics of digital filters and FFT Design Lab: FIR filter & FFT Day 3 ¾ Basics of digital communications Design Lab: modem, error correction/detection code & encryption/decryption Day 4 ¾ Basics of video/imaging; Design Lab: color space converter, 2D filters, DCT, DWT Fee $ 995 Location College of Engineering, Department of Electrical Engineering D DIIG GIITTA ALL SSY YSSTTEEM MD DEESSIIG GN N Embedded Systems and Embedded FPGAs Aug. 16-19, 2005 8:30am – 4:30pm Course Overview This short course is designed to introduce the fundamentals of embedded system and embedded FPGA design methodology. The objectives are to give an overview of the technology, fundamentals and advanced issues, with hands-on experience with embedded FPGAs. The course is organized into two parts: Embedded system fundamentals, and embedded FPGAs. The first part will address fundamental concepts such as microprocessor architecture, bus functionality/arbitration, memory and I/O, interrupts, instruction set/Assembler/C, real-time operating system (ROS), and drivers in a conventional embedded system. The second part focuses on advanced embedded systems design including embedded FPGA implementation and practice. The Laboratory modules will provide hands-on experience with projects on processor core, developing IP with VHDL, writing drivers, system integration, and test. Students will be exposed to a learning experience balanced between fundamental and advanced issues, theoretical concepts and hands-on experiments that will allow them to progress from novice to expert within a short time. Course Objective Upon completion of this course, students will be able to: ¾ ¾ ¾ ¾ ¾ ¾ ¾ ¾ ¾ Understand the basic issues of embedded system Understand microprocessor architecture and instruction set Understand interrupt driven system Write driver in assembler or C for specific embedded processor Understand the design flow of embedded FPGA Understand software development in EDK environments Write special IO driver Adding IP to hardware design Debugging Who should attend? Hardware/Software engineer who needs to start on an embedded system project in a quick hurry. Prerequisites Students taking this course should have working knowledge of digital circuits and some exposure to C, VHDL, FPGA design methodology, Course Material Course Binder: with lecture notes and laboratory materials. Laboratory Digital Design Lab E389. The lab is equipped with workstations, of both Windows and Linux OS. It supports Synopsys’s design Analyzer and Design Complier and is equipped with Xilinx ISE and EDK Course Instructor: Professor Tri Caohuu Dr Caohuu has his B.Sc., MSEE, Ph.D, in Electrical Engineering and has over 20 years of industrial experience in design and implementation of digital system and project management. He was employed with Bell Northern Research, Control Data and Leigh Systems in Canada. He was Director of R&D of EMC, Ltd., Toronto, Canada from 1981 to 1986. Currently, Dr. Caohuu is Professor and Associate Chair at San Jose State University, Department of Electrical Engineering. He has been with San Jose State University since 1990 and has taught courses in embedded system design, advanced computer architectures, ASIC design, and digital design using VHDL and short courses in HDL-based design methodology. Dr Caohuu’s research interests include computer architecture and reconfigurable architecture, parallel VLSI computation, advanced microprocessor systems, area-time efficient VLSI arrays for digital signal processing, HDL based design methodology and ASIC design. He was a Guest Professor at Darmstadt University, Germany, 1998-99. He served as the General Chairman for the VITC’97 conference at San Jose and was President of Vietnamese Association of Computer Engineering and Technology 2000-02 (VACETS). Daily schedule Day 1 Introduction to Embedded Systems Embedded Computer Systems Overview ¾ Embedded / Real-Time Systems: Definitions and Issues ¾ US Technical Trends ¾ Overview of Embedded Software ¾ Embedded OS ¾ SOC based embedded system Day 2 Embedded System Fundamentals ¾ Microprocessor ¾ Bus functionality/arbitration ¾ Memory and I/O ¾ Interrupts ¾ Instruction Set/Assembler/C ¾ Operating System (OS) ¾ Driver Lab Modules: Conventional Embedded System & IO subsystem Day 3 Embedded FPGA System ¾ Introduction to Embedded FPGA ¾ Trade off between FPGA and Conventional System ¾ Design Considerations ¾ Tool Embedded FPGA Design Architecture ¾ Hardware: • Processor Architecture (PowerPC/Microblaze) • Bus Architecture (OPB/LPB) • Peripheral (EMC, UART, GPIO, etc.) • Custom IP ¾ Software: • OS and Driver • Software Application Day 4 Embedded FPGA Design Flow ¾ Design System Architecture ¾ Custom Driver ¾ Software Application ¾ Integration and Download ¾ Debugging Lab Modules: Embedded FPGA with Xilink EDK NETWORKING ENGINEERING High-Speed Data Networks Aug. 16-19, 2005 8:30am – 4:30pm Course Overview This course covers high-speed architectures, delay modeling, and the latest innovations in broadband computer communication networks. Detailed studies on design and analysis of high-speed switches and routers, design of input/output interfaces for fast routers with quality-of-service provisions, design of multicast switches and networks, delay modeling, bandwidth allocations and congestion control methods for broadband networks, voice compression for higher data rates, voice over IP, and latest techniques in wireless communication systems. Course Highlights The course starts with a brief overview of high-speed networks and architectures that continues toward the design of switching systems, routers and router interfaces with quality-of-service provisioning. The course moves towards the delay analysis and congestion control techniques, and then targets at some most demanded topics such as the design of multicast high-speed networks, voice over IP, and wireless high-speed networks. Who should attend? This course provides a broad study of the computer communication network technology. The course is intended for students, engineers and managers in system R&D and especially for experts in networks who seek understanding of this high-speed computer networking technology for innovation of more powerful systems Prerequisite Elementary Understanding of Computer Networking Course Material Instructor’s Handout Instructor Biography Nader F. Mir, Ph.D. in electrical engineering from Washington University in St. Louis and Associate Professor of Electrical Engineering Department at San Jose State University, CA. He was a research scientist at the Advanced Telecommunications Institute, Stevens Institute of Technology, in New Jersey working on design of advanced telecommunication networks and also was with the Computer and Communications Research Center (CCRC) at Washington University and worked on design and analysis of gigabit switching systems project. His research interests are: analysis of computer communication networks, design and analysis of switching systems, network design for wireless and telecommunication systems, and applications of digital integrated circuits in computer communications. He is a senior member of the IEEE and served as conference Technical Program Committee Member, Steering Committee member, and Session Chair of a number of conferences and published numerous refereed technical papers all in the field of communications and networking. He has published a book in video and communication engineering and another textbook under publications entitled “Data Networks, Design and Analysis”. Dr. Mir is the recipient of several awards including the university teaching recognition award and research excellence award. He is currently the Editor of Journal of Computing and Information Technology and also an associate editor of IEEE Communications Magazine. Daily Schedule Day 1: ¾ Overview of High-Speed Network Architectures • MPLS Wide-Area Networks o Label Stack and Label Distribution o Traffic Engineering • o Architectures of High-Speed LANs Optical Networks and WDM Techniques o IP Over Optical Core Switches o Cross-Connect Wavelength Networks ¾ Design of Switching Systems and Routers • Transmission systems and Multiplexers • Estimation of Link Blocking • Switching Networks o Crossbar Switches o Multistage Switches o Shared-Memory Switches • Non-Blocking Switches • Concentration and Expansion Switches • Increasing Speed of Switches Day 2: ¾ Design of Router Interfaces with Quality-of-Service • Input and Output Port Processors o Packet Fragmentation o Routing Table o Multicast Process o Congestion Controller • Integrated Service Method o Traffic Shaping o Admission Control o Packet Scheduling o Buffer Management • Differentiated Service Method o Diffserv Fields o Traffic Conditioner o Bandwidth Broker ¾ Delay Analysis and Congestion Control • Delay Models at the Node Level • Delay Models at the Network Level • Flow Control at the Link Level • Resource Allocations • General Methods of Congestion Control • TCP Congestion Control • Congestion Avoidance Methods ¾ Design of Multicast High-Speed Networks • Review of Multicast Protocols o Intra-domain Multicast Protocols o Inter-domain Multicast Protocols • Design of Copy-Network/Routing Networks • Hardware Design of Recycling Technique • Design of Multicast Boolean Splitting Algorithm • Design of Multicast Deflection-Routing Networks Day 3: ¾ Voice over IP • Basic IP Telephone System • Digital Voice Sampling and Distortion • Compression Techniques for High-Speed Networks • Limit of Compression • Signaling Protocol for Void o Telephone Numbering o H.323 Protocol o Session Initiation Protocol • Real Time Transport Protocols ¾ Wireless High-Speed Networks • Review of Wireless Fundamentals • Design of Wireless Systems at Link Level o Modulation Techniques o Channel Coding • Wireless Network Topology • 802.11 Standards • Wireless LANs o High-Speed Architectures o MAC Layers • RF-ID Laboratory (1/2 day) ¾ Some Hands-on Experiments in Computer Networking Fee $995 Location College of Engineering, Department of Electrical Engineering at San Jose State University DSP System Design and Implementations (Aug. 9-12, 2005) Wireless Transmitters (Aug. 9-12, 2005) FPGA DSP System Design (Aug. 16-19, 2005) Embedded System and Embedded FPGA (Aug. 16-19, 2005) High-Speed Data Networks (Aug. 16-19, 2005) Each class is $995. (IEEE members discount $50.00 off/course). Add all the course costs together and make the check payable to SJSU and mail registration form to: Short Course Program, Department of Electrical Engineering, San Jose State University, San Jose, CA 95192-0084. [Fax: (408) 924-3925] For more information contact Irma Alarcón at (408) 924-3938, ialarcon@emai.sjsu.edu . IEEE GRID – July, 2005 Email ________________________________ Fax ______________ Phone____________________Amount enclosed_________________ Signature _______________________________________________ City_____________________ State_____________Zip___________ Card #_________________________________Expiry ___________ Address_________________________________________________ Cardholder’s Name _______________________________________ Complete the appropriate section: Check enclosed Name___________________________________________________ P.O. enclosed Charge card Organization/Company_____________________________________ Visa Mastercard Class Choice (check one or more) REGISTRATION FORM SAN FERNANDO STREET *Engineering S J S U HWY-101 N 11TH STREET 10TH STREET 4TH STREET Map and Driving Directions: SAN CARLOS STREET 7th Street Garage 7TH STREET SAN SALVADOR STREET I-280 The Engineering Building is located at the corner of South Seventh Street and East San Fernando Street, San Jose. From U.S. HWY 101: Take Interstate 280, exit at Seventh Street and proceed north to campus. From Interstate 880 South: Take HWY 101 to Interstate 280, exit at Seventh Street and proceed north to campus. From San José Mineta International Airport: Take Guadalupe Parkway (becomes Highway 87) south to I-280 southbound. Exit at Seventh Street. Turn left on Seventh Street to campus. Public Transportation: Transit buses and the light rail line connect to downtown San José and the campus from throughout the county, the airport and the Amtrak/CalTrain San José depot. Call 408-924-7433 for specific routes. Paid Parking is available in the SJSU garage at Seventh and San Salvador Street. For more details visit: http://www.sjsu.edu/about_sjsu/campus_maps/directions/ Contact Information: Program Secretary: Irma Alarcon Telephone: (408) 924-3938 Fax: (408) 924-3925 E-mail: ialarcon@email.sjsu.edu Program Director: Tri Caohuu Telephone: (408) 924-3951 E-mail: caohuut@email.sjsu.edu Department of Electrical Engineering San Jose State University One Washington Square San Jose, California 95192-0084