CHAPTER VIII FINITE STATE MACHINES (FSM)

advertisement

INTRO. TO COMP. ENG.

CHAPTER VIII-1

•CHAPTER VIII

FINITE STATE MACHINES

CHAPTER VIII

FINITE STATE MACHINES (FSM)

R.M. Dansereau; v.1.0

INTRO. TO COMP. ENG.

CHAPTER VIII-2

FINITE STATE MACHINES

•

STATE MACHINES

•STATE MACHINES

-INTRODUCTION

INTRODUCTION

From the previous chapter we can make simple memory elements.

• Latches as well as latches with control signals

• Flip-flops

• Registers

•

The goal now is to use the memory elements to hold the running state of

the machine.

• The state of the machine can be used to perform sequential operations.

• This chapter will discuss how to represent the state of the machine for

design and communication purposes.

R.M. Dansereau; v.1.0

INTRO. TO COMP. ENG.

CHAPTER VIII-3

FINITE STATE MACHINES

•

STATE MACHINES

•STATE MACHINES

-INTRODUCTION

MEALY & MOORE MACHINES

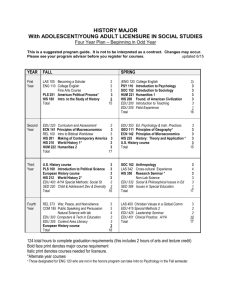

Mealy machine

• Sequential system where

output depends on current

Input

input and state.

Sequential System

Combinational

Logic

Output

Memory

(state)

•

Moore machine

• Sequential system where

output depends only on

current state.

Input

Sequential System

Combinational

Logic

Memory

(state)

R.M. Dansereau; v.1.0

Output

INTRO. TO COMP. ENG.

CHAPTER VIII-4

FINITE STATE MACHINES

•

STATE MACHINES

SYNC. & ASYNC. SYSTEMS

•STATE MACHINES

-INTRODUCTION

-MEALY & MOORE MACH.

Synchronous sequential system

• Behaviour depends on the inputs and outputs at discrete instants of time.

• Flip-flops, registers, and latches that are enabled/controlled with a signal

derived from clock form a synchronous sequential system.

•

Asynchronous sequential system

• Behaviour depends on inputs at any instant of time.

• Latches without control signals behave in an asynchronous manner.

•

The state machines discussed in this chapter will be synchronous

sequential systems (i.e. controlled by a clock)

• This allows us to form timed Boolean functions such as

• N ( t ) = D A ( t + 1 ) where N is the next state of a D flip-flop D A .

R.M. Dansereau; v.1.0

STATE DIAGRAMS

INTRO. TO COMP. ENG.

CHAPTER VIII-5

FINITE STATE MACHINES

•

ELEMENTS OF DIAGRAMS

•STATE MACHINES

-INTRODUCTION

-MEALY & MOORE MACH.

-SYNC. & ASYNC SYSTEMS

A state diagram represents a finite state machine (FSM) and contains

• Circles: represent the machine states

• Labelled with a binary encoded number or S k reflecting state.

• Directed arcs: represent the transitions between states

• Labelled with input/output for that state transition.

a /p

Sk

State

Sj

b /q

Input/Output

R.M. Dansereau; v.1.0

Input:

x ( t ) ∈ { a, b }

Output:

z ( t ) ∈ { p, q }

State:

s ( t ) ∈ { S k, S j }

Initial state:

s ( 0 ) = Sk

INTRO. TO COMP. ENG.

CHAPTER VIII-6

FINITE STATE MACHINES

•

STATE DIAGRAMS

PROPERTIES

•STATE MACHINES

•STATE DIAGRAMS

-ELEMENTS OF DIAGRAMS

Some restrictions that are placed on the state diagrams:

• FSM can only be in one state at a time!

• Therefore, only in one state, or one circle, at a time.

• State transitions are followed only on clock cycles. (synchronous!)

•

Mealy machines and Moore machines can be labelled differently.

• Mealy machine: Since output depends on state and inputs:

• Label directed arcs with input/output for that state transition.

• Moore machine: Since output depends only on state:

• Label directed arcs with input for that state transistion.

• Label state circles with S k /output.

R.M. Dansereau; v.1.0

INTRO. TO COMP. ENG.

CHAPTER VIII-7

FINITE STATE MACHINES

•

STATE DIAGRAMS

STATE DIAGRAM EXAMPLES

The following is a simple example. What does this state machine do?

0/1

0/0

S0

S1

1/0

Input:

x ( t ) ∈ { 0, 1 }

Output:

z ( t ) ∈ { 0, 1 }

State:

s ( t ) ∈ { S 0, S 1 }

Initial state:

s ( 0 ) = S0

1/0

•

•STATE MACHINES

•STATE DIAGRAMS

-ELEMENTS OF DIAGRAMS

-PROPERTIES

Here is a simplified way of forming the above state machine.

S0

0/1, 1/0

S1

0/0,1/0

• An input of 0 or 1 causes the transition with output 1 and 0, respectively.

R.M. Dansereau; v.1.0

INTRO. TO COMP. ENG.

CHAPTER VIII-8

FINITE STATE MACHINES

•

STATE DIAGRAMS

BIT FLIPPER EXAMPLE

•STATE DIAGRAMS

-ELEMENTS OF DIAGRAMS

-PROPERTIES

-STATE DIAGRAM EX.

Consider the simple bit flipper looked at the in previous chapter. How

would a state diagram be formed?

• Below is one possible way of drawing the state diagram for the bit flipper.

-/1

S0

S1

-/0

• Since the bit flipper is a Moore machine, the state diagram can also be

-

S0 ⁄ 0

S1 ⁄ 1

-

R.M. Dansereau; v.1.0

INTRO. TO COMP. ENG.

CHAPTER VIII-9

FINITE STATE MACHINES

•

STATE DIAGRAMS

PATTERN DETECT EXAMPLE

•STATE DIAGRAMS

-PROPERTIES

-STATE DIAGRAM EX.

-BIT FLIPPER EX.

Suppose we want a sequential system that has the following behaviour

x ( t ) ∈ { 0, 1 }

Input:

Output:

z ( t ) ∈ { 0, 1 }

Function:

1

z(t) =

0

if x ( t – 3, t ) = 1101

otherwise

• Effectively, the system should output a 1 when the last set of four inputs

have been 1101.

• For instance, the following output z(t) is obtained for the input x(t)

0123456789...

t

100100100100110101101101001101001

x(t)

???000000000000100001001000001000

z(t)

R.M. Dansereau; v.1.0

INTRO. TO COMP. ENG.

CHAPTER VIII-10

FINITE STATE MACHINES

•

STATE DIAGRAMS

•STATE DIAGRAMS

-STATE DIAGRAM EX.

-BIT FLIPPER EX.

-PATTERN DETECT EX.

PATTERN DETECT EXAMPLE

The following state diagram gives the behaviour of the desired 1101 pattern

detector.

• Consider S 0 to be the initial state, S 1 when first symbol detected (1), S 2

when subpattern 11 detected, and S 3 when subpattern 110 detected.

0/0

1/0

1/0

S0

S1

1/0

S2

0/0

1/1

0/0

R.M. Dansereau; v.1.0

0/0

S3

INTRO. TO COMP. ENG.

CHAPTER VIII-11

FINITE STATE MACHINES

•

STATE TABLES

INTRODUCTION

•STATE DIAGRAMS

-STATE DIAGRAM EX.

-BIT FLIPPER EX.

-PATTERN DETECT EX.

State tables also express a systems behaviour and consists of

• Present state

• The present state of the system, typically given in binary encoded

form or with S k . So, a state of S 5 in our state diagram with 10

states would be represented as 0101 since we require 4 bits.

• Inputs

• Whatever external inputs used to cause the state transitions.

• Next state

• The next state, generally in binary encoded form.

• Outputs

• Whatever outputs, other then the state, for the system. Note that

there would be no outputs in a Moore machine.

R.M. Dansereau; v.1.0

INTRO. TO COMP. ENG.

CHAPTER VIII-12

FINITE STATE MACHINES

•

STATE TABLES

•STATE DIAGRAMS

•STATE TABLES

-INTRODUCTION

BIT FLIPPER EXAMPLE

Consider again the bit flipper example with state diagram

S0 ⁄ 0

S1 ⁄ 1

-

•

The state table for this state diagram would be

R.M. Dansereau; v.1.0

Present State

Input

Next State

Output

S 0 or 0

-

1

-

S 1 or 1

-

0

-

INTRO. TO COMP. ENG.

CHAPTER VIII-13

FINITE STATE MACHINES

•

STATE TABLES

TRANSLATE FROM DIAGRAM

•STATE DIAGRAMS

•STATE TABLES

-INTRODUCTION

-BIT FLIPPER EX.

From a state diagram, a state table is fairly easy to obtain.

• Determine the number of states in the state diagram.

• If there are m states and n 1-bit inputs, then there will be m 2 n rows in

the state table.

• Example: If there are 3 states and 2 1-bit inputs, each state will

have 2 2 = 4 possible inputs, for a total of 3*4=12 rows.

• Write out for each state, the 2 n possible input rows.

• For each state/input pair, follow the directed arc in the state diagram to

determine the next state and the output.

R.M. Dansereau; v.1.0

INTRO. TO COMP. ENG.

CHAPTER VIII-14

FINITE STATE MACHINES

•

STATE TABLES

•STATE TABLES

-INTRODUCTION

-BIT FLIPPER EX.

-TRANSLATE DIAGRAM

PATTERN DETECT EXAMPLE

If we consider the pattern detection example previously discussed, the

following would be the state table.

Present State

P1 P0

Input

X

Next State

N1 N0

Output

Z

S 0 or

0

0

0

S 0 or

0

0

0

S 0 or

0

0

1

S 1 or

0

1

0

S 1 or

0

1

0

S 0 or

0

0

0

S 1 or

0

1

1

S 2 or

1

0

0

S 2 or

1

0

0

S 3 or

1

1

0

S 2 or

1

0

1

S 2 or

1

0

0

S 3 or

1

1

0

S 0 or

0

0

0

S 3 or

1

1

1

S 1 or

0

1

1

R.M. Dansereau; v.1.0

INTRO. TO COMP. ENG.

CHAPTER VIII-15

FINITE STATE MACHINES

•

STATE TABLES

TRANSLATE TO DIAGRAM

•STATE TABLES

-BIT FLIPPER EX.

-TRANSLATE DIAGRAM

-PATTERN DETECT EX.

If given a state table, the state diagram can be developed as follows.

• Determine the number of states in the table and draw a state circle

corresponding to each one.

• Label the circle with the state name for a Mealy machine.

• Label the circle with the state name/output for a Moore machine.

• For each row in the table, identify the present state circle and draw a

directed arc to the next state circle.

• Label the arc with the input/output pair for a Mealy machine.

• Label the arc with the input for a Moore machine.

R.M. Dansereau; v.1.0

INTRO. TO COMP. ENG.

CHAPTER VIII-16

FINITE STATE MACHINES

•

SEQ. CIRCUITS

INTRODUCTION

•STATE TABLES

-TRANSLATE DIAGRAM

-PATTERN DETECT EX.

-TRANSLATE TO DIAGRAM

With the descriptions of a FSM as a state diagram and a state table, the

next question is how to develop a sequential circuit, or logic diagram from

the FSM.

•

Effectively, we wish to form a circuit as follows.

Inputs

Present State

Combinational

Network

State

FF

φ 1φ 2

FF

φ 1φ 2

R.M. Dansereau; v.1.0

Outputs

(Mealy machine)

Next State

Outputs

(Moore machine)

INTRO. TO COMP. ENG.

CHAPTER VIII-17

FINITE STATE MACHINES

•

SEQ. CIRCUITS

FROM STATE TABLE

•STATE TABLES

•SEQUENTIAL CIRCUITS

-INTRODUCTION

The procedure for developing a logic circuit from a state table is the same

as with a regular truth table.

• Generate Boolean functions for

• each external outputs using external inputs and present state bits

• each next state bit using external inputs and present state bits

• Use Boolean algebra, Karnaugh maps, etc. as normal to simplify.

• Draw a register for each state bit.

• Draw logic diagram components connecting external outputs to external

inputs and outputs of state bit registers (which have the present state).

• Draw logic diagram components connecting inputs of state bits (for next

state) to the external inputs and outputs of state bit registers (which have

the present state).

R.M. Dansereau; v.1.0

SEQ. CIRCUITS

INTRO. TO COMP. ENG.

CHAPTER VIII-18

PATTERN DETECT EXAMPLE

FINITE STATE MACHINES

•

•STATE TABLES

•SEQUENTIAL CIRCUITS

-INTRODUCTION

-DEVEL. LOGIC CIRCUITS

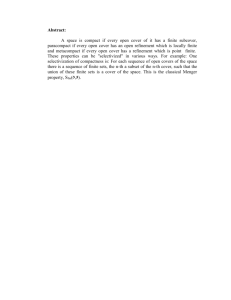

Following the procedure outlined, Boolean functions for the pattern

detector state table can be formed using Karnaugh maps as follows.

P1P0

X

00 01 11 10

P1P0

X

00 01 11 10

P1P0

X

00 01 11 10

0

0

0

1

0

0

0

1

0

0

0

0

0

0

0

1

1

1

0

0

1

1

0

1

0

1

0

0

1

0

N1

N0

N 1 = XP 1 + XP 1 P 0

N 0 = XP 1 P 0 + XP 1 P 0 + XP 1 P 0 = XP 1 P 0 + X ( P 1 ⊕ P 0 )

Z = XP 1 P 0

R.M. Dansereau; v.1.0

Z

INTRO. TO COMP. ENG.

CHAPTER VIII-19

FINITE STATE MACHINES

•

SEQ. CIRCUITS

PATTERN DETECT EXAMPLE

•SEQUENTIAL CIRCUITS

-INTRODUCTION

-DEVEL. LOGIC CIRCUITS

-PATTERN DETECT EX.

Notice that the previous Boolean functions can also be expressed with time

as follows.

N1 ( t ) = P1 ( t + 1 ) = X ( t ) ⋅ P1 ( t ) + X ( t ) ⋅ P1 ( t ) ⋅ P0 ( t )

N0 ( t ) = P0 ( t + 1 ) = X ( t ) ⋅ P1 ( t ) ⋅ P0 ( t ) + X ( t ) ⋅ P1 ( t ) ⋅ P0 ( t )

+ X ( t ) ⋅ P1 ( t ) ⋅ P0 ( t )

= X ( t ) ⋅ P1 ( t ) ⋅ P0 ( t ) + X ( t ) ⋅ P1 ( t ) ⊕ P0 ( t )

Z ( t ) = X ⋅ P1 ( t ) ⋅ P0 ( t )

•

An important thing to note in these equations is the relation between the

present states P and the next states N.

R.M. Dansereau; v.1.0

INTRO. TO COMP. ENG.

CHAPTER VIII-20

FINITE STATE MACHINES

•

SEQ. CIRCUITS

PATTERN DETECT EXAMPLE

•SEQUENTIAL CIRCUITS

-INTRODUCTION

-DEVEL. LOGIC CIRCUITS

-PATTERN DETECT EX.

The following logic circuit implements the pattern detect example.

N0

P0

φ1 φ2

N1

P1

φ1 φ2

X

R.M. Dansereau; v.1.0

Z

INTRO. TO COMP. ENG.

CHAPTER VIII-21

FSM EXAMPLES

FINITE STATE MACHINES

•

EXAMPLE #1

•SEQUENTIAL CIRCUITS

-INTRODUCTION

-DEVEL. LOGIC CIRCUITS

-PATTERN DETECT EX.

Consider the following system description.

• A sequential system has

• One input = {a, b, c}

• One output = {p, q}

• Output is

• q when input sequence has even # of a’s and odd # of b’s

• p otherwise

R.M. Dansereau; v.1.0

INTRO. TO COMP. ENG.

CHAPTER VIII-22

FINITE STATE MACHINES

•

FSM EXAMPLES

EXAMPLE #1

•SEQUENTIAL CIRCUITS

•FSM EXAMPLES

-EXAMPLE #1

We can begin forming a state machine for the system description by

reviewing the possible states. In addition, assign each state a state name.

• S EE: even # of a’s and even # of b’s / output is p

• S EO : even # of a’s and odd # of b’s / output is q

• S OO : odd # of a’s and odd # of b’s / output is p

• S OE : odd # of a’s and even # of b’s / output is p

•

Note that this machine can be a Moore machine. So, we can associate the

output with each state.

R.M. Dansereau; v.1.0

INTRO. TO COMP. ENG.

CHAPTER VIII-23

FINITE STATE MACHINES

•

FSM EXAMPLES

EXAMPLE #1

•SEQUENTIAL CIRCUITS

•FSM EXAMPLES

-EXAMPLE #1

Now draw a circle with each state.

S EE ⁄ p

R.M. Dansereau; v.1.0

S EO ⁄ q

S OO ⁄ p

S OE ⁄ p

INTRO. TO COMP. ENG.

CHAPTER VIII-24

FINITE STATE MACHINES

•

FSM EXAMPLES

EXAMPLE #1

•SEQUENTIAL CIRCUITS

•FSM EXAMPLES

-EXAMPLE #1

Finally, for each state, consider the effect for each possible input.

• For instance, starting with state S EE , the next state for the three input a,

b, and c are determined as follows.

c

S EE ⁄ p

b

S EO ⁄ q

S OO ⁄ p

a

R.M. Dansereau; v.1.0

S OE ⁄ p

FSM EXAMPLES

INTRO. TO COMP. ENG.

CHAPTER VIII-25

EXAMPLE #1

FINITE STATE MACHINES

•

•SEQUENTIAL CIRCUITS

•FSM EXAMPLES

-EXAMPLE #1

Finishing the state diagram, the following is obtained.

a

b

c

S EE ⁄ p

b

S EO ⁄ q

a

S OO ⁄ p

c

c

a

R.M. Dansereau; v.1.0

b

a

b

S OE ⁄ p

c

INTRO. TO COMP. ENG.

CHAPTER VIII-26

FSM EXAMPLES

FINITE STATE MACHINES

•

EXAMPLE #1

•SEQUENTIAL CIRCUITS

•FSM EXAMPLES

-EXAMPLE #1

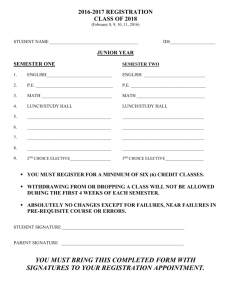

A state table can also be formed for this state diagram as follows.

• First, assign a binary number to each state

• S EE = 00 , S EO = 01 , S OO = 10 , S OE = 11

• Assign a binary number to each input

• a = 00, b = 01, c = 10

• Assign a binary number to each output

• p = 0, q = 1

• Then for each state, find the next state for each input. In this case there

are three possible input values, so, three possible state transitions from

each state.

•

The state table on the following slide shows the results for this example.

R.M. Dansereau; v.1.0

INTRO. TO COMP. ENG.

CHAPTER VIII-27

FINITE STATE MACHINES

Present State

P1 P0

SEE =

SEE =

SEE =

SEO =

SEO =

SEO =

SOO =

SOO =

SOO =

SOE =

SOE =

SOE =

R.M. Dansereau; v.1.0

0

0

0

0

0

0

1

1

1

1

1

1

0

0

0

1

1

1

0

0

0

1

1

1

FSM EXAMPLES

•SEQUENTIAL CIRCUITS

•FSM EXAMPLES

-EXAMPLE #1

EXAMPLE #1

Input

X

a = 00

b = 01

c = 10

a = 00

b = 01

c = 10

a = 00

b = 01

c = 10

a = 00

b = 01

c = 10

Next State

N1 N0

SOE =

SEO =

SEE =

SOO =

SEE =

SEO =

SEO =

SOE =

SOO =

SEE =

SOO =

SOE =

1

0

0

1

0

0

0

1

1

0

1

1

1

1

0

0

0

1

1

1

0

0

0

1

Output

Z

p=0

p=0

p=0

q=1

q=1

q=1

p=0

p=0

p=0

p=0

p=0

p=0

FSM EXAMPLES

INTRO. TO COMP. ENG.

CHAPTER VIII-28

EXAMPLE #1

FINITE STATE MACHINES

•

•SEQUENTIAL CIRCUITS

•FSM EXAMPLES

-EXAMPLE #1

The Boolean function for the output can be determined from a Karnaugh

map as follows.

• Note that an input of 11 is not possible since we only have three inputs

that we have assigned to 00, 01, and 10. We can therefore use don’t

cares for this possible input.

P1P0

X1X0 00 01 11 10

R.M. Dansereau; v.1.0

00

0

1

0

0

01

0

1

0

0

11

X X X X

10

0

1

0

0

Z = P1 P0

FSM EXAMPLES

INTRO. TO COMP. ENG.

CHAPTER VIII-29

EXAMPLE #1

FINITE STATE MACHINES

•

•SEQUENTIAL CIRCUITS

•FSM EXAMPLES

-EXAMPLE #1

The Boolean function for the next state bit can also be determined from

Karnaugh maps as follows.

P1P0

X1X0 00 01 11 10

00

1

1

0

0

00

1

0

0

1

01

0

0

1

1

01

1

0

0

1

11

X X X X

11

X X X X

10

0

10

0

0

1

1

N1 = P1 ⊕ X1 ⊕ X0

R.M. Dansereau; v.1.0

P1P0

X1X0 00 01 11 10

1

1

0

N0 = P0 X1 + P0 X1 = P0 ⊕ X1

INTRO. TO COMP. ENG.

CHAPTER VIII-30

FINITE STATE MACHINES

•

FSM EXAMPLES

EXAMPLE #1

•SEQUENTIAL CIRCUITS

•FSM EXAMPLES

-EXAMPLE #1

The following logic circuit can be made with these Boolean functions.

N1 = P1 ⊕ X1 ⊕ X0

N0 = P0 ⊕ X1

Z = P1 P0

N0

X1

P0

φ1 φ2

X0

N1

P1

φ1 φ2

R.M. Dansereau; v.1.0

Z

INTRO. TO COMP. ENG.

CHAPTER VIII-31

FSM EXAMPLES

FINITE STATE MACHINES

•

EXAMPLE #2

•SEQUENTIAL CIRCUITS

•FSM EXAMPLES

-EXAMPLE #1

A sequential circuit is defined by the following Boolean functions with input

X , present states P 0 , P 1 , and P 2 , and next states N 0 , N 1 , and N 2 .

• N2 = X ( P 1 ⊕ P0 ) + X ( P1 ⊕ P0 )

• N1 = P2

• N0 = P1

• Z = XP 1 P 2

•

Derive the state table.

•

Derive the state diagram.

R.M. Dansereau; v.1.0

INTRO. TO COMP. ENG.

CHAPTER VIII-32

FSM EXAMPLES

EXAMPLE #2

FINITE STATE MACHINES

•

•SEQUENTIAL CIRCUITS

•FSM EXAMPLES

-EXAMPLE #1

-EXAMPLE #2

The state table is formed as follows.

Present State

P2 P1 P0

Input

X

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

R.M. Dansereau; v.1.0

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

Next State

N2 N1 N0

1

0

0

1

0

1

1

0

1

0

0

1

0

1

1

0

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

Output

Z

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

1

INTRO. TO COMP. ENG.

CHAPTER VIII-33

FSM EXAMPLES

EXAMPLE #2

FINITE STATE MACHINES

•

•SEQUENTIAL CIRCUITS

•FSM EXAMPLES

-EXAMPLE #1

-EXAMPLE #2

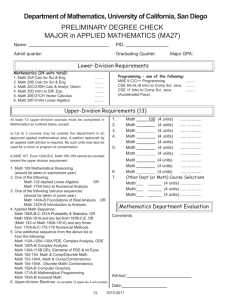

The state diagram can be drawn as follows.

1/0

1/0

S0

0/0

0/0

1/0

S1

1/0

0/0

1/0

S2

0/0

S3

0/0

0/0

S4

S5

1/0

S6

1/1

1/1

S7

0/0

0/0

R.M. Dansereau; v.1.0