Computer Organization

Douglas Comer

Computer Science Department

Purdue University

250 N. University Street

West Lafayette, IN 47907-2066

http://www.cs.purdue.edu/people/comer

Copyright 2006. All rights reserved. This document may not

be reproduced by any means without written consent of the author.

VI

Operand Addressing

And

Instruction Representation

CS250 -- Chapt. 6

1

2006

Number Of Operands Per Instruction

d Four basic architectural types

–

0-address

–

1-address

–

2-address

–

3-address

CS250 -- Chapt. 6

2

2006

0-Address Architecture

d No explicit operands in the instruction

d Operands kept on stack in memory

d Instruction removes top N items from stack

d Instruction leaves result on top of stack

CS250 -- Chapt. 6

3

2006

Example 0-Address Instructions

push X

push 7

add

pop X

d Increments X by 7

CS250 -- Chapt. 6

4

2006

1-Address Architecture

d One explicit operand per instruction

d Second operand is implicit

–

Always found in hardware register

–

Known as accumulator

CS250 -- Chapt. 6

5

2006

Example 1-Address Instructions

load X

add 7

store X

CS250 -- Chapt. 6

6

2006

2-Address Architecture

d Two explicit operands per instruction

d Result overwrites one of the operands

d Operands known as source and destination

d Works well for instructions such as memory copy

CS250 -- Chapt. 6

7

2006

Example 2-Address Instructions

add 7, X

d Computes X ← X + 7

CS250 -- Chapt. 6

8

2006

3-Address Architecture

d Three explicit operands per instruction

d Operands specify source, destination, and result

CS250 -- Chapt. 6

9

2006

Example Of 3-Address Instructions

add X, Y, Z

d Computes Z ← X + Y

CS250 -- Chapt. 6

10

2006

Example Operand Types

d Operand that specifies a source

–

Signed constant

–

Unsigned constant

–

Contents of a register

–

Value in a memory location

d Operand that specifies a destination

–

Single register

–

Pair of contiguous registers

–

Memory location

CS250 -- Chapt. 6

11

2006

Example Operand Types

(continued)

d Operand that specifies a constant is known as immediate

value

d Memory references usually much more expensive than

immediate or register access

CS250 -- Chapt. 6

12

2006

Von Neumann Bottleneck

On a computer that follows the Von Neumann architecture, the

time spent performing memory accesses can limit the overall

performance. Architects use the term Von Neumann bottleneck

to characterize the situation, and avoid the bottleneck with

techniques such as restricting most operands to registers.

CS250 -- Chapt. 6

13

2006

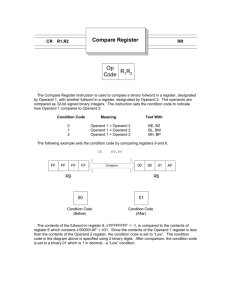

Operand Encoding

d Implicit type encoding

–

For given opcode, the type of each operand is fixed

–

More opcodes required

–

Example: opcode is add_signed_immediate_to_register

d Explicit type encoding

–

Operand specifies type and value

–

Fewer opcodes required

–

Example: opcode is add, operands specify register and

immediate

CS250 -- Chapt. 6

14

2006

Example Of Implicit Encoding

Opcode

Operands

Meaning

22222222222222222222222222222222222222222222222222222222222222222

Add register

R1 R2

R1 ← R1 + R2

Add immediate signed

R1 I

R1 ← R1 + I

Add immediate unsigned

R1 UI

R1 ← R1 + UI

Add memory

R1 M

R1 ← R1 + memory[M]

CS250 -- Chapt. 6

15

2006

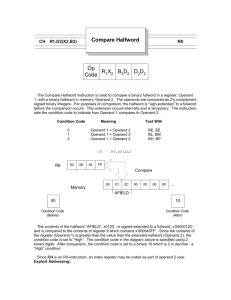

Example Of Explicit Encoding

opcode

add

operand 1

..

..

..

register ...

..

..

.

operand 2

1

..

..

..

register ...

..

..

.

operand 1

add

CS250 -- Chapt. 6

..

..

..

register ...

..

..

.

operand 2

1

16

2

signed

integer

..

..

..

..

..

..

..

-93

2006

Combinations

d Operand specifies multiple items

d Processor computes final value from individual items

d Typical computation: sum

d Example

–

Register-offset specifies register and immediate value

–

Processor adds immediate value to contents of register

CS250 -- Chapt. 6

17

2006

Illustration Of Register-Offset

opcode

add

CS250 -- Chapt. 6

operand 1

..

..

register- ....

offset ...

..

.

2

operand 2

..

..

..

..

..

..

..

18

-17

..

..

register- ....

offset ...

..

.

4

..

..

..

..

..

..

..

76

2006

Operand Tradeoffs

d No single style of operands optimal for all purposes

d Tradeoffs among

–

Ease of programming

–

Fewer instructions

–

Smaller instructions

–

Larger range of immediate values

–

Faster operand fetch and decode

–

Decreased hardware size

CS250 -- Chapt. 6

19

2006

Operands In Memory And Indirect Reference

d Operand can specify

–

Value in memory (memory reference)

–

Location in memory that contains the address of the

operand (indirect reference)

d Note: memory references are relatively expensive

CS250 -- Chapt. 6

20

2006

Types Of Indirection

d Indirection through a register

–

Operand specifies register number, R

–

Obtain A, the current value from register R

–

Interpret A as a memory address, and fetch the operand

from memory location A

d Indirection through a memory location

–

Operand specifies memory address, A

–

Obtain M, the value in memory location A

–

Interpret M as a memory address, and fetch the operand

from memory location M

CS250 -- Chapt. 6

21

2006

Illustration Of Operand Addressing Modes

cpu

memory

locations in memory

instruction register

4

1

5

2

3

5

3

general-purpose register

1 Immediate value (in the instruction)

2 Direct register reference

3 Indirect through a register

4 Direct memory reference

5 Indirect memory reference

CS250 -- Chapt. 6

22

2006

Summary

d Architect chooses the number and types of operands for

each instruction

d Possibilities include

–

Immediate (constant value)

–

Contents of register

–

Value in memory

–

Indirect reference to memory

CS250 -- Chapt. 6

23

2006

Summary

(continued)

d Type of operand can be encoded

–

Implicitly

–

Explicitly

d Many variations exist; each represents a tradeoff

CS250 -- Chapt. 6

24

2006

Questions?