S h d l (1) Schedule (1)

advertisement

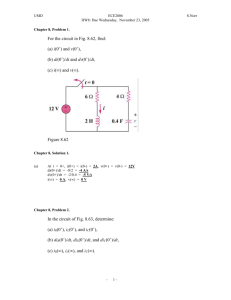

S h d l (1) Schedule 01. 02/25/16 Chapter 1 Introduction (Moore’s rule) 02. 03/03/16 Chapter 1 Introduction (Cost and TW) 03 03/10/16 Chapter 2 (Mask) 03. 04. 03/17/16 Chapter 2 (Processing) 05. 03/24/16 Chapter 2 (Transistors) 06 03/31/16 Quiz 1, 06. 1 Chapter 2 (Cross-section (C ti , latch l t h up)) 07. 04/07/16 Chapter 2 (Layout, Reverse Engineering) VLSI Design : Chapter 2-1 1 AQ Quick i kR Review i on Ch Chapter O One VLSI? Moore’s Law The Difficulties in VLSI Design Cost of the VLSI Design Taiwan VLSI Related Industry VLSI Design : Chapter 2-1 2 Ch Chapter 22: T Transistors i & Layout L Masks Basic fabrication steps (Next week) Transistor structures Basic transistor behavior VLSI Design : Chapter 2-1 3 Flow Fl Marketing survey Specification English, Idea Design: Architecture, Logic, Circuit Backend, …. GDSII Manufacture: Masks, Die, Packaging Dice, Chips Testing g VLSI Design : Chapter 2-1 4 F b i i Services Fabrication S i Educational services (government funding, free for students) : U.S.: MOSIS EC: EuroPractice Taiwan: CIC Japan: VDEC Foundry = fabrication lines for hire (fab) TSMC, UMC, TSMC UMC SMIC, SMIC Samsung, Samsung Chartered, IBM (X-Fab) Jazz Tower Jazz, Tower, HHNEC HHNEC…… VLSI Design : Chapter 2-1 5 MOSIS MPW Program g • Winning Enabler for New Designs • MOSIS engagement model for start-ups and initial prototyping runs • Validate IBM Model-to-Hardware Model to Hardware Correlations and Tech Support on test chips MOSIS Information Science Institute University of Southern California 4676 Admiralty Way, 7th Floor Marina del Rey Rey, CA 90292-6695 U.S. Rep: Wes Hansford hansford@mosis.org 1-310-448-9316 VLSI Design : Chapter 2-1 6 2006 MOSIS MPW Schedule and D li Deliverables bl A) MOSIS Deliverable = 40 dies per each chip design g B) MOSIS MPW Pricing available at http://www.mosis.org/Ord ers/Prices/price-listp export.html 1. MPW Schedule for IBM: http://www.mosis.org/products/fab/schedule/ http://www.mosis.org/Orders/Prices/price-list-export.html 7 VLSI Design : Chapter 2-1 More info: http://www.phy.ntnu.edu.tw/demolab/html.php?html=JavaScript/s_pertab 8 VLSI Design : Chapter 2-1 Design Package Layout Masks Wafer Photolithographic Process W f Wafer Chips Chi VLSI Design : Chapter 2-1 9 柴可斯基拉晶機 氬 Seed S dH Holder ld 晶種固定器 拉升方向 旋 轉 晶種 Silicon Seed 石墨基底 晶體 Ingot 矽坩堝 Silica Crucible 熱阻絲 熔融液體 Melt 固-液接面 固 液接面 VLSI Design : Chapter 2-1 10 Fl i Zone Floating Z Zone refinement VLSI Design : Chapter 2-1 11 300mm asas-grown Crystal VLSI Design : Chapter 2-1 12 Single Crystal Production VLSI Design : Chapter 2-1 13 VLSI Design : Chapter 2-1 14 18 Inches Wafer VLSI Design : Chapter 2-1 15 F b i i Processes Fabrication P IC built on silicon substrate: some structures diffused into substrate; other structures built on top of substrate * (SOI) Substrate regions are doped with n-type and p-type p ype impurities. pu es. (n+, ( , p+ p = heavily eav y doped) Wires made of polycrystalline silicon, silicide, Al or Cu Al, Cu. (Wu (Wu, Ti) Silicon dioxide (SiO2) is insulator. VLSI Design : Chapter 2-1 16 Chip Chi VLSI Design : Chapter 2-1 17 積體電路產業流程 電路設計公司 光罩製作廠 電路設計 光罩製作 積體電路製造 晶圓材料廠 封裝廠 測試廠 客 晶圓製造 積體電路封裝 積體電路測試 戶 VLSI Design : Chapter 2-1 18 積體電路製造之流程圖 Integrated Circuit Process Flow 晶片 Wafer 薄膜形成 Thin Film Deposition 雜質滲入 Dopant Diffusion/ Implantation 微影術 Photolithography 光 罩 Mask Set VLSI Design : Chapter 2-1 蝕 刻 Etch 晶片完成 Completed Wafer 19 積體電路生產流程 Integrated Circuit Process Flow ● 第一層光罩 1st masking step ● 蝕刻機Etcher ● 離子植入機Ion Implanter ● 初步氧化 Oxidation ● 微影製程 Photo Lithography ● 蝕刻 Etching ● 離子植入 Ion Implantation ● 第二層光罩 2nd masking step ● 氧化爐 Furnace F ● 氧化爐 Furnace ● 晶圓Wafer ● 擴散爐 Furnace ● 第三層光罩 3rd masking step ● 金屬濺鍍機 Sputter S tt 重覆前述 製程數次 Process repeats ● 擴散 Diffusion ● 微影蝕刻 Lithography Etching ● 微影蝕刻 ● 氧化Oxidation Lithography Etching ● 金屬濺鍍 Sputtering ● 第N 層光罩 Nth masking step ● 金屬層微影蝕刻 VLSIlayer DesignLitho/Etching : Chapter 2-1 Metal ● 晶圓針測 Wafer Probing ● 晶圓切割 Wafer Sawing ● 晶粒黏著 Dice Attachment 外包廠代工Subcontractor ● 打線連接 Bonding ● 完成裝配及測試 Finished IC 20Package F b i i Flow Fabrication Fl Design house GDSII Layout Masks Design Photolithographic Iterate fro 20~40+ times Package g Wafer Process Foundry Testing CP Chips VLSI Design : Chapter 2-1 Testing FT Testing and packaging 21 M k Mask Design Layout Package g Masks Wafer Photolithographic Process Foundry Testing Chips VLSI Design : Chapter 2-1 Testing Testing and packaging 22 Design Package Layout Masks Wafer Photolithographic Process M k Mask Chi Chips Photomask is an i image transfer f vehicle hi l that serve the stepper ( (scanner) ) iin Fab F b to t expose the IC circuit patterns tt onto t wafers f Light source : I-line I line (365nm) KrF (248nm) ArF (193nm) VLSI Design : Chapter 2-1 23 Design Package Layout Masks Wafer Photolithographic Process Bi Binary Photomask Ph k Chi Chips Photo resist 6 inches CrO2 film 1/4 inch Cr film Quarts As usual the transmittance will physically decrease while the wavelength of a light source is shorter 350nm. So h t then th 350 S the th Transmittance % Quartz with a high transmittance is essential to a photomask. VLSI Design : Chapter 2-1 quartz 100 90 80 Poly silicate 70 glass 60 50 40 30 20 10 0 200 250 300 Soda lime glass 350 400 450 500 Wavelength (nm)24 Design Package Layout Masks Wafer Photolithographic Process M i l off Mask Material M k Chi Chips A substrate consisted of a quartz plate sputtered with a chrome thin film (MOSiON) g sensitive p polymer y and coated with a light (photo resist) onto the chrome film. pphoto resist Cr/CrOx quartz VLSI Design : Chapter 2-1 25 M k Profile Mask P fil photo resist Cr/CrOx QZ Development chemical : TMAH Etch wet : (NH4)2Ce(NO3)6,HClO4,H2O dry : Cl2 , O2 Resist Strip wet : NMP , H2SO4 VLSI Design : Chapter 2-1 26 Design Package Layout Masks Wafer Photolithographic Process P lli l Pellicle Chi Chips Pellicle is used to prevent the particles in environment from falling onto the photomask and assure the defect free p exposure process VLSI Design : Chapter 2-1 27 Design Layout Package Masks Wafer Photolithographic M k Fl Mask Flow Process Chi Chips exposure data conversion defect inspection process pre-cleaning cleaning CD / overlay & basic inspection mask k repair pellicle mounting VLSI Design : Chapter 2-1 particle inspection outgoing g g check & package shipping 28 Bi Binary & HTPSN Ph Photomask k 6 inches ¼ inch Bridge phenomenon will happen subsequently if the distance between Binary two holes is too short. HTPSM is an effective solution for improving p g resolution and always applied for metal layers such like contact, via and so on. VLSI Design : Chapter 2-1 Binary Photo resist CrO2 film Cr film MoSiON Quarts HTPSM Amplitude on mask Intensity on wafer Light diffraction area Bridge Two images on wafer 29 PSM Phase Shifting Masks (PSM) etch topography into mask Creates interference fringes on the wafer Interference effects boost contrast Phase Masks can make extremely small gates conventional mask glass phase shifting mask Chrome Phase shifter Electric field at mask Intensity at wafer VLSI Design : Chapter 2-1 30 S h d l (1) Schedule 01. 02/25/16 Chapter 1 Introduction (Moore’s rule) 02. 03/03/16 Chapter 1 Introduction (Cost and TW) 03 03/10/16 Chapter 2 (Mask) 03. 04. 03/17/16 Chapter 2 (Processing) 05. 03/24/16 Chapter 2 (Transistors) 06 03/31/16 Quiz 1, 06. 1 Chapter 2 (Cross-section (C ti , latch l t h up)) 07. 04/07/16 Chapter 2 (Layout, Reverse Engineering) VLSI Design : Chapter 2-1 31 M k to wafer Mask f Layout 0.25µ 0.18µ 0 13 0.13µ 90-nm 65-nm VLSI Design : Chapter 2-1 32 Design Layout Package Masks Wafer Photolithographic OPC (1) Process Chi Chips OPC Software Writing Tool Original g Design g Design with OPC Mask Design OPC mask Issues Conventional 1 Data Handling burden 1. 2. Long exposure time and Process Image on Mask lithography g p y Binary Mask 3. Defect Inspection OPC Binary Mask VLSI Design : Chapter 2-1 lithography 33 OPC (2) OPC VLSI Design : Chapter 2-1 Fracture 34 OPC (3) Optical Proximity Correction ( (OPC,光學鄰近校正) 光學鄰近校正) is i a photolithography enhancement technique commonly used to compensate for image errors due to diffraction or process effects. effects we'd like printed on the wafer, VLSI Design : Chapter 2-1 the shape after applying optical proximity correction, correction how the shape actually prints 35 Detects & Corrects Lithography Hotspots IC Compiler Lithography Compliance Check Hotspot Detection I iti l Layout Initial L t Hotspot Detected Hotspot Correction Clean Layout Lithography Models VLSI Design : Chapter 2-1 36 Design Layout Package Masks Wafer Photolithographic Ali Alignments Process Chi Chips • CD (critical dimension) line width of pattern geometries on photomask Bar code Alignment mark A A A A main cell Feducial • registration (position accuracy) Frame H0299-4U20A1 H0299 4U20A1 title VLSI Design : Chapter 2-1 37 Design Package Layout Masks Wafer Photolithographic R i (1) Repair Process Chi Chips The ionized carbon will be diffused onto the pin hole while the FIB is applied applied. Ga focused ion beam Styrene Ionized carbon Before repair Pin hole After repair VLSI Design : Chapter 2-1 38 Design Package Layout Masks Wafer Photolithographic R i (2) Repair Process Chi Chips The pin dot will be removed by laser beam. Laser Beam Before repair Pin dot After repair VLSI Design : Chapter 2-1 39 Design Package Layout Masks Wafer Photolithographic Process I Inspection i Chi Chips A:端面接觸痕 B:端面霧化 C:導角連續亮點 D:Pellicle框與Pellicle case接觸痕 E:Pellicle框上原材製程殘留痕跡 F:Mask洗邊不完整 G: Case 接觸痕 H:Mask 邊緣數字符號未解析 I:G面亮紋(距離 Edge5mm內) J:膜面亮紋(距離 Edge5mm內) K:夾具接觸痕 L:原材端面刻字 VLSI Design : Chapter 2-1 40 F bP Fab Processes Design Package g Layout Masks Wafer Photolithographic Process Foundry Testing Chips VLSI Design : Chapter 2-1 Testing 41 ● 亂流 空調機 清淨空氣從過濾器吹 出口,由地板附近吸 入。 ● VLSI Design : Chapter 2-1 42 ●垂直層流 清淨空氣自屋 頂至地板的流 通方式。 VLSI Design : Chapter 2-1 空調機 43 VLSI Design : Chapter 2-1 44 VLSI Design : Chapter 2-1 45 VLSI Design : Chapter 2-1 46 Clean-room Standard VLSI Design : Chapter 2-1 47 Design Layout Package Masks Wafer Photolithographic Ph li h Photolithography h Process Chi Chips optical mask oxidation photoresist removal (ashing) photoresist coating pp exposure p stepper Etch Wet Dry CVD Ion Imp VLSI Design : Chapter 2-1 Typical operations in a single photolithographic cycle (from [Fullman]). 上光阻液 軟烤 曝光 硬烤 顯影 Etching photoresist development acid etch process step spin, rinse, dry 48 VLSI Design : Chapter 2-1 49 VLSI Design : Chapter 2-1 50 Design Package Layout Masks Wafer Photolithographic Process Chips Chi VLSI Design : Chapter 2-1 51 Design Package Layout Masks Wafer Photolithographic Process Ph li h Photolithography h Chi Chips Mask patterns are put on wafer using photosensitive material: VLSI Design : Chapter 2-1 52 VLSI Design : Chapter 2-1 53 Design Package Layout Masks Wafer Photolithographic Process Chips Chi VLSI Design : Chapter 2-1 54 VLSI Design : Chapter 2-1 55 Di Size Die Si and d Yi Yield ld VLSI Design : Chapter 2-1 56 Design Package Layout Masks Wafer Photolithographic Process Chips Chi VLSI Design : Chapter 2-1 57 Design Package Layout Masks Wafer Photolithographic Process D i Doping Chips Chi VLSI Design : Chapter 2-1 58 VLSI Design : Chapter 2-1 59 VLSI Design : Chapter 2-1 60 VLSI Design : Chapter 2-1 61 VLSI Design : Chapter 2-1 62 SiO2 450 C SiH 4 2O 2 SiO 2 2H 2 O 300 ~ 500 C SiH 4 O 2 SiO 2 2H 2 VLSI Design : Chapter 2-1 63 VLSI Design : Chapter 2-1 64 Search for the “VLSI manufacture” . https://www.youtube.com/watch?v=gBAKXvsaEiw VLSI Design : Chapter 2-1 65 Quiz Next Week 15% Covered From Chapter 1 to today’s material Time: 18:40 ~ 19:10 Pl Please bring b i color l pens Seat will be arranged g VLSI Design : Chapter 2-1 66 S h d l (1) Schedule 01. 02/25/16 Chapter 1 Introduction (Moore’s rule) 02. 03/03/16 Chapter 1 Introduction (Cost and TW) 03 03/10/16 Chapter 2 (Mask) 03. 04. 03/17/16 Chapter 2 (Processing) 05. 03/24/16 Chapter 2 (Transistors) 06 03/31/16 Quiz 1, 06. 1 Chapter 2 (Cross-section (C ti , latch l t h up)) 07. 04/07/16 Chapter 2 (Layout, Reverse Engineering) VLSI Design : Chapter 2-1 67 Design Package Layout Masks Wafer Photolithographic Ph li h Photolithography h Process Chi Chips optical mask oxidation photoresist removal (ashing) photoresist coating pp exposure p stepper Typical operations in a single photolithographic cycle (from [Fullman]). photoresist development acid etch process step VLSI Design : Chapter 2-1 spin, rinse, dry 68 Design Layout Package Masks Wafer Photolithographic P Processes Process Chi Chips cross section Chemical or plasma etch Si-substrate Hardened resist SiO 2 (a) Silicon base material Si-substrate Photoresist SiO 2 Si-substrate (d) After development and etching of resist, chemical or plasma etch of SiO 2 Hardened resist SiO 2 (b) After oxidation and deposition of negative photoresist UV-light Patterned optical mask Si-substrate (e) After etching Exposed resist Si-substrate (c) Stepper exposure VLSI Design : Chapter 2-1 SiO 2 Si-substrate (f) Final result after removal of resist 69 Design Package Layout Masks Wafer Photolithographic Process P Processing i II II-1 1 Chips Chi VLSI Design : Chapter 2-1 70 Design Package Layout Masks Wafer Photolithographic Processing II-2 Process Chips Chi Ex: Metal, poly, …… VLSI Design : Chapter 2-1 71 Basic fabrication steps Transistor structures Basic transistor behavior VLSI Design : Chapter 2-1 72 Design Package Layout Masks Wafer Photolithographic D i Design Process Chi Chips VDD VDD Transistor level M2 M4 Vout Vin Vout2 M3 M1 Gate level Gate level VLSI Design : Chapter 2-1 Gate level 73 Design Package Layout Masks Wafer Photolithographic Process F From D Design i to L Layout Chips Chi Layout level VLSI Design : Chapter 2-1 level 74 Process steps First place tubs to provide properly-doped substrate for n-type, p-type transistors: Substrate (p--) Cross-section p-tub (p-well) n-tub (n-well) Substrate (p (p--)) VLSI Design : Chapter 2-1 75 P Process steps, cont’d. ’d Pattern polysilicon before diffusion regions: poly pt b p-tub VLSI Design : Chapter 2-1 gate oxide poly nt b n-tub 76 P Process steps, cont’d ’d Add diffusions, performing self-masking: poly n+ VLSI Design : Chapter 2-1 pt b p-tub poly n+ p+ nt b n-tub p+ 77 P Process steps, cont’d ’d Start adding metal layers: metal 1 metal 1 contact poly n+ VLSI Design : Chapter 2-1 p-tub via poly n+ p+ n-tub p+ 78 Th C The Cross S Section i off an IC SiO2 metal3 via metal2 metal1 transistor contact poly n+ VLSI Design : Chapter 2-1 p n+ substrate s bstrate substrate 79 Th Cross The C Section S i off an Inverter I gate-oxide TiSi2 AlCu SiO2 Tungsten poly p-well n+ SiO2 n-well p-epi p+ p+ VLSI Design : Chapter 2-1 80 P Process steps, cont’d ’d VLSI Design : Chapter 2-1 81 T Transistor i layout l n-type (tubs/well may vary): p-well L w contact n-diff poly VLSI Design : Chapter 2-1 82 NMOS T Transistor i VLSI Design : Chapter 2-1 83 T Transistor i structure n-type transistor: VLSI Design : Chapter 2-1 (Angstrom) Å, A, AU 1/10 mµ , 10-10m, m 10-8cm 84 Design Package Layout Masks Wafer Photolithographic Process Q i k Look Quick L k Again A i (1) Chi Chips p-epi (a) Base material: p+ substrate with p p-epi p layer y p+ SiN 34 p-epi p+ p+ VLSI Design : Chapter 2-1 SiO 2 (b) After deposition of gate-oxide and sacrificial nitride (acts as a buffer layer) (c) After plasma etch of insulating trenches using the inverse of the active area mask 85 Design Package Layout Masks Wafer Photolithographic Process Q i k Look Quick L k Again A i (2) Chi Chips SiO 2 (d) After trench filling, CMP planarization, and removal of sacrificial nitride n p VLSI Design : Chapter 2-1 (e) After n-well and V adjust implants Tp (f) After p-well and V adjust implants Tn 86 Design Package Layout Masks Wafer Photolithographic Process Q i k Look Quick L k Again A i (3) poly(silicon) Chi Chips (g) After polysilicon deposition and etch Self-alignment!! n+ p+ (h) After n+ source/drain and p+source/drain implants implants. These steps also dope the polysilicon. SiO 2 (i) After deposition of SiO insulator and contact hole2etch. VLSI Design : Chapter 2-1 87 Design Package Layout Masks Wafer Photolithographic Process Q i k Look Quick L k Again A i (4) Chi Chips Al (j) After deposition and patterning of first Al layer. Al SiO 2 (k) After deposition of SiO insulator, etching of via’s, 2 deposition and patterning of second layer of Al. VLSI Design : Chapter 2-1 88 VLSI Design : Chapter 2-1 89 VLSI Design : Chapter 2-1 90 VLSI Design : Chapter 2-1 91 VLSI Design : Chapter 2-1 92 VLSI Design : Chapter 2-1 93 VLSI Design : Chapter 2-1 94 VLSI Design : Chapter 2-1 95 Design Package Layout Masks Wafer Photolithographic Ph li h Photolithography h Process Chi Chips optical mask oxidation photoresist removal (ashing) photoresist coating pp exposure p stepper Typical operations in a single photolithographic cycle (from [Fullman]). photoresist development acid etch process step VLSI Design : Chapter 2-1 spin, rinse, dry 96 Design Package Layout Masks Wafer Photolithographic Process M l Li Metal Lines Chips Chi Let’s et s have ave a look oo at the real process VLSI Design : Chapter 2-1 97 IC Cross Section and 3D View VLSI Design : Chapter 2-1 98 SEM XX-section - Device HV-NMOS N+ N-grade N-drift N-drift N+ N-grade X 6000 HV-PMOS P+ P-grade P d P d ift P-drift P+ P P-grade d P d ift P-drift X 6000 N+ N-grade VLSI Design : Chapter 2-1 X 20000 DDD structure 99 44 VLSI Design : Chapter 2-1 100 VLSI Design : Chapter 2-1 101 Quiz Next Week 15% Covered From Chapter 1 to today’s material Time: 18:40 ~ 19:10 Pl Please bring b i color l pens Seat will be arranged g VLSI Design : Chapter 2-1 102