Interrupt Request

advertisement

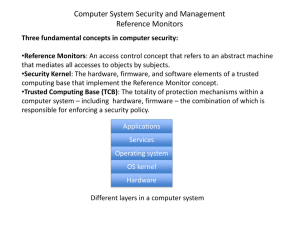

Programmed I/O Interrupt-Driven I/O Direct Memory Access (DMA) I/O Processors 10/08/2015 Input/Output Systems and Peripheral Devices (02-2) 1 Principle of Interrupt-Driven I/O Multiple-Interrupt Systems Priority Interrupt Systems Parallel Priority Interrupts Daisy-Chain Priority Interrupts 10/08/2015 Input/Output Systems and Peripheral Devices (02-2) 2 Interrupt – suspension of program execution by an external signal or by an internal event of the CPU Program suspension occurs at the end of the current instruction’s execution The CPU is relieved from the task of testing the status of I/O devices Interrupt sources can be external or internal to the CPU 10/08/2015 Input/Output Systems and Peripheral Devices (02-2) 3 Examples of interrupt sources: Peripheral devices data transfers Virtual memory page transfers Hardware circuits for supervising normal operation of the system: detecting memory errors, power-supply failures Internal software events: overflows, divisions by zero, non-existent or privileged instructions 10/08/2015 Input/Output Systems and Peripheral Devices (02-2) 4 For interrupting the CPU, a control line is asserted IREQ (Interrupt Request) An interrupt flag is set When recognizing the interrupt request, the CPU: Asserts an interrupt acknowledge signal IACK (Interrupt Acknowledge) Executes an interrupt handler routine, associated with the interrupt source 10/08/2015 Input/Output Systems and Peripheral Devices (02-2) 5 For transferring control to the interrupt handler routine: The CPU identifies the interrupt source The CPU determines the address of the interrupt handler corresponding to the interrupt source The CPU saves the program counter (PC) and other status information The CPU loads the address of the interrupt handler into the program counter 10/08/2015 Input/Output Systems and Peripheral Devices (02-2) 6 The CPU has to determine the address of the interrupt handler Methods for choosing the address of the interrupt handler: Nonvectored interrupts: the interrupt handler is located at a fixed address in memory Vectored interrupts: the address is supplied by the interrupt source, in the form of an interrupt vector 10/08/2015 Input/Output Systems and Peripheral Devices (02-2) 7 Principle of Interrupt-Driven I/O Multiple-Interrupt Systems Priority Interrupt Systems Parallel Priority Interrupts Daisy-Chain Priority Interrupts 10/08/2015 Input/Output Systems and Peripheral Devices (02-2) 8 For registering the interrupt requests, an interrupt request register is used For an individual control of interrupt sources, mask flip-flops are used interrupt mask register Main problems: Identifying the source of interrupt Choosing the interrupt to service in case of several simultaneous requests 10/08/2015 Input/Output Systems and Peripheral Devices (02-2) 9 Techniques for identifying the source of interrupt: Multiple interrupt lines Software polling Connecting the devices in a daisy chain (hardware polling) Bus arbitration 10/08/2015 Input/Output Systems and Peripheral Devices (02-2) 10 Multiple interrupt lines between the CPU and the I/O modules The simplest solution It is impractical to dedicate a large number of bus lines or processor pins to interrupt lines Usually, multiple I/O modules will be attached to each line 10/08/2015 Input/Output Systems and Peripheral Devices (02-2) 11 Software polling When the CPU detects an interrupt, it executes an interrupt-service routine The I/O modules are interrogated (polled) to determine which module generated the interrupt For polling, a separate command line may be used (e.g., TEST I/O) Each I/O module may contain an addressable status register 10/08/2015 Input/Output Systems and Peripheral Devices (02-2) 12 Hardware polling A daisy-chain of devices is used All I/O modules share a common interrupt request line When detects an interrupt request, the CPU asserts an interrupt acknowledge signal The interrupt acknowledge signal is daisychained through the I/O modules 10/08/2015 Input/Output Systems and Peripheral Devices (02-2) 13 The acknowledge signal propagates through the I/O modules until it reaches a requesting module This module responds by placing an interrupt vector on the data bus The CPU uses the vector as a pointer to the service routine for the module Advantage: there is no need to execute a general interrupt service routine 10/08/2015 Input/Output Systems and Peripheral Devices (02-2) 14 Bus arbitration Uses vectored interrupts An I/O module must first gain control of the bus before it can assert the interrupt request signal When detects the interrupt, the CPU asserts the interrupt acknowledge signal The requesting module places its vector on the data lines 10/08/2015 Input/Output Systems and Peripheral Devices (02-2) 15 Principle of Interrupt-Driven I/O Multiple-Interrupt Systems Priority Interrupt Systems Parallel Priority Interrupts Daisy-Chain Priority Interrupts 10/08/2015 Input/Output Systems and Peripheral Devices (02-2) 16 In case of simultaneous requests, a priority system is needed Establishing the priority of simultaneous interrupts can be done in software or in hardware Software method: Identification of the highest-priority source is made by polling There is a common service routine, which polls the interrupt sources 10/08/2015 Input/Output Systems and Peripheral Devices (02-2) 17 The order in which the sources are polled determines their priority Disadvantage: if there are many sources, the time required for polling increases Hardware method: An interrupt controller accepts interrupt requests from many sources and determines the highest priority request Each source has its own interrupt vector 10/08/2015 Input/Output Systems and Peripheral Devices (02-2) 18 Principle of Interrupt-Driven I/O Multiple-Interrupt Systems Priority Interrupt Systems Parallel Priority Interrupts Daisy-Chain Priority Interrupts 10/08/2015 Input/Output Systems and Peripheral Devices (02-2) 19 An interrupt register RINT is used Its bits are set separately by the interrupt requests of each device Priority is established according to the position of bits in the register The interrupt mask register RM allows to control (disable) the status of each interrupt request 10/08/2015 Input/Output Systems and Peripheral Devices (02-2) 20 10/08/2015 Input/Output Systems and Peripheral Devices (02-2) 21 The priority encoder: Implements the priority function Generates two bits of the interrupt vector The vector is transferred to the CPU via tristate buffers The buffers are enabled with the INTACK signal from the CPU and the IST, IEN flipflops IST – interrupt status flip-flop IEN – interrupt enable flip-flop 10/08/2015 Input/Output Systems and Peripheral Devices (02-2) 22 Principle of Interrupt-Driven I/O Multiple-Interrupt Systems Priority Interrupt Systems Parallel Priority Interrupts Daisy-Chain Priority Interrupts 10/08/2015 Input/Output Systems and Peripheral Devices (02-2) 23 All devices that can generate an interrupt request are connected in a daisy-chain The device with the highest priority is placed in the first position The interrupt request line is shared by all devices (wired OR connection) When no interrupt requests are pending, the interrupt request line remains at logical 0 10/08/2015 Input/Output Systems and Peripheral Devices (02-2) 24 10/08/2015 Input/Output Systems and Peripheral Devices (02-2) 25 The CPU responds to an interrupt request by asserting the INTACK signal The signal is received by device D0 at its PI (Priority In) input The signal is sent to the PO (Priority Out) output only if device D0 is not requesting an interrupt If D0 has a pending interrupt: Blocks the acknowledge signal Places its own interrupt vector 10/08/2015 Input/Output Systems and Peripheral Devices (02-2) 26 Programmed I/O Interrupt-Driven I/O Direct Memory Access (DMA) I/O Processors 10/08/2015 Input/Output Systems and Peripheral Devices (02-2) 27 Principle of I/O through DMA Execution of DMA Transfers Configurations of Systems Using DMA Transfers 10/08/2015 Input/Output Systems and Peripheral Devices (02-2) 28 Disadvantage of programmed I/O and interrupt-driven I/O: the CPU is busy with managing the I/O operations DMA eliminates this disadvantage data transfers are executed directly between the internal memory and the I/O system An additional module is required DMA controller Two methods for performing transfers through DMA 10/08/2015 Input/Output Systems and Peripheral Devices (02-2) 29 1. By suspending the CPU operations and placing the bus in the high-impedance state during the transfer Data break or block transfer This method is required, e.g., for magnetic disk drives data transmission cannot be stopped or slowed down The CPU is inactive for relatively long time periods 10/08/2015 Input/Output Systems and Peripheral Devices (02-2) 30 2. By using the time intervals when the CPU does not access the memory Cycle stealing Large blocks of data are transferred by a sequence of DMA bus transactions interspersed with CPU bus transactions The method reduces the maximum transfer rate, but it also reduces the interference of the DMA controller in accessing memory by the CPU 10/08/2015 Input/Output Systems and Peripheral Devices (02-2) 31 Breakpoints of the CPU for performing transfers through DMA and through interrupts 10/08/2015 Input/Output Systems and Peripheral Devices (02-2) 32 Principle of I/O through DMA Execution of DMA Transfers Configurations of Systems Using DMA Transfers 10/08/2015 Input/Output Systems and Peripheral Devices (02-2) 33 The CPU sends an initialization sequence to the DMA controller The initialization sequence contains: Direction of transfer (read or write) Address of the I/O device involved Starting address of the memory area used for the transfer Number of bytes or words to be transferred 10/08/2015 Input/Output Systems and Peripheral Devices (02-2) 34 The CPU releases the bus and may execute other operations The DMA controller generates the addresses and control signals needed for the transfer After a DMA cycle, other cycles may follow or the control is transferred to the CPU When the transfer is complete, the DMA controller generates an interrupt request to the CPU 10/08/2015 Input/Output Systems and Peripheral Devices (02-2) 35 10/08/2015 Input/Output Systems and Peripheral Devices (02-2) 36 1. The CPU loads the IOAR and DC registers with initial values I/O instructions 2. When the DMA controller is ready for the transfer, it asserts the DMAREQ signal At the next DMA breakpoint, the CPU releases the bus and asserts DMAACK 3. The DMA controller transfers data directly with the main memory; the IOAR and DC registers are updated 10/08/2015 Input/Output Systems and Peripheral Devices (02-2) 37 4. If the DC register 0, but the I/O device is not ready, the DMA controller releases the bus The CPU disables the DMAACK signal and takes control of the bus 5. If the DC register = 0, the DMA controller releases the bus and sends an interrupt request to the CPU The CPU responds by halting the I/O device or by initiating a new transfer 10/08/2015 Input/Output Systems and Peripheral Devices (02-2) 38 Principle of I/O through DMA Execution of DMA Transfers Configurations of Systems Using DMA Transfers 10/08/2015 Input/Output Systems and Peripheral Devices (02-2) 39 10/08/2015 Input/Output Systems and Peripheral Devices (02-2) 40 10/08/2015 Input/Output Systems and Peripheral Devices (02-2) 41 Programmed I/O Interrupt-Driven I/O Direct Memory Access (DMA) I/O Processors 10/08/2015 Input/Output Systems and Peripheral Devices (02-2) 42 Principle of I/O through I/O Processors Execution of an I/O Program Intel I/O Processors 10/08/2015 Input/Output Systems and Peripheral Devices (02-2) 43 Principle of I/O through I/O Processors (1) While DMA releases the CPU from many I/O operations, for high-speed peripherals numerous bus cycles will be needed During these cycles, the CPU enters a wait state The cycle stealing will saturate the bus A certain time is required to service the interrupts The I/O modules have been improved, becoming I/O processors (IOPs) 10/08/2015 Input/Output Systems and Peripheral Devices (02-2) 44 Principle of I/O through I/O Processors (2) Some of these I/O modules are also called I/O channels IOPs have a specialized instruction set for I/O operations The CPU sends a command to the IOP to execute an I/O program (channel program) located in memory The CPU can specify a sequence of I/O operations, and is interrupted only at the completion of the entire sequence 10/08/2015 Input/Output Systems and Peripheral Devices (02-2) 45 Principle of I/O through I/O Processors (3) 10/08/2015 Input/Output Systems and Peripheral Devices (02-2) 46 Principle of I/O through I/O Processors (4) The CPU and IOP can also communicate with each other directly via control lines DMA Request (DMAREQ) DMA Acknowledge (DMAACK) The CPU may attention the IOP by asserting the ATN (Attention) signal execution of an I/O program The IOP may attention the CPU by asserting the IREQ signal execution of an interrupt service routine 10/08/2015 Input/Output Systems and Peripheral Devices (02-2) 47 Principle of I/O through I/O Processors Execution of an I/O Program Intel I/O Processors 10/08/2015 Input/Output Systems and Peripheral Devices (02-2) 48 10/08/2015 Input/Output Systems and Peripheral Devices (02-2) 49 Principle of I/O through I/O Processors Execution of an I/O Program Intel I/O Processors 10/08/2015 Input/Output Systems and Peripheral Devices (02-2) 50 Intended for high-performance servers Designed to maximize the bandwidth of servers’ I/O operations by balancing the data flow Relieving the main processor from the task of executing I/O operations Intercepting the interrupts generated by the peripheral devices 10/08/2015 Input/Output Systems and Peripheral Devices (02-2) 51 In RAID (Redundant Array of Independent Disks) subsystems used to control the parallel transactions and compression algorithms A dedicated controller is more expensive Peer-to-peer technologies Creating an interface between the disk drives and the local network the data flow is managed by the I/O processor 10/08/2015 Input/Output Systems and Peripheral Devices (02-2) 52 IOP321 Contains an interface for the PCI-X bus IOP33x Intended for communication, storage, and networking applications that require I/Ointensive operations Contain an interface for the PCI Express bus with 8 lanes Hardware acceleration of RAID 5 applications 10/08/2015 Input/Output Systems and Peripheral Devices (02-2) 53 IOP341, IOP342 Contain interfaces for the PCI-X and PCI Express buses (8 lanes) IOP348 Designed for storage subsystems SAS/SATA II controller for 8 ports SAS: Serial Attached SCSI SATA: Serial ATA Hardware acceleration of RAID 6 applications 10/08/2015 Input/Output Systems and Peripheral Devices (02-2) 54 Interrupts relieve the CPU from testing the status of I/O devices Two methods for choosing the address of the interrupt handler: nonvectored or vectored interrupts Several techniques are used for identifying the source of interrupt in a multiple-interrupt system The interrupt lines can be connected in parallel or in a daisy-chain 10/08/2015 Input/Output Systems and Peripheral Devices (02-2) 55 The DMA technique allows performing I/O transfers without CPU intervention Two methods for performing DMA transfers: data break (block transfer) or cycle stealing I/O processors (IOPs) have specialized instructions for I/O operations An IOP may execute a sequence of I/O operations without interrupting the CPU The CPU and an IOP communicate via a memory area and via control signals 10/08/2015 Input/Output Systems and Peripheral Devices (02-2) 56 Operations executed by the CPU when detecting an interrupt request Methods for choosing the address of the interrupt handler Nonvectored interrupts Vectored interrupts Techniques for identifying the source of interrupt in a multiple-interrupt system Software polling technique Hardware polling technique 10/08/2015 Input/Output Systems and Peripheral Devices (02-2) 57 Software method for establishing the priority of simultaneous interrupts Hardware method for establishing the priority of simultaneous interrupts Parallel connection of interrupt lines Daisy-chain connection of interrupt lines Principle of I/O through DMA Methods for performing DMA transfers Data-break DMA transfer method 10/08/2015 Input/Output Systems and Peripheral Devices (02-2) 58 Cycle-stealing DMA transfer method Execution of DMA transfers Diagram of circuitry required for DMA transfers and the execution steps of a transfer Principle of I/O through IOP Structure of a computer with IOP CPU-IOP communication Operations for execution of an I/O program 10/08/2015 Input/Output Systems and Peripheral Devices (02-2) 59 1. What are the methods for choosing the address of the interrupt handler? 2. How does the technique of hardware polling work? 3. What are the methods for performing DMA transfers? 4. What is the advantage of I/O through I/O processors compared to DMA? 10/08/2015 Input/Output Systems and Peripheral Devices (02-2) 60