SystemVerilog 2012 New Proposals for Design Engineers

SystemVerilog PAR Meeting - 2010

1 of 37

SystemVerilog 2012

New Proposals for Design Engineers

Clifford E. Cummings

Sunburst Design, Inc.

cliffc@sunburst-design.com

www.sunburst-design.com

World Class Verilog & SystemVerilog Training

Front Lines & Observation

• Have interacted with real users for ~18 years of training

– Verilog ~18 years / Synthesis ~14 years / SystemVerilog ~7 years

• What are the most frequent mistakes made by engineers ?

– What SystemVerilog syntax is non-intuitive?

– What would make it easier to use the language?

• What enhancements would reduce design errors

Priority: Features that:

(1) Are easier to understand

(2) Requires less code

(3) Finds more design bugs

Quote from Dave Rich at DVCon 2010:

These are not enhancement requests ...

... these are long missing features !!

2 of 37 www.sunburst-design.com

1

SystemVerilog PAR Meeting - 2010

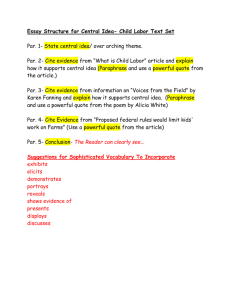

Examples & Syntax

• Important to solve problems - syntax is secondary

• Identify a problem

• Suggest a solution

• Suggest a syntax

... but be prepared to consider alternative syntax solutions

Possible syntax included in examples

Different syntax may be better

3 of 37

Hardware Description Language

• SystemVerilog is supposed to be an HDL

Some constructs are too software-like in their approach

• Think hardware!!

Create constructs and techniques that are intuitive to hardware engineers !!

4 of 37

For designers, let's build a

Hardware Description Language

(not a hardware-aware software language) www.sunburst-design.com

2

SystemVerilog PAR Meeting - 2010

5 of 37

X-Optimism/Pessimism Removal

X-Optimism/Pessimism Removal

Problem Statement

• X-optimism/pessimism is a long-suffered problem in Verilog,

SystemVerilog and VHDL

6 of 37

• Some papers that describe the problem

– Lionel Bening, “Simulation of High Speed Computer Logic,” Proc. 6th

Design Automation Conf., June, 1969

– Lionel Bening, “A Two-State Methodology for RTL Logic Simulation,”

Proc. 36th Design Automation Conf., June, 1999

– Mike Turpin's ARM paper: www.arm.com/pdfs/Verilog_X_Bugs.pdf

NOTE - X 's are not the problem ...

... failure to propagate the X 's is the problem www.sunburst-design.com

3

SystemVerilog PAR Meeting - 2010

7 of 37

X-Optimism/Pessimism Removal

Addressing the Problem

• This problem can be addressed by doing the following: case (expr) inside Included with SystemVerilog-2005

– Addition of case0

– X -detection in testing expressions

– X -assignments if X -detection occurs

Added to SystemVerilog-2009

NEW - trap the X 's

NEW - propagate the X 's

• NOTE: Unwanted X-propagation is a 4-state simulation artifact, not a synthesis problem

8 of 37

X-Optimism/Pessimism Removal

alwaysx Constructs

• Five new X-procedure keywords

• Conditional or loop expressions coded inside of an X-procedure variety that returns a Z or X would do the following:

– Assign X to all variables within the scope of the statement or loop

– Ignore all system tasks and functions

– Perhaps report a warning or error that the tested expression result was X or Z initialx alwaysx always_combx always_ffx always_latchx if ( expr ) case ( expr while (

) expr ) repeat ( expr ) do-while ( expr ) wait -statement may be an exception

(waits indefinitely on X ) for ( expr ; expr ; expr )

X 's are propagated instead of being hidden

Such as $display

Optional: but tools could convert warning into error www.sunburst-design.com

4

SystemVerilog PAR Meeting - 2010

9 of 37

Synthesis of alwaysx Constructs

• SYNTHESIS NOTE: Synthesis tools would treat X-procedures the same as the non-X-procedures

X-procedures would just be synonyms to the synthesis tool

10 of 37

Problem #1 - Fixed

(Source - Mike Turpin - ARM) always_comb

case (sel)

3'b000: clz = 2'b11;

3'b001: clz = 2'b10;

3'b010,

3'b011: clz = 2'b01;

3'b100,

3'b101,

3'b110,

3'b111: clz = 2'b00;

default: clz = 2'bXX;

endcase always_combx

Fixed!

case (sel) inside

3'b000: clz = 2'b11;

3'b001: clz = 2'b10;

3'b01?: clz = 2'b01;

3'b1??: clz = 2'b00;

endcase

Example:

Count leading 0 's

FULL

X -propagation

Problem: for 32 bits, case statement requires 2**32

(429 million lines) of code

If (sel) returns X then clz=2'bXX

No default necessary www.sunburst-design.com

5

SystemVerilog PAR Meeting - 2010

11 of 37

Problem #2 and Fix

(Source - Mike Turpin - ARM)

reg match;

reg [15:0] instr;

case (instr)

16'h014F: match = 1'b1;

16'h152E: match = 1'b1;

<...>

default: match = 1'b0;

endcase always_combx begin

match = '0;

unique0 case (instr)

16'h014F: match = '1;

16'h152E: match = '1;

<...>

endcase end

Example:

Decoder logic - some outputs set high but most set low

X-Optimism Problem: if instr goes to X , match is set to 0

Set common default match='0 always_combx for undefined instr cases sets match='X

DFF Problem and Fix

(Source - Cliff Cummings) always_ff @(posedge clk or negedge rst_n)

if (!rst_n) q <= '0;

else q <= d; X-Optimism Problem: if rst_n uninitialized to X , set q to d

12 of 37

Data is clocked when reset is unknown always_ffx @(posedge clk or negedge rst_n)

if (!rst_n) q <= '0;

else q <= d; always_ffx for undefined rst_n signal sets q='X www.sunburst-design.com

6

SystemVerilog PAR Meeting - 2010

Latch Problem and Fix

(Source - Cliff Cummings) always_latch

if (!rst_n) q <= '0;

else if (en) q <= d; X-Optimism Problem: if rst_n uninitialized to X , set q to d

Data is passed through the latch when reset is unknown

13 of 37 always_latchx

if (!rst_n) q <= '0;

else if (en) q <= d; always_latchx for undefined rst_n signal sets q='X

14 of 37

Connectivity

Engineers and students declare the signal !

www.sunburst-design.com

7

SystemVerilog PAR Meeting - 2010

15 of 37

Verilog-2001 Enhancement:

`default_nettype none

• The default data type for Verilog is: wire

1-bit wire declarations not required wire -port declarations not required

• Verilog-2001 added a new compiler directive argument:

`default_nettype none

Used to turn off the default

Verilog data type

• Forces declaration of all variables

Including all 1-bit wire s and wire port types

• Intended purpose: declaring all variables will help to identify typos in the code

This is debatable!

Simple Design - `default_nettype none

Can Add Errors, Confusion and Frustration!

.

`default_nettype none module testmod3(out1, out1_n,

in1, in2);

output out1, out1_n;

input in1, in2;

wire outl, ou1_n;

wire in1, in2;

wire outO;

Extra typing can add more syntax errors

"Syntax Error: out0 not declared"

"Syntax Error: out1 not declared"

and u1 (out0, in1, in2);

buf u2 (out1, out0);

not u3 (out1_n, out0); endmodule

"Syntax Error: out1_n not declared"

16 of 37

Error messages can add more confusion

These are false error messages in1 in2

Intended logic out0 out1 out1_n

Correct logic - does not compile

Error??

Error??

out1 in1 in2 out0 out1_n

Error??

www.sunburst-design.com

8

SystemVerilog PAR Meeting - 2010

Dangling Signal Checking

• Add the compiler directives

`report_dangles on

`report_dangles off

Can be embedded into code

• Add a command line switch to check the compilation unit for the same potential "dangles" problems

-dangles

Recommended switch name

Exact name is not important

Compiler directives would have precedence over command line switch

17 of 37

Dangling Signal Checking

• Connectivity checking - reports errors when:

– Nets or variables have driver but no receiver

Check all bits of a vector

– Nets or variables have receiver but no driver

Check all bits of a vector

18 of 37

– Nets or variables have no driver(s) OR receiver(s)

Declared net or variable is not in use

Removes clutter from the design www.sunburst-design.com

9

SystemVerilog PAR Meeting - 2010

19 of 37

Connectivity Exceptions

module reg16 (

(output [15:0] dout,

input [15:0] din,

input load, clk, rst_n,

input () scanin,

output () scanout);

...

endmodule

Example: module includes scan input and output that are not connected until layout

Required EMPTY () connections

Error if connected!

module addrdecode (

(output mem1, mem2, ...,

input [15:0] addr,

input en);

wire [9:3] addr ();

...

endmodule

These addr bits are not used this module

Error if connected!

20 of 37

Signed Operators

www.sunburst-design.com

10

SystemVerilog PAR Meeting - 2010

Signed Data Types ???

• No such thing as signed data types

• Verilog-2001 signed arithmetic is broken

Does not exist in real hardware

Lots of gotchas

21 of 37

Signed Operators

Thanks Elliott Mednick !!

• Create signed operators

– Examples

Unsigned multiplication: prod = a * b;

Unsigned addition: sum = a + b + ci;

– Example proposed solution

Signed multiplication: prod = a <*> b;

Signed addition: sum = a <+> b <+> ci;

No signed data types required

Closer to real hardware www.sunburst-design.com

11

22 of 37

SystemVerilog PAR Meeting - 2010

23 of 37

Signed Operators with Options

• Signed operators might optionally refer to existing standards

– Example proposed solution

Signed multiplication using IEEE Floating Point: prod = a <*, ieee-fp> b;

Useful operator types could be extended as needed

Use of Variable Types Vs. Net Types

Annoying Verilog Requirements

• Variable types are only assigned inside of procedural blocks

A very silly rule!

Procedural assignment:

LHS must be a variable type reg [8:0] sum; always @(a or b)

sum = a + b;

24 of 37

• Net types are assigned or driven outside of procedural blocks wire [8:0] sum; assign sum = a + b;

Continuous assignment:

LHS must be a net type wire y; and g1 (y, c, d);

Gate primitive: output must be a net type wire n1; mydff u1 (.q(n1), .d(n2), .clk(clk));

Module instance: output must be a net type www.sunburst-design.com

12

SystemVerilog PAR Meeting - 2010

25 of 37

SystemVerilog Unresolved Type - logic

• logic is roughly equivalent to the VHDL std_ulogic type

– Either: permits only a single driving source -OR-

Unresolved procedural assignments from one or more procedural blocks

Illegal to make both continuous assignments and procedural assignments to the same variable logic is a 4-state type bit is an equivalent unresolved 2-state type

• wire net type still required for:

– Multiply driven buses (such as bus crossbars and onehot muxes)

– Bi-directional buses (more than one driving source)

26 of 37

The logic Data Type

First Usage Determines Legal Usage

• SystemVerilog-2005

– logic : Near-universal data type for unresolved assignments

First-usage determined behavior of the variable y1 and y2 are declared to be

SystemVerilog logic -variables module dual_mux (

output logic y1, y2,

input logic in1a, in1b, sel1a

input logic in2a, in2b, sel2a);

always_comb begin

if (sel1a) y1 = in1a;

else y1 = in1b;

end

assign y2 = sel2a ? in2a : in2b; endmodule y1 is treated like a

Verilog reg -variable y2 is treated like a

Verilog wire

EASY to move assignments between always and assign www.sunburst-design.com

13

SystemVerilog PAR Meeting - 2010

27 of 37

The wire Data Type

Let First Usage Determines Legal Usage

• Proposal:

– wire : Near-universal data type for resolved assignments!!

First-usage SHOULD determine behavior of the wire -type y1 and y2 would default to be

SystemVerilog wire -"variables" module dual_mux (

output y1, y2,

input in1a, in1b, sel1a

input in2a, in2b, sel2a);

always_comb begin

if (sel1a) y1 = in1a;

else y1 = in1b;

end

assign y2 = sel2a ? in2a : in2b; endmodule y1 is treated like a

Verilog reg -variable y2 is treated like a

Verilog wire

EASY to move assignments between always and assign

New Type-Behavior Is Intuitive

Easier Use-Model For Design Engineers

• Users would have a universal data type:

– logic : unresolved data type

– wire : resolved data type wire "variables" are fully backward compatible reg data type usage would finally die"

28 of 37

• Solves the old reg -vs- wire confusion

Verilogs reg -vs- wire data type rules are confusing new users

Verilogs reg -vs- wire data type rules are confusing to design engineers

VHDL engineers ridicule Verilog's reg -vs- wire

(no such distinction in VHDL) www.sunburst-design.com

14

SystemVerilog PAR Meeting - 2010

29 of 37

`default_nettype logic

Or Equivalent Declaration

• The ability to change the default type to a non-net-type is very desirable

`default_nettype logic would be a typical choice

• Perhaps `default_type would have been better

`default_nettype is good enough

• Mantis 1747 suggests a different syntax for ports

`default_nettype ports_only wire

`default_porttype wire

Would be useful to allow logic "nettype"

30 of 37

`default_nettype off

Or Equivalent Declaration

• The ability to turn off a `default_nettype would be useful

• `default_nettype off could be an option

Alternative option #1

`default_nettype revert

Alternative option #2

`default_nettype go_back_to_the_way_it_was

• Disabling a local `default_nettype is important to IP

IP developers do not want their models to corrupt a customer environment www.sunburst-design.com

15

SystemVerilog PAR Meeting - 2010

31 of 37

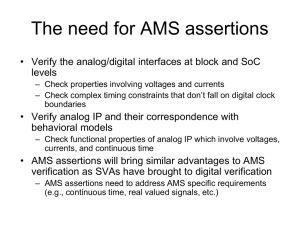

Verification Language Enhancements

e-Language User Topics

• when inheritance Not just AOP

BIGGEST complaint from e-Users who are forced to use SystemVerilog

• extend enumerated types Complaint from e-Users

• Reuse of enumerated names

• Soft constraints

Not just e-Users

• Allow extending of covergroups

Complaint from e-Users

Very common request from

all verification engineers

32 of 37

Reproducible Randomization of Initial States

• Cummings/Bening paper on 2-state simulations

Randomization of initial states helps detect a new class of bugs

2004 Boston SNUG paper www.sunburst-design.com/papers

• HP holds a patent on this capability

I think HP might be willing to donate the patent

This enhancement helps find bugs !!

www.sunburst-design.com

16

SystemVerilog PAR Meeting - 2010

33 of 37

always-assign Race Removal

• Multiple engineers have experienced always assign races

Most engineers submit this as a simulator bug

(not a bug!)

Cliff tells users the simulator is IEEE compliant and this is a known legal-race

• Add to required event scheduling:

– When 0-delay procedure starts, it must complete before executing other drivers or procedures

– Vendors can suspend procedure execution only if the behavior is the same as uninterrupted procedures

95% of procedures can be suspended without adding race conditions

34 of 37

Declarations & Instantiation

• Engineers do funny things to avoid declarations

Common to see continuous assignments via wire declarations

• SV-2005 .* port connections

Verilog Emacs mode expands these signals

• Remove requirement to declare 1-bit wires Implicit wires with .*

Many engineers want to remove requirement to declare internal buses

• Regular expressions using .* and port connections

Verilog Emacs mode has this capability www.sunburst-design.com

17

SystemVerilog PAR Meeting - 2010

35 of 37

$all_signals

• Primarily intended for use with assertions and clocking blocks

Other applications might also benefit

Returns a list of all signals in the scope concatenated into a single vector

• Useful system function

$all_signals

$all_inputs

$all_outputs

$all_inouts

Returns a list of all inpts in the scope concatenated into a single vector

Returns a list of all outputs in the scope concatenated into a single vector

Returns a list of all inouts in the scope concatenated into a single vector

• Allow exceptions to be removed

$all_signals(-sig1, sig2);

All signals EXCEPT sig1 & sig2

36 of 37

ANSI Style Port & Parameter Lists

Allow Both Commas, and Semicolons; module pipeline #(DEPTH=5, DWIDTH=16)

(output logic [DWIDTH-1:0] dout,

input logic [DWIDTH-1:0] din,

input clk, rst_n);

wire [DWIDTH-1:0] n [0:DEPTH];

genvar i;

Request from Microchip

(Don Mills)

assign n[0] = din;

assign dout = n[DEPTH];

generate for (i=0; i<DEPTH; i++) begin: p

Microchip has a large number of parameter files

preg8 g (.q(n[i+1]), .d(n[i]), .clk(clk), .rst_n(rst_n));

end endgenerate endmodule

File: mc_params.v

module pipeline #(`include "mc_params.v")

(output logic [DWIDTH-1:0] dout, parameter DEPTH=5; parameter DWIDTH=16;

input logic [DWIDTH-1:0] din,

input clk, rst_n);

...

www.sunburst-design.com

18

SystemVerilog PAR Meeting - 2010

37 of 37

Miscellaneous Other Designer Requests

• Treat Verilog-2001 attributes likes strings

(* synthesis, async_set_reset = "sig_name1, sig_name2, ..." *)

(* synthesis, black_box [ =<optional_value>] *)

(* UPF, upf_option *)

(* layout, layout_option *)

Allows easy insertion of tool information

• Fix UDP event scheduling for reg-declared UDPs

UDPs with a reg declarations should update in the NBA region

UDP latches and flip-flops have race conditions in some simulators

• Intentional bit-reversal logic [7:0] data;

...

data[7:0] = data[@0:7] ;

This shows that the reversal is intentional

38 of 37

SystemVerilog 2012

New Proposals for Design Engineers

Clifford E. Cummings

Sunburst Design, Inc.

cliffc@sunburst-design.com

www.sunburst-design.com

World Class Verilog & SystemVerilog Training www.sunburst-design.com

19