Exclusive OR/ Exclusive NOR Tables for XOR/XNOR

advertisement

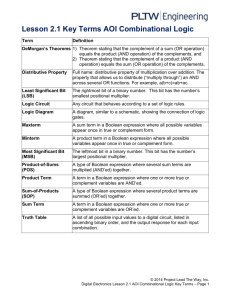

Goals for Lecture ECE 20B, Winter 2003 Introduction to Electrical Engineering, II LECTURE NOTES #5 Instructor: Andrew B. Kahng (lecture) Email: abk@ece.ucsd.edu Telephone: 858-822-4884 office, 858-353-0550 cell Office: 3802 AP&M Office Hours: MW noon-1pm XOR/XNOR Combinational Logic Blocks Class Website: http://vlsicad.ucsd.edu/courses/ece20b/wi03 1 Exclusive OR/ Exclusive NOR Tables for XOR/XNOR The eXclusive OR (XOR) function is an important Boolean function used extensively in logic circuits. Uses for the XOR gate include: – – – – 2 Operator Rules: XOR Adders/subtractors Parity generators/checkers Signature analyzers Pseudo-random sequence generators Definitions – The XOR function is: X ⊕ Y = XY + X Y – The eXclusive NOR (XNOR) function, otherwise known as Equivalence is: X ⊕ Y = XY + XY X Y 0 0 0 1 1 1 0 1 XNOR X⊕Y 0 1 1 0 0 0 Y X⊕Y 0 1 1 0 1 1 0 1 X 0 1 The XOR function means: X OR Y, but NOT BOTH The XNOR function, denoted by the operator ≡, is also known as the Equivalence function. 3 XOR/XNOR Extension 4 XOR Implementations The XOR function can be extended to 3 or more variables. For more than 2 variables, it is called a modulo 2 sum (Mod 2 sum), instead of XOR: The simple SOP implementation uses the following structure: X X ⊕ Y ⊕ Z = X YZ + XY Z + X Y Z + XYZ The XOR definition, Boolean identities and Boolean theorems give: X Y Y A NAND only implementation is: X ⊕0= X X ⊕1= X X⊕X =0 X⊕X =1 X⊕Y = X⊕Y X⊕Y = X⊕Y X ⊕Y = Y⊕X (X ⊕ Y ) ⊕ Z = X ⊕ (Y ⊕ Z ) = X ⊕ Y ⊕ Z X X 5 Y Y 6 1 XOR Implementations (Cont.) Odd Function The AND-OR implementation is the SOP form for the XOR function: The modulo 2 sum function for n variables X ⊕ Y = XY + X Y The multiple-level NAND implementation can be derived by combining inversions as follows: The inverse of the modulo 2 sum function for n variables – Contains an odd number of 1’s, and – Is therefore called the odd function. – Contains an even number of 1’s, and – Is therefore called the even function. X ⊕ Y = XY + X Y Implementation of even and odd functions for greater than 4 variables as a single gate is difficult, so “trees” of 2 to 4 input XOR or XNORs are used. = XY + X Y = XY + X Y = XY ⋅ (X + Y) = XY ⋅ X + XY ⋅ Y 7 Example: Odd Function Implementation Three-Input Odd Function: 8 Product terms of Odd and Even For an n-bit even or odd function, there will be (2n)/2 or 2n – 1 w product terms of n variables (minterms)! y 1 1 1 1 1 1 1 1 x w 1 1 1 z z Even Function y 1 1 1 1 y v=1 1 1 x 1 1 Odd Function 1 w 1 1 v=0 Four Input Odd Function: y 1 1 1 x 1 1 w 1 1 1 z 1 x 1 z Odd Function of Five Bits 9 Parity Generators/Checkers Positive and Negative Logic The same physical gate has different logical meanings depending on interpretation of the signal levels. Positive Logic A parity tree for n data bits generates a parity bit that is appended to the data bits to form an n + 1X bit codeword Y Example: 3-bit even P parity generator – Logic 1 is set to HIGH (more positive) signal levels – Logic 0 is set to LOW (less positive) signal levels Z A parity tree for n + 1 bits checks the codeword for correct parity: – C=0 if the codeword parity is correct – C=1 if the codeword parity is Incorrect Example: 4-bit even parity checker 10 Negative Logic – Logic 1 is set to LOW (more negative) signal levels – Logic 0 is set to HIGH (less negative) signal levels X Y A gate which implements a Positive Logic AND function will implement a Negative Logic OR function. C Z P 11 12 2 Design Hierarchy (MK 3.1) Hierarchical Design The function mapping inputs to outputs may be very complex Combinational Circuits A combinational logic circuit has: – To control complexity, we decompose the function into smaller pieces called blocks – The blocks are subdivided into finer blocks – The "leaves” in the hierarchy are called primitive blocks – A set of m Boolean inputs, – A set of n Boolean outputs, and – n switching functions mapping the 2n input combinations to a output such that the current output depends only on the current inputs. Example: 16 input parity tree – – – – – A block diagram: Combinational Logic Circuit m Boolean Inputs Top Level: 16 inputs, one output 2nd Level: Five 4-bit parity trees in two levels 3rd Level: Three 2-bit exclusive-OR functions Primitive level: Four 2-input NANDs The design requires 5 X 3 X 4 = 60 two-input NAND gates n Boolean Outputs 13 Reusable Functions and Design What is “Design (Technology)”? Whenever possible, we try to decompose a complex design into common, reusable function blocks These blocks are tested and well documented Computer-aided design (CAD) tools might include them in libraries Computer-aided manufacturing (CAM) tools might know how to manufacture and test them Other tools: – – – – 14 Schematic Capture Logic Simulators Timing Verifiers Hardware Description Languages (HDL) Design = specification, synthesis, analysis – What do I want? – Create – Check Design Technology = Technology that enables design to occur in a timely, costeffective way – (What happens if we can’t design new products quickly?) Libraries Tools Methods 15 Top-Down versus Bottom-Up 16 Analysis Procedure A Top-Down design proceeds from an abstract, high level specification to a more and more detailed design by decomposition and successive refinement A Bottom-Up design starts with detailed primitive elements and combines them into larger and larger and more complex functions Designs usually proceed from both directions simultaneously – Top-Down design answers: What are we building? – Bottom-Up design answers: How do we build it? Top-Down controls complexity while Bottom-Up controls the details 17 Switching Functions from Logic Diagrams Given a logic diagram, the analysis process provides a set of Boolean equations, a truth table, or a verbal explanation of circuit behavior. Procedure: 1. Determine that the circuit is combinational (no feedback loops), then: 2. Identify and label all gate outputs that are a function of the input variables. Obtain the Boolean functions for these labeled gate outputs. 3. Identify and label all gate outputs that are a function of inputs or previously labeled gates. Obtain Boolean functions for them. 4. Repeat Step 2 until all outputs are completed. 5. Back substitute until all functions are specified in terms of inputs only. 18 3 Analysis Example Step 2: Label all outputs of gates near inputs. Analysis (Continued) A F B F T1 C T4 D C T3 B D T2 E B E Write Boolean equations for them:A F T1 B C T1 = B + C T2 = B E A B Step 3: Identify and label all gate outputs that are a function of inputs or previously labeled gates. Obtain Boolean functions for them. T3 = D + T2 D Step 4: Repeat Step 3 until all done B E T4 = T1 T3 F = A + T4 T2 19 Analysis Example: Code Converter Analysis (Continued) A B F T1 C D C F2 F1 T3 B E B A T4 D 20 T2 w x F0 z Step 4: Back substitute until all functions are specified in terms of inputs only F = A + T4 T3 = D + T2 T1 = B + C y T4 = T1 T3 T2 = B ⋅ E Substituting: T 3 = D + ( B ⋅ E) T 4 = ( B + C) ( D + ( B E)) F = A + ( B + C) ( D + ( B E)) 21 Truth Tables from Logic Diagrams 22 Truth Tables from Logic Diagrams 1. Determine the number of input variables, n. There will be 2n input vectors from zero to 2(n-1). Enter them in the table. 2. Label the outputs of selected gates with symbols and enter a column for each one in the table. 3. Obtain the truth table for the outputs of those gates that are a function of only input variables. 4. Proceed to fill in the outputs of all gates that are derived from inputs and previously calculated terms. Procedure: – Determine the number of input variables, n. There will be 2n input vectors from zero to 2n – 1. Enter them in the table. – Label the outputs of selected gates with symbols and enter a column for each one in the table. – Obtain the truth table for the outputs of those gates that are a function of only input variables. – Proceed to fill in the outputs of all gates that are derived from inputs and previously calculated terms. Example: Find the function table for the code converter. 23 24 4 Code Converter Truth Table Four inputs give 16 input vectors. Start with F0, F1 and z. ABCD F0 0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 1010 1011 1100 1101 1110 1111 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 F1 F2 Truth Table Fill-in w x y Now we can calculate x, y, and F2. z 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 ABCD F0 F1 F2 0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 1010 1011 1100 1101 1110 1111 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 0 1 1 1 0 1 1 1 0 1 1 1 0 1 1 1 0 1 1 1 1 1 1 1 0 1 1 1 1 1 1 1 w x y z 0 1 1 1 1 0 0 0 0 1 1 1 1 0 0 0 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 25 26 Complete Entries Finally we can fill in w to complete the table: What Does the Circuit Do? ABCD F0 F1 0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 1010 1011 1100 1101 1110 1111 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 0 1 1 1 0 1 1 1 0 1 1 1 0 1 1 1 By inspection, the output variable vector (w,x,y,z) is just the input variable vector (A,B,C,D) plus three. The function(s) F(A,B,C,D) = (w,x,y,z) are: “ADD THREE TO THE INPUT VECTOR” Function F1 has the meaning: “ADD ONE TO THE UPPER TWO BITS” Similarly, function F2 has the meaning: “ADD ONE TO THE UPPER BIT” Generally, it is not this obvious to figure out what the functions mean F2 w x y z 0 1 1 1 1 1 1 1 0 1 1 1 1 1 1 1 0 0 0 0 0 1 1 1 1 1 1 1 1 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 0 0 0 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 27 28 Logic Design: Functional Blocks Final Note (and warning) The use of "Don't Cares" in the original specification can cloud the analysis. Analysis: From a design to a specification of the behavior – Note that the functions for the "w" bit differ from the implementation in Ex. 3-2 of the book. – The book used "Don't Cares" to simplify the logic. The example here did not. – This can be seen C w w C by inspecting the 0 1 3 2 0 1 3 2 two K-maps for 15 1 7 1 6 15 1 7 1 6 4 the function w: 4 B A X12 X13 X15 X14 1 8 1 9 X11 X10 D Book Fig. 4-8 A 112 13 15 – Logic diagram to equations – Logic diagram to function table – "Word description" of circuit operation Synthesis: From a specification to design implementation B 14 1 8 1 9 111 1 10 D Notes Example 29 – – – – Define the problem Generate function table or equations Minimize the Boolean function Implement the circuit 30 5 Design Procedure (MK 3.4) Combinational Logic Implementation A combinational logic circuit has: First, start with the specification of the circuit to be designed. – A set of m Boolean inputs, – A set of n Boolean outputs, and – A function mapping inputs to outputs. – Note: this can sometimes require a lot of work to complete the specification process, especially if it is poorly specified initially We think of the function as n separate Boolean functions of m inputs Procedure: – – – – Treat each output as a separate function Minimize the equations for each function Implement each function independently Sometimes an implementation can share product or sum logic terms to arrive at a lower literal cost solution. Second, follow these steps: We will study the design of a code converter to see these steps. – – – – – Identify the inputs and outputs Derive truth table Obtain simplified Boolean equations Draw the logic diagram Check your work to verify correctness 31 32 Example: BCD to Excess 3 Code Converter Design Example A code converter transforms one internal representation of data to another We will start with a table of the desired conversion and minimize the resulting multiple output Boolean function Sometimes terms can be shared to minimize the implementation cost The Problem: Function table: – Design a BCD to Excess-3 code converter – Specification: • BCD code -- 4-bit patterns "0000" to "1001" for digits 0 to 9 base 10 • Excess-3 -- BCD code plus binary "0011" for digits 0 to 9 base 10 33 Example (Cont.): BCD to Excess 3 Map functions z and find minimum cost SOP equations for each A C 1 3 12 14 5 7 16 X12 X13 X15 X14 18 B A X11 X10 9 1 13 2 14 5 17 6 0 14 A 7 6 X12 X13 X15 X14 8 1 9 X11 X10 D C w 11 1 3 1 2 5 X11 X10 9 D C x All BCD codes greater than "9" can be assigned "Don't Cares" in the K-Map. Such BCD codes are never possible. 34 B X12 X13 X15 X14 D Note: Next, we will manipulate the equations to expose some shared terms: C 10 18 Output Excess-3 wxyz 0011 0100 0101 0110 0111 1000 1001 1010 1011 1011 Example (Cont.): BCD to Excess 3 y 10 Input BCD ABCD 0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 0 4 B A 1 3 2 15 1 7 1 6 X12 X13 X15 X14 1 8 1 9 X11 X10 D 35 B The term (C + D) can be used more than once to simplify the implementation See Fig. 3-10 in Mano and Kime for the implementation 36 6 2-to-4 Line Decoder Functional Block: Decoders (MK 3.5) 2n A Decoder converts n binary bits to a maximum of unique output lines. An m-to-n line decoder, where m < 2n, can be used to: Generate 2n (or fewer) minterms Select one-of 2n items Decoders are sometimes known as demultiplexers when enabled with a separate data-in line. This device takes: n=2 input lines and decodes minterms for: m=2n= 4 output lines. A A B A B A B A B B 37 38 Implementing Logic with Decoders 2-to-4 Line Demultiplexer This device takes: X n=2 input lines and decodes minterms for: m=22 =4 output lines where each output is: ANDed with an input, X. If X is viewed as an Enable, all outputs are 0 for X = 0 and one output is 1 for X = 1. If X is viewed as Data, then this data is sent to one or the outputs. A A B X A B X A B X A B X Decoders provide minterms directly. Simply "OR" the appropriate minterm outputs to make any logic function desired. Active low decoders behave as the first NAND gate in a NAND-NAND, Sum of Products implementation. Active high decoders behave as first stage AND gates in a AND-OR Sum of Products implementation. Two or more active high decoders driven from different bits of a binary code can be used to form minterms by "ANDING" their outputs. Similarly, active low decoders can be used to form minterms by "ORING" their outputs. B 39 40 Example: F(X,Y,Z) = ∑m(0,3,5,6) Example: F(A,B) = ∑m(0,3) For this we use a 2-to-4 line decoder and sum minterms 0 and 3 with an OR gate: m3 F m0 A B 41 42 7 Implementing Larger Minterms Minterm m15 is formed by "ANDING" the D3 outputs of each decoder. Similarly m0 is formed by A "ANDING" the D0 outputs of B each decoder. D3 D2 S1 D1 S0 D0 What minterm is formed by "ANDING" D1 (upper) and D2 (lower) outputs? C S1 D1 D S0 D0 Functional Block: Encoders (MK 3.6) m15 m?? D3 D2 m0 Encoders perform the "inverse" operation of decoders, taking a code in one format and encoding it into another format. Many encoders consist of just OR gates. For example an 8-to-3 binary encoder consists of three 4-input OR gates, OR2 ,OR1 and OR0. Input Ii, i = 0,…,7 is connected to an input on ORj if the binary representation of i has a 1 in position j. A priority encoder is used to generate a code for the "most significant" bit set in a string of bits. This can be used to find the first one in a word, or to select external events in priority order. An example of a MSI priority encoder is the 74F148, 8 line to 3 line priority encoder. It can be cascaded to encode higher numbers of bits. This works best with widely scattered, sparse minterms. 43 Encoder Example 44 Review: Decoders and Encoders Encode 4 lines 0, 1, 2, 3 into the corresponding binary codes. A Decoder converts n binary bits to a maximum of 2n unique output lines. Decoders are sometimes know as demultiplexers when enabled with a separate data-in line. Decoders implement minterms directly. Use a decoder and an OR gate to form Sum-of-Minterms directly. Encoders perform the "inverse" operation of decoders, taking a code in one format and encoding it into another format. 45 Multiplexers (MK 3.7) 46 Example: A 4-to-1 multiplexer A Multiplexer (MUX) is another common functional block. The 4-to-1 line Multiplexer uses the same minterm decoder core. A Multiplexer uses n binary select bits to choose n from a maximum of 2 unique input lines. Like a decoder, it decodes minterms internally. It is like a demultiplexer with individual data input lines (instead of just one) and an output OR gate. Unlike a decoder, it has only one output line. The decoded minterms are used to select data n from one of up to 2 unique data input lines. I3 I2 X I1 I0 S1 The output of the multiplexer is the data input whose index is specified by the n bit code. S0 47 48 8 Functions with Multiplexers Multiplexer Versus Decoder I3 X A B X I2 A B X X I1 A B X I0 S1 A S0 B A B X Simply tie each input to the "1" or "0" line as desired. It is also possible to implement any n+1 variable n function with a 2 multiplexer. Simply use the (n+1)st variable in true or complement form depending upon what the truth table requires. A Boolean function of more than n variables can be partitioned into several easily implemented subfunctions defined on a subset of the variables. The multiplexer will then select among these subfunctions. Note how similar the two are internally. 49 Example: Gray to Binary Code Gray ABC 000 100 110 010 011 111 101 001 The Gray code has adjacent elements separated by only one bit change. We wish to convert a 3-bit Gray code to a binary code. The function table on the right documents the required conversion. ⇒ It is possible to implement any Boolean function of n n variables with a 2 input multiplexer. 50 Gray to Binary (Continued) Binary xyz 000 001 010 011 100 101 110 111 First step: Let's get the function table into a logical order by reordering the input Gray code values in binary sequence: ⇒ Gray ABC 000 001 010 011 100 101 110 111 By inspection: x = F(A,B,C) = ∑m(1, 3, 5, 7) y = G(A,B,C) = ∑m(1, 2, 5, 6) z = H(A,B,C) = ∑m(1, 2, 4, 7) The Gray to Binary Code Converter requires us to implement three separate, three-input Boolean functions. Binary xyz 000 111 011 100 001 110 010 101 51 52 Gray to Binary (Continued) Gray to Binary (Continued) The K-Maps We know that 2n to 1 Multiplexers can be used to implement arbitrary functions of n bits. We simply connect the inputs to "0" or "1" as needed. B X 0 A 4 11 1 1 1 5 3 7 6 C 0 1 4 1 1 3 17 5 C A 0 1 4 15 1 3 7 12 1 Use two eightinput multiplexers to implement functions for y and z: ⇒ 16 C B Z A B Y 2 12 6 Note: x(A,B,C) = C, is an easy function to implement. (No logic gates needed!) Function y(A,B,C) = B'C + B'C is a bit harder to implement. Function z(A,B,C) looks familiar. What is it? 0 0 1 0 1 1 0 A B C D7 D6 D5 D4 D3 D2 D1 D0 S2 S1 S0 0 Out 8-to-1 MUX 1 1 0 0 1 1 0 Z A B C D7 D6 D5 D4 D3 D2 D1 D0 S2 S1 S0 Y Out 8-to-1 MUX In this case, the MUX elements are acting like a "Read Only Memory" (ROM). 53 54 9 Other MUX Implementations MUX Implementations (Cont.) We can also use two 4-to-1 MUX blocks and implement y and z. Suppose we factor out A and use B and C as the select inputs to the multiplexers Factoring out variable A leads to the following implementation with two, 4-to-1 Multiplexers: A 11 B 10 00 01 0 1 D0 D1 0 1 0 D3 0 Y Z 1 D2 1 A 11 B 10 00 01 0 1 D0 D1 1 0 C A A' A' A 0 D3 1 1 D2 0 A A B C A S1 S0 Out 0 1 1 0 Z 4-to-1 MUX B C D3 D2 D1 D0 S1 S0 Out 4-to-1 MUX 55 MUX: (Cont.) Factoring Out C 0 1 0 1 0 1 0 1 x D0 = C D1 = C D2 = C D3 = C Binary y 0 D0 = C 1 1 D1 = C' 0 0 D2 = C 1 0 D3 = C' 0 0 1 1 0 1 0 0 1 56 MUX: (Cont.) Factoring out B We could have factored out other variables. As in the book, we will factor out C and apply AB to the select inputs: Gray ABC 000 001 010 011 100 101 110 111 z D0 = C D1 = C' D2 = C' D3 = C Gray ABC 000 010 00 1 0 11 1 00 11 0 101 111 x 0 x = "0" 0 0 1 1 x = "1" 1 1 0 0 x = "0" 0 0 1 1 x = "1" 1 1 0 Binary y y=B y = B' y=B y = B' 0 1 1 0 1 0 0 1 z z=B z = B' z = B' z=B Note: We re-arranged the table (fixing A and C and varying B from 0 to 1 in each cell) to simplify this procedure. It still looks like factoring A was better. This is slightly larger than selecting A to factor out. 57 MUX: (Cont.) Factoring out A Gray ABC 000 1 00 00 1 101 010 11 0 0 11 111 x 0 D0 = 0 0 1 D1 = 1 1 0 D2 = 0 0 1 D3 = 1 1 Binary y 0 D0 = 0 0 0 1 1 D1 = 1 1 1 0 1 D2 = 1 1 1 0 0 D3 = 0 0 0 1 Y As before, x = C. C A D3 D2 D1 D0 58 Summary Know the functions performed by the following functional blocks: z D0 = A – Decoders – Demultiplexers – Encoders – Multiplexers D1 = A' D2 = A' Know how to implement Boolean functions using: D3 = A Note: We re-arranged the table (fixing B and C and varying A from 0 to 1 in each cell) to simplify this procedure. Factoring A is best! Note also that x = C holds. 59 – Multiplexers – Decoders 60 10 Functional Blocks: Addition Functional Block: Half-Adder A 2-input, 1-bit width binary adder that produces the following values: Binary addition occurs frequently in digital and computer systems. In this section, we: – Develop a Half-Adder (HA), a 2-input bitwise addition functional block, – Develop a Full-Adder (FA), a 3-input bitwise addition functional block, – Iterate full-adders using a ripple-carry to perform parallel binary addition, and – Develop a Carry-Look-Ahead Adder CLA to improve performance. Logic Simplification: Half-Adder S S= X ⋅Y + X ⋅Y = X ⊕ Y S = (X + Y ) ⋅ (X + Y ) X 0 12 3 Y X 0 1 2 13 CS 00 01 01 10 C 0 0 0 1 S 0 1 1 62 0 (a), (b), and (e) are SOP, POS, and XOR implementations for S. These equations lead to several implementations. In (c), the C function is used as a term in the ANDNOR implementation of S, and in (d), the C function is used in a POS term for S. 63 64 Implementations: Half-Adder The most common half adder implementation (e) is: Functional Block: Full-Adder A full adder is similar to a half adder, but includes a carry-in bit from lower stages. Like the halfadder, it computes a sum bit, S and a carry bit, C. C – For a carry-in (Z) of zero, it is the same as the half-adder: ⇒ X S Y C X S = (X + Y )C C = (( X Y )) 1 +1 C = (X + Y ) C = XY ( b) S = ( X + Y ) ( X + Y ) ( e) S = X⊕Y C = XY C = XY ( c) S = ( C + X Y ) C = XY C = X ⋅Y C = ( ( X ⋅Y ) ) A NAND only implementation (equivalent to equation d) is: 1 +0 We can derive following sets of equations for a half-adder: (d ) S = ( X + Y ) C ( a) S = X Y + X Y and S= X ⊕ Y C = X ⋅Y 0 +1 Five Implementations: Half-Adder C Y 11 0 +0 A half adder adds two bits to produce a two-bit sum. X Y The sum is expressed as a 0 0 sum bit , S and a carry bit, C. The half adder can be specified 0 1 as a combined truth table 1 0 for S and C: ⇒ 1 1 61 The K-Map for S, C is: This is a pretty trivial map! By inspection: X +Y S C Y 65 – For a carry- in (Z) of one: ⇒ Z X +Y 0 0 +0 0 0 +1 0 1 +0 0 1 +1 CS 00 01 01 10 Z X +Y 1 0 +0 1 0 +1 1 1 +0 1 1 +1 CS 01 10 10 11 66 11 Design: Full-Adder Design: Full-Adder Full-Adder Function Table: ⇒ X Y Z 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1 Full-Adder K-Map: S C Y 0 X 1 4 1 1 5 3 1 1 7 From the K-Map, we get: S= X Y Z +X Y Z +X Y Z +X Y Z C = X Y +X Z +Y Z S 0 1 1 0 1 0 0 1 The S function is the three-bit XOR function (Odd Function): S = X ⊕ Y⊕ Z The Carry bit C is 1 if both X and Y are 1 (the sum is 2), or if the sum is 1 and a carry-in (Z) occurs. Thus C can be re-written as: C = X Y + ( X ⊕ Y) Z Y 2 0 X 6 C 0 0 0 1 0 1 1 1 1 1 1 4 Z 1 5 3 7 1 2 The term X·Y is carry generate. 6 The term X⊕Y is carry propagate. Z 67 68 Implementation: Full Adder Full Adder Schematic ⇒ Parallel Binary Adders G Co A P S B Ci Here X, Y, and Z, and C (from the previous pages) are A, B, Ci and Co respectively. Also, G = Generate and P = Propagate. Note: This is really a combination of a 3-bit odd function (for S = sum) and Carry logic: To add more than one bit, we "bundle" sets of logical signals together and build devices that operate on the whole set in parallel. Example: 4-bit binary adder: Adds an input vector "A(3..0) " to "B(3..0)“ to get a sum S(3..0) thus: ⇒ Note: the carry out of Stage i becomes the carry in of Stage i+1. Description Subscript Name 3210 Input Carry 0110 Ci Augend 1011 Ai Addend 0011 Bi Sum 1110 Si Output Carry 0011 Ci+1 (G = Generate) OR (P =Propagate AND Ci = Carry In) Co = G + P · Ci 69 Carry Propagation & Delay 4-bit Ripple-Carry Binary Adder A four-bit Full Adder made from four 1-bit Full Adders: ⇒ A(2) B(2) A(3) B(3) C(4) x Co y FA S S(3) Ci C(3) x Co y FA Ci C(2) S S(2) Here FA is a Full-Adder from before: ⇒ A(1) B(1) x Co y FA Ci 70 A(0) B(0) x C(1) Co S y Ci FA One problem with the addition of binary numbers is the length of time to propagate the ripple carry from the least significant bit to the most significant bit. The gate-level propagation path for a 4-bit ripple carry adder of the last example: A(3) B(3) C(0) A(2) B(2) A(1) B(1) A(0) B(0) S C(3) S(0) S(1) P S Ci C(1) C(0) C(4) G Co C(2) S(3) A B 71 S(2) S(1) S(0) Note: The "long path" is from A(0) or B(0) though the network to either C(4) or S(3). 72 12 Carry Look-Ahead Carry Look-Ahead (Continued) Given Stage i from a Full Adder, we know that there will be a carry generated when Ai = Bi = "1", whether or not there is a carry-in. Ai Alternately, there will be Bi a carry propagated if the Gi "Half-Sum" is "1" and a carry-in, Ci occurs. Pi These two signal conditions Ci are called Generate denoted as Gi, and Propagate denoted as Pi respectively and are Ci+1 Si shown here: ⇒ By defining the equations for the Full Adder in term of the Pi and Gi, we have: Pi = A i ⊕ Bi G i = A i Bi And the output sum S(i) and carry C(i+1) is defined as: Si = Pi ⊕ Ci Ci +1 = G i + Pi Ci Starting the stage numbering at zero, we have: C4 = G 3 + P3 G 2 + P3 P2 G1 + P3 P2 P1 G 0 + P3 P2 P1 P0 C0 where C0 is a carry in to the least significant bit. 73 Group Carry Look-Ahead Logic Carry Look-Ahead (Continued) Look at the following addition examples, all of which generate a carry of 1 out of 1xxx +1xxx the third stage: 1xxxx 74 Figure 3-28 in the text shows how to implement a carry look-ahead circuit for four bits. This could be extended to more than four bits. In practice, though, it becomes more difficult to implement this over more than a few bits. The concept can be extended another level by considering a Group Generate (G 0-3) and Group Propagate (P 0-3) logic condition: Generate a carry in Stage3 11xx +01xx 10xxx Generate a carry in Stage2 and propagate it through Stage3 111x +001x 100xx Generate a carry in Stage1 and propagate it through Stage2 and Stage3 1111 +0001 1000x Generate a carry in Stage0 and propagate it through Stage1, Stage2 and Stage3 1111 +0000 10000 Use a carry into Stage0 and propagate it through Stage0, Stage1, Stage2 and Stage3 75 Complements G0- 3 = G 3 + P3 G 2 + P3 P2 G1 + P3 P2 P1 P0 G0 P0- 3 = P3 P2 P1 P0 Using these two equations: C4 = G 0- 3 + P0- 3 C0 Thus, it is possible to have four 4-bit adders use one of the same carry look-ahead circuits to add 16 bits! 76 Diminished Radix Complement Subtraction of numbers requires a different algorithm from that for addition Adding the complement of a number is equivalent to subtraction We will discuss two complements: Given a number N in Base r having n digits, the (r – 1)’s-complement (called the Diminished Radix Complement) is defined as: (rn – 1) – N Example: – For r = 10, N = 123410, n = 4 (4 digits),we have: (rn – 1) = 10,000 – 1 = 999910 – The 9's complement of 123410 is then: – Diminished Radix Complement – Radix Complement 999910 - 123410 = 876510 Subtraction will be done by adding the complement of the subtrahend 77 78 13 Binary 1's Complement Radix Complement For r = 2, N = 011100112, n = 8 (8 digits): (rn – 1) = 256 -1 = 25510 or 111111112 The 1's complement of 011100112 is then: 11111111 – 01110011 10001100 Since the 2n – 1 factor consists of all 1's and since 1 – 0 = 1 and 1 – 1 = 0, the one's complement is obtained by complementing each individual bit (bitwise NOT). Given a number N in Base r having n digits, the r's complement (called the radix complement) is defined as: – rn –N for N ≠ 0 and – 0 for N = 0 The radix complement is obtained by adding 1 to the diminished radix complement Example: –For r = 10, N = 123410, n = 4 (4 digits), we have: rn = 10,00010 –The 10's complement of 1234 is then 10,000 - 1234 = 876610 or 8765 + 1 (9's complement plus 1) 79 Binary 2's Complement 80 Alternate 2’s Complement For r = 2, N = 011100112, n = 8 (8 digits), we have: (rn ) = 25610 or 1000000002 The 2's complement of 01110011 is then: 100000000 – 01110011 10001101 Note the result is the 1's complement plus 1 Given: an n-bit binary number, beginning at the right and proceeding left: – Copy all least significant 0’s – Copy the first 1 – Complement all bits thereafter. 2’s Complement Example: 10010100 – Copy underlined bits: 100 – and complement bits to the left: 01101100 81 82 Unsigned 10’s Complement Subtraction Example 1 Subtraction with Radix Complements For n-digit, unsigned numbers M and N, find M − N in base r: – Add the r's complement of the subtrahend N to the minuend M: M + (rn − N) = M − N + rn – If M > N, the sum produces end carry rn which is discarded; from above, M − N remains. – If M < N, the sum does not produce an end carry and, from above, is equal to rn − ( N − M ), the r's complement of ( N − M ). – To obtain the result − (N – M) , take the r's complement of the sum and place a − in front. 83 Find 54310 – 12310 543 – 123 543 + 877 10’s comp 420 The carry of 1 indicates that no correction of the result is required. 1 84 14 Unsigned 10’s Complement Subtraction Example 2 Unsigned 2’s Complement Subtraction Example 1 Find 12310 – 54310 123 – 543 Find 010101002 – 010000112 0 123 + 457 580 10’s comp 520 The carry of 0 indicates that a correction of the result is required. Result = – (520) 10’s comp 01010100 01010100 1 – 01000011 2’s comp + 10111101 00010001 The carry of 1 indicates that no correction of the result is required. 85 Unsigned 2’s Complement Subtraction Example 2 Subtraction with Diminished Radix Complement Find 010000112 – 010101002 01000011 – 01010100 86 For n-digit, unsigned numbers M and N, find M − N in base r: 01000011 + 10101100 2’s comp 11101111 2’s comp 00010001 The carry of 0 indicates that a correction of the result is required. Result = – (00010001) 0 – Add the (r − 1)'s complement of the subtrahend N to the minuend M: M + (rn − 1 − N) = M − N + rn − 1 – If M > N, the result is excess by rn − 1. The end carry rn when discarded removes rn, leaving a result short by 1. To fix this shortage, whenever and end carry occurs we all 1 in the LSB position. This is called end-around carry. – If M < N, the sum does not produce an end carry and, from above, is equal to rn − 1 − ( N − M ), the r − 1 's complement of ( N − M ). – To obtain the result − (N – M) , take the r − 1 's complement of the sum and place a − in front. 87 Unsigned 1’s Complement Subtraction Example 1 88 Unsigned 1’s Complement Subtraction Example 2 Find 010101002 – 010000112 Find 010000112 – 010101002 01010100 1 01010100 – 01000011 1’s comp+ 10111100 00010000 +1 00010001 The end-around carry occurs. 01000011 01000011 0 – 01010100 1’s comp+ 10101011 111011101’s comp 00010001 The carry of 0 indicates that a correction of the result is required. Result = – (00010001) 89 90 15 Signed Integers Signed Integer Representations Positive numbers and zero can be represented by unsigned n-digit, radix r numbers. We need a representation for negative numbers. To represent a sign (+ or –) we need exactly one more bit of information (1 binary digit gives 21 = 2 elements which is exactly what is needed). Since computers use binary numbers, by convention, (and, for convenience), the most significant bit is interpreted as a sign bit: Signed-Magnitude – here the n – 1 digits are interpreted as a positive magnitude. Signed-Complement – here the digits are interpreted as the rest of the complement of the number. There are two possibilities here: Signed One's Complement – s an–2 … a2a1a0 – Uses 1's Complement Arithmetic where: Signed Two's Complement – s = 0 for Positive numbers s = 1 for Negative numbers – Use 2's Complement Arithmetic and ai = 0 or 1 represent in some form the magnitude. 91 Signed Integer Representation Example Signed-Magnitude Arithmetic Addition: r =2, n=3 Number +3 +2 +1 +0 –0 –1 –2 –3 –4 92 Sign -Mag. 011 010 001 000 100 101 110 111 — 1's Comp. 011 010 001 000 111 110 101 100 — – If signs are the same: 1. Add the magnitudes. 2. Check for overflow (a carry into the sign bit). 3. The sign of the result is the same. – If the signs differ: 1. Subtract the subtrahend from the minuend 2. If a borrow occurs, take the two’s complement of result and make the sign the complement of the sign of the minuend. 3. Overflow will never occur. 2's Comp. 011 010 001 000 — 111 110 101 100 Subtraction: – Complement the sign bit of the number you are subtracting and follow the rules for addition. 93 Sign-Magnitude Examples 94 Signed-Complement Arithmetic Addition: 1. Add the numbers including the sign bits, discarding a carry out of the sign bits (2's Complement), or using an end-around carry (1's Complement). 2. If the sign bits were the same for both numbers and the sign of the result is different, an overflow has occurred. 3. The sign of the result is computed in step 1. Subtraction: Form the complement of the number you are subtracting and follow the rules for addition. 95 96 16 Signed 2’s Complement Examples Signed 1’s Complement Examples 97 98 2’s Complement Adder/Subtractor Overflow Detection Subtraction can be accomplished by addition of the Two's Complement. 1. Complement each bit (One's Comp.) 2. Add one to the result. The following circuit computes A - B: When the Carry-In is 1, the 2’s comp of B A(1) A(2) is formed using XORs A(3) B(1) B(3) B(2) to form the 1’s comp and adding the 1 on C(0). C(4) x Co y FA Ci C(3) x Co S S(3) y FA Ci C(2) x Co S S(2) y FA Ci C(1) A(0) B(0) x Co S S(1) C(0) y FA Ci S S(0) 99 100 Review of Decimal Multiplication Binary Multiplication The binary digit multiplication table is trivial: (a × b) b=0 b =1 a=0 0 0 a=1 0 1 Perform base 10 multiplication by: – Computing partial products, and – Justifying and summing the partial products. To compute partial products: This is simply the Boolean AND function. Form larger products the same way we form larger products in base 10. – Multiply the row of multiplicand digits by each multiplier digit, one at a time. Partial product formation here require carries to be added – more complex than binary 101 102 17 Example: (237 x 149) Base 10 Partial products are: 237 × 9, 237 × 4, and 237 × 1 2 3 Note that the partial product × summation for n digit, base 10 1 4 numbers requires adding up 2 1 3 9 4 8 to n digits (with carries). + 2 3 7 Note also n x m digit multiply generates up 3 5 3 1 to an m+n digit result. Binary Multiplication Algorithm We compute base 2 multiplication by: 7 9 3 3 103 – Computing partial products, and – Justifying and summing the partial products. (same as decimal!) To compute partial products: – Multiply the row of multiplicand digits by each multiplier digit, one at a time. – With binary numbers, partial products are very simple! They are either: • all zero (if the multiplier digit is zero), or • the same as the multiplicand (if the multiplier digit is one). Note: No carries are added in partial product formation! 104 Example: (101 x 011) Base 2 Partial products are: 101 x 0, 101 x 1, and 101 x 1 1 0 1 Note that the partial product × 0 1 1 summation for n digit, base 1 0 1 2 numbers requires adding up to n digits (with carries) 1 0 1 in a column. 0 0 0 Note also n x m digit 0 0 1 1 1 1 multiply generates up to an m + n digit result (same as decimal). 105 18